一种基于LabVIEW FPGA 的运载火箭数字量接口测试方法

黄 皓,刘 靓

(北京宇航系统工程研究所,北京 100076)

在传统方式下,运载火箭遥测系统综合试验中外系统接口功能测试是使用模拟量、指令、数字量单机测试台分别模拟相应控制系统信号,而该传统方法中数字量测试台中一般使用定制FPGA 板卡来实现脉冲量、计算机字等数字量信号,但存在以下几点不足:

(1)每个型号的数字量测试板卡软硬件都使用定制开发方式,会造成相似种类设备重复设计生产,不利于状态升级迭代和举一反三。

(2)无论代码更新或型号移植,需要数字量板卡重新烧录底层FPGA 逻辑代码,而板卡多为定制板卡,需要拆卸取出单板,进行单板加电烧写程序后再联调,无法灵活便捷实现测试设备资源调试和复用。

(3)硬件底层编程和与上位机软件在不同软件开发工具下编译开发,因此需要开发人员具备多种软件开发能力,编程人员调试开发时间和难度会增加。

FPGA 技术有很多优势,如可以自定义I/O 硬件时序逻辑、拥有较强的数字信号处理能力等,但因为配置FPGA 需要VHDL 编程的专业知识或复杂的设计工具,而这些工作通常又是由硬件设计工程师,而非测试和控制工程师所完成的,所以系统的终端用户往往不愿开发自己的基于FPGA 的系统,只能通过定制设计的硬件才能够完成创建复杂精密的测量和控制系统[1]。

为解决传统测试方式的不足,本文设计了一种研制基于通用PXI 总线模块的外系统接口等效器用于接口功能测试,采用PXI DA 板卡作为模拟量信号源,PXI 继电器开关板卡作为指令信号源,而数字量信号采用NI FPGA 可编程逻辑板卡模拟数字量时序逻辑。尽管不同型号的数字量信号逻辑协议和数据位数可能存在不一致,但可以将相同硬件部分复用,硬件程序部分使用上位机软件LabVIEW FPGA 模块灵活编译下载,无需硬件连线来烧写新程序,从而实现不同型号之间的灵活通用方式,并且接口通讯协议的更新可通过LabVIEW 在线编程编译后升级底层逻辑关系,该方法适用于外系统接口测试同时兼容多型号不同时序传输协议[2]。

1 信号分析及设备系统架构

1.1 数字量信号模拟要求

以陀螺脉冲参数性质为例,接口电路如图1 所示,输出脉冲的数字信号电平参数要求如下:

图1 陀螺脉冲测试接口Fig.1 Gyro pulse testing interface

(1)幅度:0~5 V;

(2)脉冲宽度:1 μs~4 ms 内,由FPGA 设置;

(3)频率:小于等于500 kHz,由FPGA 设置。

而计算机字协议为在接收到中断请求脉冲后,在要求时间内向遥测系统传输完一个遥测字,如图2 所示。因此等效器设计时需要在硬件和软件协议上满足接口要求,从而实现对数字量参数的信号模拟。

图2 计算机系统测试接口时序Fig.2 Timing of computer system test interface

1.2 设备系统架构和组成

外系统接口等效器中激励信号模块的设计架构要求基于PXI 仪器组合与信号调理组合的方式,其中数字量信号模拟源采用NI PXI-7841R 数字板卡编程模块来实现数字逻辑协议,它提供的可编程FPGA芯片,适合板载处理和灵活的I/O操作。本文使用的是PXIe-7854R 下的FPGA 板卡,型号为Xilinx Virtex-5 LX110,它由64 个乘法器,69120 个触发器,69120 个查找表和4608 Kb Block RAM 构成。它硬件部分是一种具有可重复配置逻辑门的芯片,在程序设计和实现上具有很强的灵活性,它可根据不同的需要而进行配置和修改。同时,它还具有精确时序和同步、快速决策及并行任务同时执行等优点,其主要指标如下:

(1)8 路模拟输入,200 kHz 独立采样率,16 位分辨率,±10 V;

(2)8 路模拟输出,1 MHz 独立更新率,16 位分辨率,±10 V;

(3)96 条数字线,可配置为速率高达40 MHz 的输入、输出、计时器或自定义逻辑;

(4)Virtex-5 LX50 FPGA,可通过LabVIEW FPGA 模块对其编程;

(5)3 路直接存储器访问(DMA)通道,用于高速硬盘数据读写。

外系统接口等效器的调理组合和适配器完成硬件接口的转换,输出数字脉冲信号具体实现接口电路如图3 所示。

图3 数字信号输出调理接口电路Fig.3 Interface circuit of digital signal output conditioning

2 软件设计

外系统等效器采用LabVIEW 界面开发工具实现程序界面和底层逻辑编写。其中界面开发使用LabVIEW 面板设计,而测试逻辑采用LabVIEW 实现状态机方式,采用ACCESS 数据库形式管理流程配置信息、硬件映射关系和测试结果,软件读取装载流程配置文件,可解析出流程配置信息,并通过硬件映射关系转换为底层板卡执行指令,最终将测试结果保存进结果数据库。

其中FPGA 的程序属于板卡测试逻辑的特殊部分,由于FPGA 为内部逻辑可编辑的硬件,由Lab-VIEW FPGA 编译工具实现,编译后的程序可在线下载到FPGA 板卡,由上位机流程调用并执行。

2.1 FPGA 开发流程

LabVIEW 是一种用图表代替文本创建应用程序的图形化编程语言,LabVIEW FPGA 是LabVIEW的一个子模块,用户可借助NI LabVIEW 图形化程序框图和NI LabVIEW FPGA 模块,配置各项数字量专用通信协议。

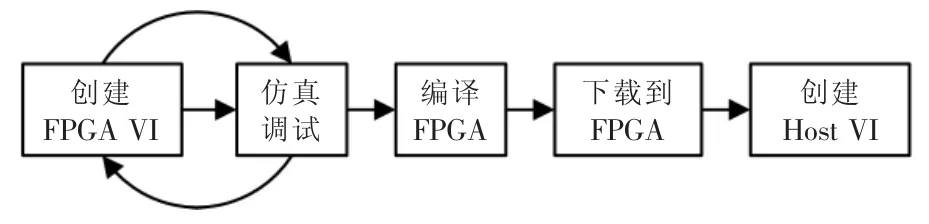

通过对LabVIEW FPGA 图形化的编程开发可以快速地开发实现数字量信号的模拟系统,同时也使工程设计人员无须了解或其他的硬件开发工具即可开发系统,使用开发应用程序的典型流程如图4 所示[3]。

图4 LabVIEW 开发FPGA 流程Fig.4 Developing FPGA flow chart with LabVIEW

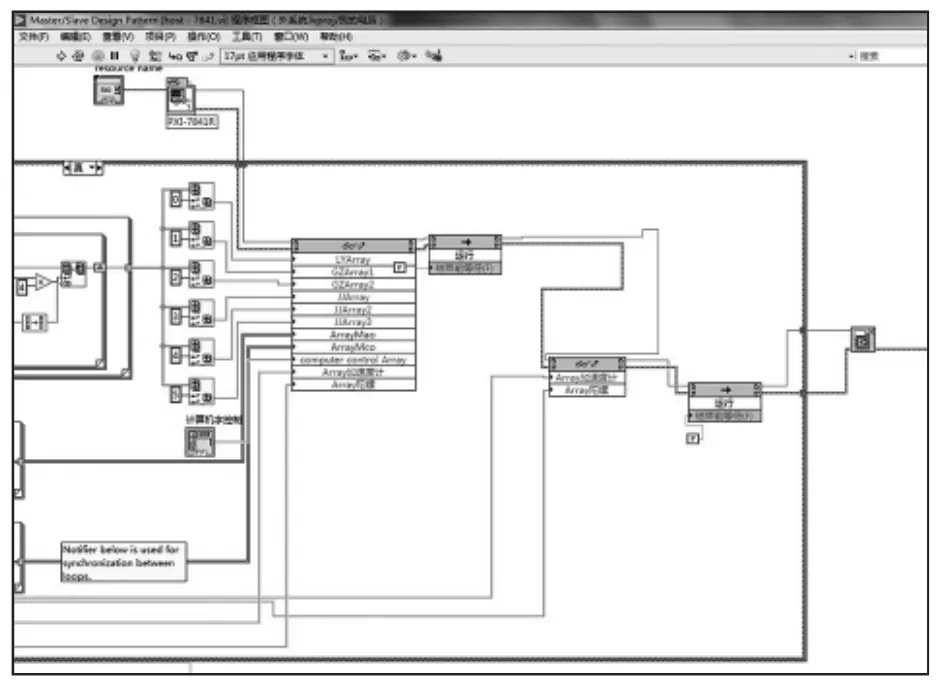

首先创建FPGA VI,使用LabVIEW FPGA 软件在主控计算机上运行程序,反复地进行调试、修改,直至程序逻辑正确无误、满足设计要求。然后编译FPGA VI,并把程序下载到FPGA 板卡。在上述FPGA程序完成后,在主控计算机上创建用户界面程序Host VI,使用Host VI 通过FPGA 输入输出接口来调用FPGA VI,最终就完成了整个系统的设计,如图5 所示。

图5 顶层Host 调用FPGA 程序Fig.5 Top Host program of calling FPGA

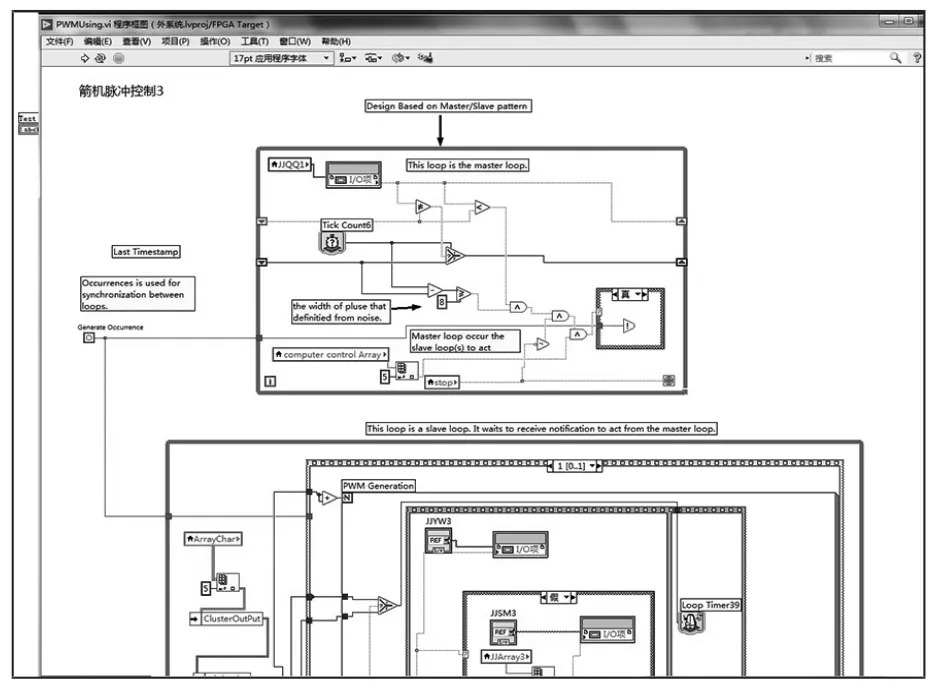

FPGA 程序根据协议编写数字量的脉冲数和计算机字的操作,并预留对Host VI 的接口参数,比如脉冲数的个数、脉冲宽度、计算机字的十六进制内容等。其中以计算机字为例,测量系统的发送请求建立中断响应,当监测到发送信号请求时,开始根据协议输出移位信号和计算机字。在这个中断响应中,需要LabVIEW FPGA 建立一个中断,其中一个循环框图为设定中断的条件,即当条件满足时中断产生。另外一循环框图为中断执行内容,当产生中断后,将执行循环框图中的内容。如图6 所示,上框图循环监测请求脉宽信号是否达到要求,当为正常请求脉冲时将产生中断,中断产生后执行下框图中的发送移位和计算机字信号。

图6 FPGA VI 中断响应程序Fig.6 FPGA VI interrupt response program

2.2 用户层设计

程序设计中多事件之间的逻辑关系必须正确,否则程序可能陷入死循环等错误,从而造成测试系统死机。自动流程执行在此类问题处理的是否得当决定了程序运行的效率和可靠性。

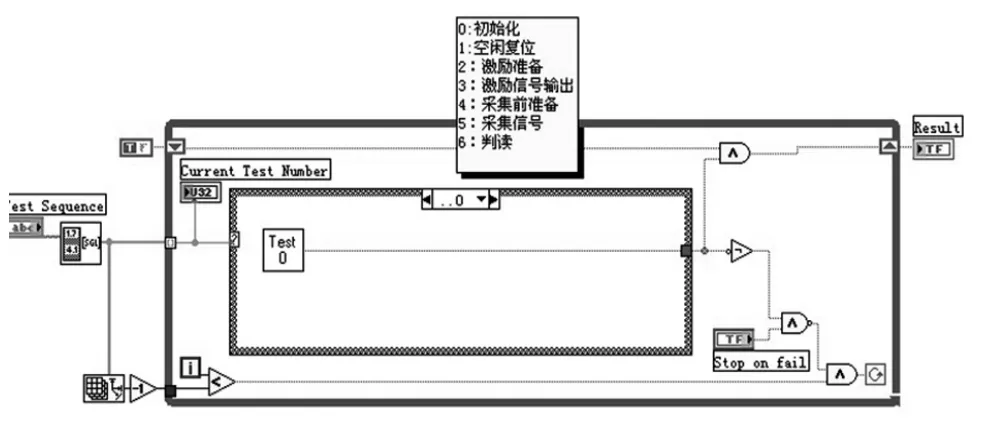

状态机不仅可以使程序中多事件之间的逻辑关系更简洁明了,同时它强大的错误处理能力、用户选择测试、条件执行等功能使多事件间的逻辑关系处理变得更为简单。一般可以用状态图来对一个状态机精确地描述。LabVIEW 状态机由一个While主循环和一个case 结构组成,并利用位寄存器来实现状态的跳转。While 循环保证状态机的连续运行,case 结构的分支与状态一一对应,即case 结构的分支名称对应着状态名称,分支里执行代码的功能对应着状态的行为,而case 结构的条件变量与系统事件相对应,引发状态的变迁及决定状态迁移的方向。状态机的While Loop+Case 结构+位移寄存器的框架使得程序的结构更为清晰,再次修改也甚为方便[4]。

在LabVIEW 状态机程序编写设计时需要注意编程习惯,如图7 所示,一般完成以下方面:

图7 状态机程序图Fig.7 State machine program diagram

(1)状态用于区分不同状态,可以使用数字对应相应状态。

(2)一般应该有:初始化、空闲、信号准备、信号输出、信号采集、判读、停止状态。本程序所需执行状态为7 个状态,结束为程序退出循环。

(3)“初始化”进行一些初始化的操作;“空闲”是一种过渡状态,用于和用户打交道的状态;“准备”为激励信号输出前的准备操作,比如数字量设置等等;“信号输出”为数字量、D/A、指令等激励信号的输出控制;“信号采集”为信号采集;“判读”为对单步测试结果的判读,并决定下一步跳转状态。

(4)状态始终贯穿整个应用程序,并由移位寄存器进行状态值的寄存和传递。当前状态分支的结果将决定下一个状态。

3 实验结果及分析

LabVIEW FPGA 程序编译下载到NI PXI-7841R后,使用Host VI 设置计算机字调试检查等效器发送的信号,等效器设定发送0xD5D5 计算机字的示波器信号监测图,如图8 所示,从示波器信号看出LabVIEW FPGA 程序逻辑与设计要求一致。

图8 计算机字数字信号图Fig.8 Diagram of digital signal computer word

测试界面如图9 所示,选择测试流程,点击“自动执行”,即自动执行测试流程,测试流程每步测试会自动显示返回值,并且比对返回值与设定合格条件,显示每项判读结果是“合格”或“不合格”。若由流程中任意一步测试结果不合格,则总结果判定为不合格,且“测试状态”灯由绿变红。例如等效器模拟源发送计算机字为0x2345678AB,若遥测采集计算机字的值为0x2345678AB,则判读结果为合格。

图9 外系统等效器测试图Fig.9 External system equivalent test diagram

4 结语

利用LabVIEW FPGA 模块可在线编程的功能可实现控制系统的数字量信号模拟的灵活配置,本文使用PXI7841R 卡和LabVIEW 图形化编程方式,通过上位机在线下载和编译FPGA 逻辑,完成脉冲量和计算机字等数字量信号模拟,实现调用不同程序适配不同型号要求,达到了数字量信号时序逻辑的软件自定义的目的,最终大幅度提高了设备的设计周期和成本。经实验验证,系统运行良好,本设计方法开发周期短、可靠性高、功能扩展性强。