一种新型的基于FPGA数字秒表的设计方法

车保川

摘要:本文介绍了一种新型的基于FPGA的数字秒表的设计与实现方法,给出了顶层电路图,和各模块的设计,增加了消除抖动的控制方法,消除了开关按键的机械抖动。通过编辑、编译和器件编程,用MODELSIM仿真软件进行了仿真,并将编程器文件下载到ISP实验板TB-BD-TS101开发板中,经实际电路测试验证,达到了预期的设计要求,显示结果准确无误。

关键词:FPGA;数字秒表;模块;开关按键

中图分类号:TN702 文献标识码:A

1前言

当今社会是数字化的社会,是数字集成电路广泛应用的社会。数字集成电路本身在不断更新换代,随着电子技术的发展,设计人员更希望设计周期尽可能短,最好能在实验室、调试现场完成对逻辑块和连线的配置,并且立即投入实际应用之中,因而出现了现场可编程逻辑门阵列FPGA。

本文介绍了如何利用FPGA设计与实现数字秒表的全过程,利用了超高速硬件描述语言VHDL的EDA设计工具,采用的是Xinlinx 的低成本系列中的Spartan-3,型号为XC3S400-4PQ208C的芯片来实现系统功能,采用分模块化思想编程,开关按键集计数、停止、清零与一体,节省资源,思路简单,容易实现。

2秒表的功能要求

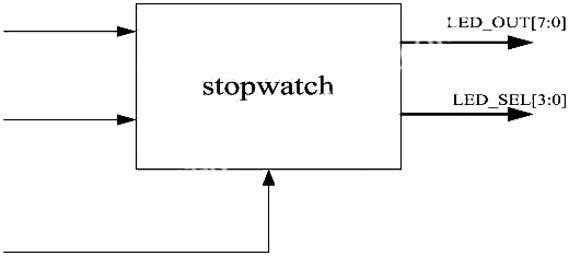

设计一个秒表stopwatch要求具有以下功能:有一个复位reset端子SW10,reset低电平有效;一个开关起、停、清零start/stop/clear端子SW7,系统启动后,第一次按SW7,秒表开始计数,第二次按SW7,秒表停止计数,第三次按SW7秒表清零。其顶层模块如图1 所示。

板子的主频时钟我们用32MHZ,秒表动态的显示在TS101板子的D5,D6,D7,D8 LED上,D5,D6表示分钟位,D7,D8表示秒钟,D6的小数点亮,表示分钟和秒钟的分隔。

3系统的模块设计

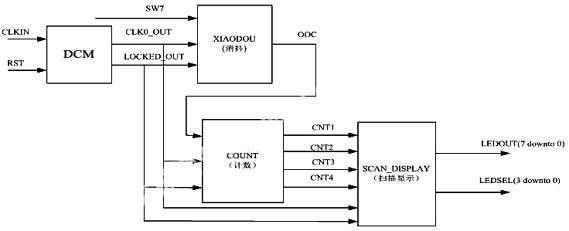

图2所示是数字秒表设计的顶层模块图,其中CLKIN是32MHz系统时钟,RST是复位信号,可以对整个系统清零。

该模块图主要分为四个部分,第一部分是DCM(Digital Clock Manager)调用模块。通过DCM的应用,可以去除时钟歪斜、频率综合与相位调整。

第二部分是消抖模块,因为开关按键为机械弹性开关,由于机械触点的弹性作用,一个按键开关在按下的瞬间会有一连串的抖动,抖动的长短由机械特性所决定,一般为5~15ms,抖动引起电平信号波动,从而引起误处理。为了确保一次按键动作只确认一次按键,必须消除抖动。

第三部分是计数模块,计数模块内部包括一个状态控制进程,控制开关的三个不同状态;一个分频进程,主要是把系统32MHz的时钟分频为1Hz:两个6进制计数器,和两个十进制计数器,这样可以比直接使用60进制计数器节省资源,直接利用秒的个位(十制)的进位信号作为秒的十位的进位信号,秒的十位(6进制)的进位信号作为分得个位的进位信号,依此类推。部分计数程序如下:

……

---------CNT4---------秒的个位计数(10进制计数器)

process(CLK0_OUT,LOCKED_OUT)--系统复位

begin

if(LOCKED_OUT = '0') then

r_ct4 <="0000";

elsif(CLK0_OUT = '1' and CLK0_OUT'event) then

if(r_outp = "00") then --清零

r_ct4 <= "0000";

elsif(r_outp = "10")then --停止计数

r_ct4 <= r_ct4;

elsif(r_outp = "01")then --开始计数

if(r_ci3 = '1') then

if(r_ct4 = "1001") then

r_ct4 <= "0000";

else

r_ct4 <= r_ct4 + '1';

end if;

end if;

end if;

end if;

end process;

r_ci4<= '1' when ((r_ct4 = "1001") and

(r_ct3 = "11110") and

(r_ct2 = "1111100110") and

(r_ct1 = "1111100110")) else

'0';--r_ci4<='1'为 进位信号

CNT1 <= r_ct4;

----------------------------------------

……

第四部分是扫描显示部分,计数器输出的四个四位信号,分别是秒针个位、十位、分针、个位、十位。通过译码显示程序,对应四个LED数码管。另外还有一片选信号,选出不同的要显示的数据,为了实现动态显示,还要控制扫描频率 ,可以通过一分频器实现,经实验得动态显示频率控制在200Hz左右可等到比较好得效果。部分译码程序如下:

……

process(s_data) begin

case s_data is

when "0000" =>s_ledout(7 downto 1) <="0111111";

when "0001" =>s_ledout(7 downto 1) <="0000110";

when "0010" =>s_ledout(7 downto 1) <="1011011";

when "0011" =>s_ledout(7 downto 1) <="1001111";

when "0100" =>s_ledout(7 downto 1) <="1100110";

when "0101" =>s_ledout(7 downto 1) <="1101101";

when "0110" =>s_ledout(7 downto 1) <="1111101";

when "0111" =>s_ledout(7 downto 1) <="0100111";

when "1000" =>s_ledout(7 downto 1) <="1111111";

when "1001" =>s_ledout(7 downto 1) <="1101111";

when others=> s_ledout(7 downto 1) <="XXXXXXX";

end case;

end process;

process(s_ledsel) begin

if (s_ledsel="1011")then --控制小数点点亮

s_ledout(0) <= '1' ;

else

s_ledout(0) <= '0' ;

end if;

end process;

……

4 设计仿真与下载验证

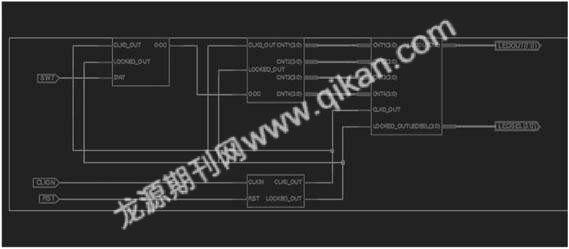

上面数字秒表得模块图,采用VHDL语言编写程序,把各程序经过编译后,生成模块,通过建立顶层文件,调用这些模块,完成电路得连接。通过ISE综合可得到完整得电路模块图。如图3所示:

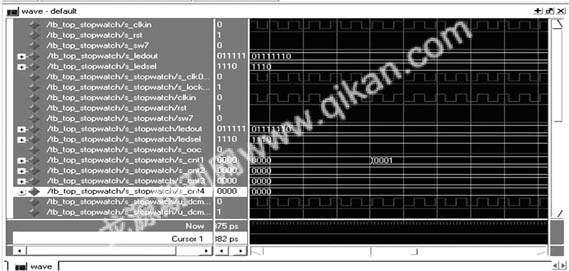

再通过Modelsim 软件进行编译、仿真,得到仿真图形如图4所示:

由仿真结果可知数字秒表实现了准确的计数功能。

最后将该设计下载到实验、开发系统中进行验证。经ISE综合后生成相应的stopwatch.ucf文件,管脚锁定如下:输入信号CLKIN对应P76引脚,RST对应P120引脚, SW7对应P116引脚;输出信号LEDOUT[7:4]对应P37~P34引脚,LEDOUT<3>对应P31, LEDOUT<2>对应P29, LEDOUT<1>对应P28, LEDOUT<0>对应P33, LEDSEL<3>对应P39,LEDSEL<2>对应P40,LEDSEL<1>对应P42,LEDSEL<0>对应P43。管脚锁定后再进行编译,生成可下载的stopwatch.mcs文件,将该文件下载到TS101芯片中,可实际验证该设计的各种功能,复位、计数、暂停、清零等。

5 结束语

通过利用FPGA设计数字秒表可,进一步熟悉了FPGA的整套开发流程,即设计入口,仿真,综合,布局布线。在Xinlinx FPGA 开发环境下,采用至上而下的设计方法有利于早期发现结构设计中的错误,避免不必要的重复设计。在结合基于FPGA的“在系统”可编程实验板,轻轻松松就能实现电子产品的设计,现场观察实

验测试结果。大大缩短了产品的设计周期和调试周期,提高了设计的可靠性和成功率。充分体现了可编程逻辑器件在数字电路设计中的优越性。

参考文献:

[1]王振红.VHDL数字电路设计与应用实践教程[M],北京:机械工业出版社,2003(6).

[2]张淑骅.基于FPGA的数字秒表的VHDL设计[J],大众科技,2006(5):7-78.

[3]詹小杏,林浩泉.用CPLD器件设计数字秒表[J],大众科技,2004(10):2.

[4]韩芝侠.基于FPGA的数字秒表设计 [J],陕西工学院学报,2004,20(4):22-23.

[5]陈耀和.VHDL语言设计技术[M],北京:电子工业出版社,2004(3).

[6]翟殿棠,田万民,厉光伟.VHDL在数字设计中的应用研究[J],信息技术研究与应用,2004(3):44-45.