PXI-E总线与TMS320C6416 HPI口的桥接设计

王金戈,秦开宇,阎啸

(电子科技大学 空天科学技术研究院 成都 610054)

0 引言

模块化仪器总线技术,从上世纪60年代推出的GPIB总线,到如今已广泛使用的VXI和PXI总线技术,随着桌面PC的PCI总线发展到PCI-EXPRESS总线,PXI标准也随之发展,PXI Express总线就此应运而生。2005年,PXISA官方组织正式推出的PXI Express的软硬件标准。通过在背板使用PCI Express技术,将传输带宽大大提升,同时保持了和原来PXI模块在软硬件上的兼容性。如此性能的提升,使得PXI Express能够进入到更多以往被专用仪器所统制的一些应用领域,如中频乃至射频的数字化仪、每秒高达几百帧的图像采集与存储、上GHz的数字化仪和信号发生器,数字通讯协议的测试与验证等等。本文的设计背景是基于PXIE总线的频谱分析仪,PXI-E接口采用PEX8311芯片实现,在实际应用中由于需要将DSP作FFT和解调运算处理之后的数据传输至上位机软件显示,上位机软件也会经常向DSP下发命令、程序或数据,于是使用在8311本地总线和DSP的HPI口间用FPGA进行了桥接设计,实现了上位机软件对DSP的高速读写和程序加载。

1 PXI-EXPRESS总线接口实现

由于PXI-E总线是在PCI-E协议的基础上,仅仅多了自动测量仪器所特有的星型触发总线、链状总线和一些硬件结构规范。因此,实现PCI-E总线的方法即可适用于PXI-E总线。目前供选择的方案主要有两种:带有物理层收发模块和PXI-E协议的FPGA实现;桥接芯片方案。

(1)FPGA实 现:如 今,XILINX公 司 的virtex-5或者spartan-6系列的FPGA集成了高速串行收发器GTP,可以实现PCI-E物理层的串行收发,并且在购买PCI-E的IP核后可以完全以单片FPGA实现PCIE协议。

(2)桥接方案:PLX公司的PEX8311芯片可以实现PCI-EXPRESS到本地总线(Loccal Bus)的桥接,桥接后的逻辑也相对简单。并且比起购买XILINX的昂贵IP核来说,是一个低成本的方案。但桥接芯片只能实现一个通道,无法完全发挥出PXIE高带宽的优势。

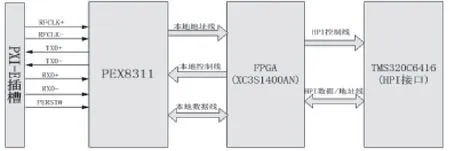

鉴于第二种方案设计成本和难度较低,本文采用了利用PEX8311的桥接方案。图1给出了硬件实现结构。

图1 接口硬件结构

PEX8311是PLX公司一款高性能的PCI-E桥接芯片,用来实现PCI-E总线到本地总线的转换,可以单次读写、连续读写或者DMA操作(见图2)。XC3S1400AN 是XILINX公司的低端FPGA芯片,完成本地总线与HPI总线的桥接。

图2 PEX8311本地总线DMA写操作

2 HPI接口

TMS320C 6416的HPI 口是一种数据宽度为32bit 的并行端口。通过HPI口,主机可以直接对CPU 的存储器空间进行操作。HPI 口内部有3个寄存器,分别是控制寄存器( HPIC) ,地址寄存器(HPIA) 和数据寄存器( HPID) 。这3个寄存器可以直接被主机访问,主机每执行一次对CPU 内部存储空间的访问都必须先对控制寄存器和地址寄存器写入相应的值,然后才能对数据寄存器进行读写操作。HPI 口的外部接口是由数据总线HD[ 31 :0]以及一部分用于描述和控制HPI 接口的控制信号组成,主要的控制信号线有: HCNTL[1:0]:控制HPI 的操作类型;HR/ W:读/ 写选择;HRDY:就绪状态标志;HINT:中断标志,DSP 向主机提出中断;HDS1 ,HDS2 ,HCS:数据选通输入,三者配合可用于产生一个HPI 内部选通信号HSTROBE:HSTROBE = [NOT(HDS1 XOR HDS2) ]OR HCS;

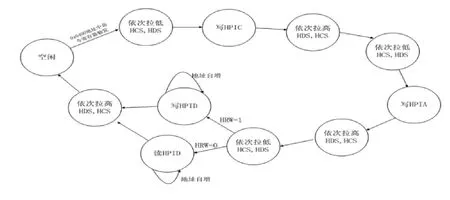

对于一个读写HPI 口的操作,应首先使能HCS ,变化HDS1 或HDS2 ,可使HSTROBE 信号产生一个下降沿,HPI 口在这个下降沿采样控制信号HCNTL[1:0]和HR/ W,同时在使能HCS 的同时扇出HRDY,以使主机进入等待状态,直到HRDY产生下降沿,表明HPID 已清空,可以接收新的数据。此时HSTROBE 也将产生一个上升沿,并采样HD[ 31 : 0]上的数据并将其送入HPID。读时序如图3所示。

图3 读HPI口时序图

对于通过HPI接口向TMS320C6416加载程序的具体过程如下:①设置Boot mode为HPI方式;② 复位DSP;③将DSP程序编译生成的.out文件转换成所需要的文件代码,加载至DSP对应的存储空间;④加载完成后主机向HPIC寄存器的DSPINT位写1,而后DSP便开始执行程序。

3 桥接程序设计

桥接程序主要由FPGA的Verilog代码配合上层软件来完成,本文给出了FPGA程序的设计方案和上位机软件的大致操作流程。

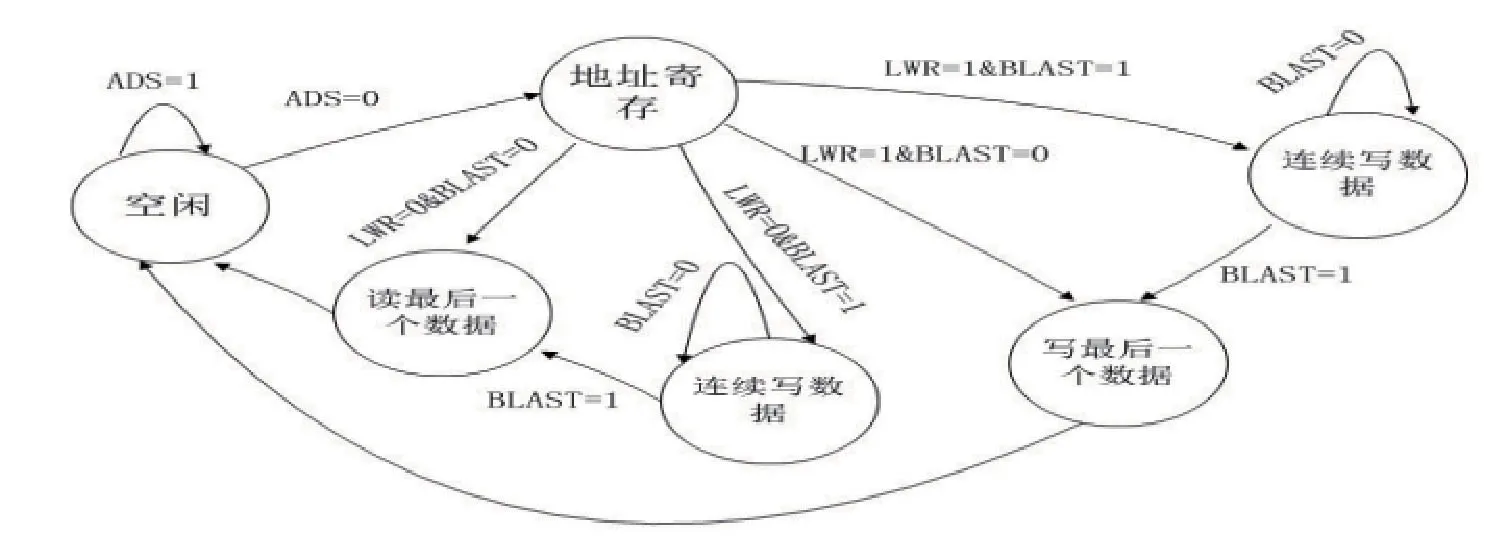

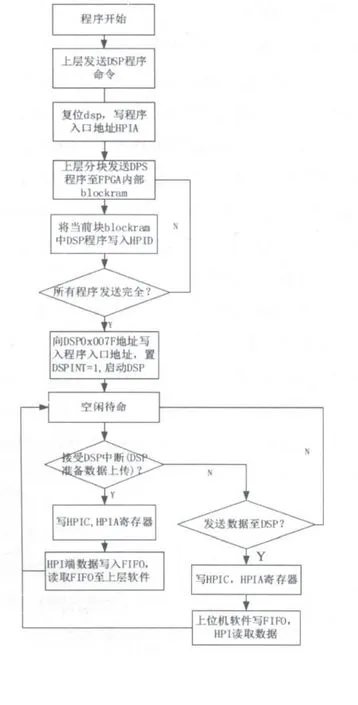

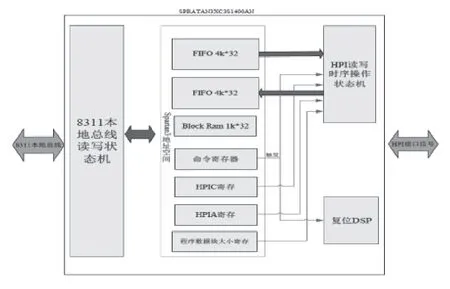

FPGA中设计了两个主要的状态机,一个是负责操作8311本地总线的读写时序状态机(图4),包括连续读写和单次读写;另一个负责操作DSP的HPI口的读写时序状态机(图5),也包括单次读写和地址自增读写。上位机软件具有3个不同功能的操作(流程图见图6),流程中的数据读写都是基于这两个状态机的调用。其中,上位机软件操作完成的第一个功能是分块发送DSP程序至FPGA内部block ram,由FPGA将其转发至DSP内部的程序空间,而后FPGA复位DSP,实现上层软件加载DSP程序。第二个功能是上层软件收到HPI中断后,FPGA接受HPI接口的数据,将其写入FPGA内部的FIFO,通过调用8311本地总线读状态机从而完成上层软件对DSP的读操作。第三个操作是在FPGA接受上层软件下发的数据,经8311本地总线将数据写入FPGA内部的FIFO,再调用HPI写状态机将FIFO数据写入HPI口,从而完成上层对DSP的写操作。整个流程均会使用到这两个主状态机进行两端总线的读写操作,需要通过不同的上层命令和不同地质空间区分不同功能操作。

图4 PEX8311本地总线数据读写状态机

图5 HPI口读写状态机

图6 上位机软件操作流程图

因此,为区分不同的程序功能,在8311的本地总线的地址空间中,人为地做了划分。地址LA[31:2]=0x400定义为命令寄存器,每次的流程操作上次软件必须首先写命令寄存器,不同的命令值会通知FPGA触发不同的状态机操作,如两端总线的读写操作和DSP复位操作。地址0x401寄存接下来需要写入的HPIC的值,地址0x402寄存HPIA的值,地址0x403寄存接下来的操作需要连续读写DSP的数据块大小。地址ox404是上层写DSP的FIFO入口地址,0x405是上层读DSP的FIFO入口地址。0x0000 ~ 0x03ff留给配置DSP程序的1k的RAM空间,整个FPGA的程序架构见图7所示。

图7 FPGA程序架构图

4 测试结果

最终,加载了FFT计算程序的DSP将FFT计算数据经本文设计的桥接模块上传至上层软件所绘出的谱线截图见图8(其中FFT运算量为2048点,中心频率为30MHz,分析带宽为10MHz)。可见,设计出的桥接模块实现了DSP的程序加载运行,成功建立起了上位机软件经PXI-E总线对DSP的高速数据传输通道。

图8 上位机软件接收DSP的FFT计算数据所绘谱线图

5 结束语

本文使用了PEX8311芯片实现了PXI-E总线到8311本地总线的桥接,再使用FPGA桥接8311本地总线和DSP的HPI总线,设计的FPGA程序实现了上层软件对DSP的程序加载和高速读写的要求。随着各种自动测试仪器越来越多地对小型化和带宽提出更高的要求,基于PXI-E总线测试仪器必将越来越多地出现在军用和民用领域中。本设计提供的低成本的解决方案和总线桥接思路同样适用于其他的PXI-E测试仪器,经实际的项目结果所验证,能够以较低成本基本满足PXI-E测试仪器小型化,高带宽的要求。

[1]PXI Express Hardware Specification, PXI System Alliance, 2005.

[2]ExpressLane PEX8311AA PCI Express-to-Generic Local Bus Bridge Data Book, PLX Technology, Dec , 2009.

[3]PEX8311- PCI Express to Generic Local Bus Bridge, PLX Technology, 2005.

[4]TMS320C64x DSP Host Port Interface (HPI) Performance, Texas Instruments, Oct, 2003.

[5]TMS320C6416 FIXED-POINT DIGITAL SIGNAL PROCESSORS, Texas Instruments, 2006.

[6]Implementing the TMS320C64X HPI Boot Process, Texas Instruments, 2004.

[7]Spartan-3AN FPGA Family Data Sheet, Xilinx, Feb, 2007.

[8]卞红雨.TMS320C6000系列DSP的CPU与外设[M].北京:清华大学出版社,2007.