正交调制器时序问题的分析与优化

彭继强,杨 豪,王旭亮

(中国电子科技集团公司第五十四研究所,河北石家庄050081)

0 引言

在工程应用中,数字正交调制器在采样速率较高时,容易发生调制数据时序问题,因此而导致IQ相位不平衡、相噪恶化等,并且在带有随机数据调制时不易被发现,严重影响数字正交调制器的调制效果。为了解决以上问题,引入固定输入信号、同相正弦输入信号和正交正弦输入信号3种特定信号分析解决问题。

AD公司的高性能数字正交上变频器AD9957作为调制器具有方便易用、频率灵活、IQ幅相一致性好的优点。然而,由于其数据接口是IQ支路时分复用的18位宽并行总线,当采样速率较高时,容易发生调制数据时序问题。在系统中,调制数据时序问题会导致IQ相位不平衡和相噪恶化等,严重时会导致调制数据错误。在带有随机数据调制时,数据错误容易被发现,但是由于调制后中频带宽较大,使因调制数据时序不佳导致的IQ相位不平衡和相噪恶化的问题不易被发现。

1 3种输入信号的分析

数字正交调制器通常由一对数字乘法器和一个数字加法器组成,其组成如图1所示。数字正交调制器的4个输入信号中,2个是数字载波信号,它们是一对正交的正弦和余弦波形,角频率都是 ωC(ωC=2πfC,fC是载波频率)。另2个是I和Q支路数字基带信号。调制输出Y(t)是基带信号上变频到载波频率(fC)后的调制信号。

图1 数字正交调制示意图

1.1 固定输入信号分析

假设固定输入信号输入载波信号频率为 ωC,I和Q输入信号不随时间变化,幅度系数为K(0≤K≤1)。则I和Q输入信号输入表达式为:

可得输出信号Y(t)的表达式:

式中,余弦函数的自变量只有输入载波信号频率ωC,说明输出信号Y(t)是一个与输入载波信号频率 ωC相同的单频信号。

1.2 同相正弦输入信号分析

假设同相正弦输入信号输入载波信号频率为ωC,I和Q输入信号为同一正弦波,幅度系数为K(0≤K≤1),角频率为 ωB。则 I和Q输入信号输入表达式为:

可得输出信号Y(t)的表达式为:

式中包括2个余弦函数,一个余弦函数有角频率项ωC+ωB,另一个有角频率项 ωC-ωB,说明输出信号Y(t)由2个信号组成,各自与载波频率fC偏移基带频率 fB。

1.3 正交正弦输入信号分析

假设正交正弦输入信号输入载波信号频率为ωC,I和Q输入信号由一对角频率为 ωB的正交信号组成,幅度系数为K(0≤K≤1)。则I和Q输入信号输入表达式为:

可得输出信号Y(t)的表达式为:

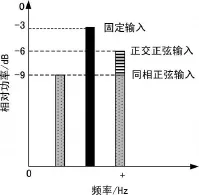

式中只有一个单一的余弦项,说明Y(t)只由一个单频信号组成,其角频率为载波角频率 ωC与基带角频率 ωB之和。如果将I和Q的输入信号交换,式(5)中角频率为载波角频率 ωC与基带角频率 ωB之差,其他并不改变。固定输入信号,同相正弦输入信号和正交正弦输入信号的频谱如图2所示。

图2 3种不同输入信号时的频谱

2 时序问题的实测与分析

在AD9957作为正交数据调制器工作时通过频谱仪对65.536 MHz和131.072 MHz两种采样速率时的调制输出进行实测。

当采样速率为65.536 MHz时,用频谱仪观察调制器输出,与理论上的推导结果相符,相位噪声优于-65 dB,输出正常。图3为在65.536MHz时的不同输入信号的频谱。正交正弦输入信号时,输出为图3(b)中的左半部分和右半部分。

图3 65.536 MHz时不同输入信号的频谱

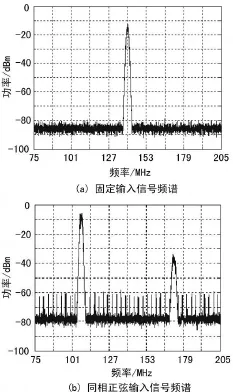

当采样速率为131.072 MHz时,用频谱仪观察调制器输出,出现IQ不平衡和相噪恶化问题,导致输出结果不正常。131.072 MHz时观察到的不同输入信号的频谱如图4所示。

图4 131.072 MHz时不同输入信号的频谱

从图4中可以观察到,固定输入信号的频谱,因数据不随时钟变化,输出正常;同相正弦输入信号以及角频率相加和相减时的正交正弦输入信号的频谱,有IQ相位不平衡和相噪恶化。正交正弦输入信号时,输出为图4(b)中的左半部分和右半部分。

对整个数据通路中的延时进行分析。用示波器观察,因PCB走线造成的相对延时不超过0.2 ns,低于示波器误差,可以忽略。对FPGA芯片中电路进行时序分析,寄存器到管脚延时,最大延时6.1 ns,最小延时0.4 ns,skew(数据偏斜,即相对延时)约6 ns;寄存器到寄存器延时,最大延时7 ns,最小延时1 ns,skew约6 ns。可见FPGA芯片内的传输延时造成18位数据之间skew较大,由于131.072MHz的采样速率对于6 ns(166.7MHz)的skew已达到临界,导致时钟采样点数据不稳定,造成了IQ相位不平衡和相噪恶化现象。

AD9957理论上可支持最高250 MHz的基带采样速率,在采样速率65.536 MHz时工作正常,但在采样速率为131.072 MHz时,由于采样速率基带数据时序问题导致AD9957的输出不正常,严重影响了数字正交调制器的效果,降低了其调制性能。

3 时序优化及性能实测

为了解决上述问题,对FPGA内部进行时序优化,使关键信号的扇入和扇出路径尽量短,减小绝对延时,优化并行数据的输出寄存器的位置,使寄存器到管脚延时一致,skew最小。经过时序分析可以观察到,最终输出的skew不超过0.02 ns。

通过以上的方法优化后,再按相同方法进行测试,当采样速率为131.072MHz时,用频谱仪观察调制器输出,与理论结果相符,输出正常,相位噪声优于-65 dB。再将采样速率提高到196.608 MHz,与理论结果相符,输出正常。

优化时序消除了调制器输出的IQ相位不平衡和相噪恶化问题后,实测了调制随机数据时的调制输出,基带数据采样速率196.608 MHz,中频带宽65.536 MHz,其频谱第二旁瓣外抑制优于-45 dB,带外抑制优于-60 dB。可见AD9957具有优异的调制性能。

4 结束语

在带有随机数据调制时,调制后中频带宽较大,使IQ不平衡和相噪恶化的问题不易被发现,通过引入固定输入、同相正弦输入和正交正弦输入3种信号对调制器输出进行测试,并对时序进行分析和优化,很好地解决了以上问题,提高了数字正交调制器的调制效果。以上方法也适用于AD9957以外的各种正交调制器的测试和优化。

[1]BUCHANANN.B,FUSCOV.HighPerfor-manceIQ Modulator-Based Phase Conjugator for Modular Retrodirective AntennaArray Implementation[J].IEEE Trans.On Commune,2009,57(5):2301-2306.

[2]CAVER J K,LIAO M W.AdaptiveCompen-sationfor Imbalance and Offset Losses in Direct Conversion Transceivers[J].IEEE Trans.On Commune,1993,42(4):581-588.

[3]NOE R.PhaseNoiseTolerant Synchronous QPSK/BPSK Basebandtype Intradyne Receiver Concept with Feedforward Carrier Recovery[J].J.Lightw.Technol,2005,23(2):802-808.

[4]宋广怡,彭继强.基于FPGA的QPSK高速解调器的设计与实现[J].无线电工程,2006,36(5):47-49.

[5]GARDNER F M.A BPSK/QPSK Timing Error Detector for Sampled Receivers[J].IEEE Trans.On Commune,1986,34(5):423-429.

[6]GARDNER F M.Interpolation in Digital Modems Part I:Fundamentals[J].IEEE Trans.on Commune,1993,41(3):501-507.