LDPC译码器的Impulse C编程设计*

张 培1,2,尚 丽2 ,刘 韬2,汪一鸣

(1. 江苏省现代企业信息化应用支撑软件工程技术研发中心,江苏 苏州 215104;2. 苏州职业大学, 江苏 苏州 215104;3. 苏州大学,江苏 苏州 215021)

1 引 言

随着FPGA平均门成本的下降,在基于FPGA的硬件平台上开发应用程序成为高性能嵌入式系统设计者的一种新选择。但是,由于过去割裂了硬件和软件开发工具、开发方法之间的关系,在面向软件应用中的FPGA技术,较之传统处理器所具有的优势并没有体现出来。

传统的硬件描述语言(HDL)主要用于描述数字系统的结构、行为、功能和接口,对较为复杂的算法设计实现则支持不够。面对当今数字系统设计中涉及的越来越多、越来越复杂的算法描述和建模,开始出现了描述硬件的C语言。对比相同功能的传统硬件描述语言,大部分计算密集型的算法如果用C代码描述,其硬件规模相对会较小,性能却很接近。

Impulse C 语言是目前比较新的一种硬件C语言,是一种基于C语言的FPGA开发语言,并且能够很好地与VHDL语言相融合。Impulse C的目标是允许C语言能被用来描述一个或多个处理单元(进程),并且将这些处理单元连接,组成一个能够实现于硬件中的完整的并行应用(如映射到FPGA的逻辑)。这种多进程并行方法非常适用于基于FPGA的嵌入式系统,也适用于很多与传统的处理器相连接的FPGA模块所组成的大型高性能计算平台[1]。同时,CoDeveloper设计平台允许设计师开发C语言算法,与HDL设计输入相比,可以使FPGA设计过程更加快捷。

LDPC码是一种新的高性能线性纠错码,其译码复杂度低,且可实行并行操作,非常适合于FPGA的并行计算。因此,本文基于最新一代从Impulse C编程到硬件编译的便捷技术,提出了一种对LDPC码译码器进行FPGA设计的新方案。

2 LDPC码译码器的设计

2.1 Impulse C编程模型

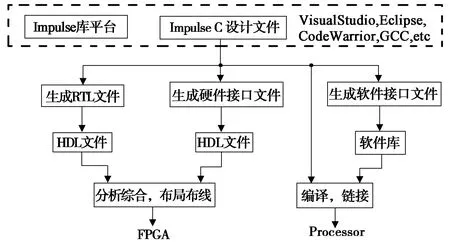

Impulse C编程模型如图1所示,它是一个针对面向流的、软硬件混合式应用程序的通信顺序进程模型。从软件到硬件编译器的过程是实现快速开发的关键,它保证了应用程序直接编译到FPGA。通过将C语言编译导入现有设计流程,设计者能够迅速创建和评估不同的软硬件划分策略,建立工作产品原型。

图1 Impulse C编程模型Fig.1 Impulse C programming model

2.2 软件设计

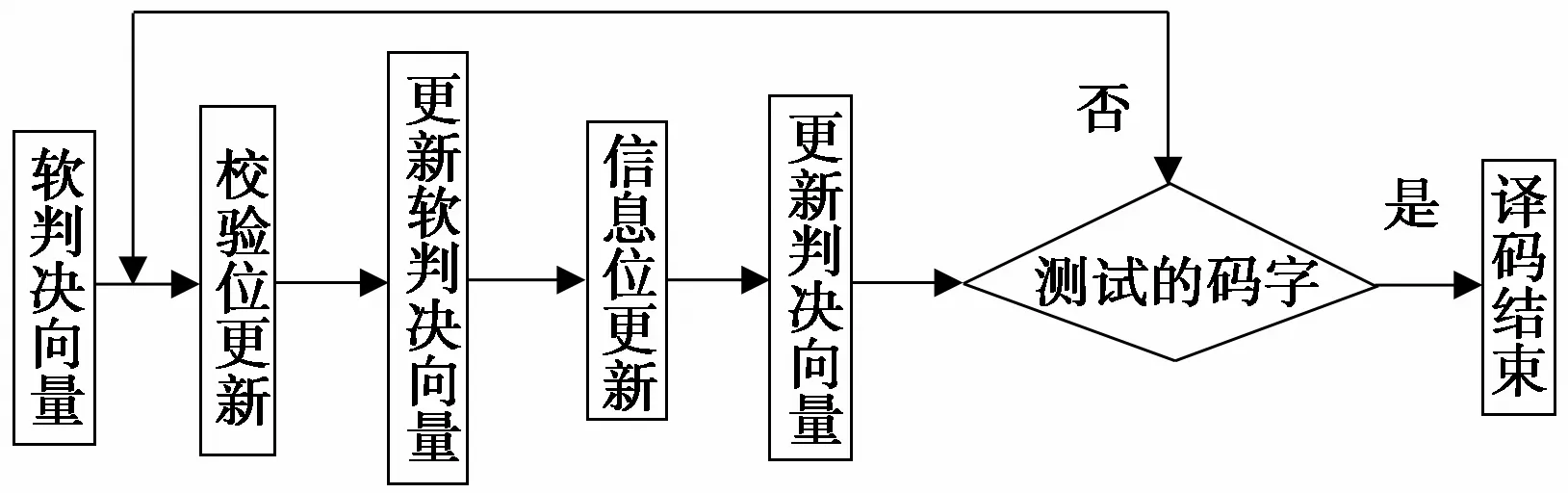

LDPC码的译码算法有多种,为了在译码性能和复杂度之间达到更好的平衡,同时基于硬件实现方面的考虑,本设计选择采用最小和算法(Min Sum Algorithm,MSA)[2-4],从而避免了进行复杂的计算和查表,复杂度得到了明显降低,而且译码性能也较好,适合硬件实现。其基本流程如图2所示。

图2 译码算法流程图Fig.2 Decoding algorithm flow

Impulse C编程的核心是进程和流。通信顺序进程编程模型是通过一组数据类型和内部库函数来实现的。这些库函数用来在进程之间进行流和信号的数据通信,还可以将进程分配到目标编程平台的实际硬件资源上。可见,多个进程之间的相互通信和同步主要通过数据流方式完成。如果一个应用程序具有设计良好的流接口,那么当它被映射到实际硬件和软件时,就能高效运行。本次设计中读取待译码数据的一段程序如下:

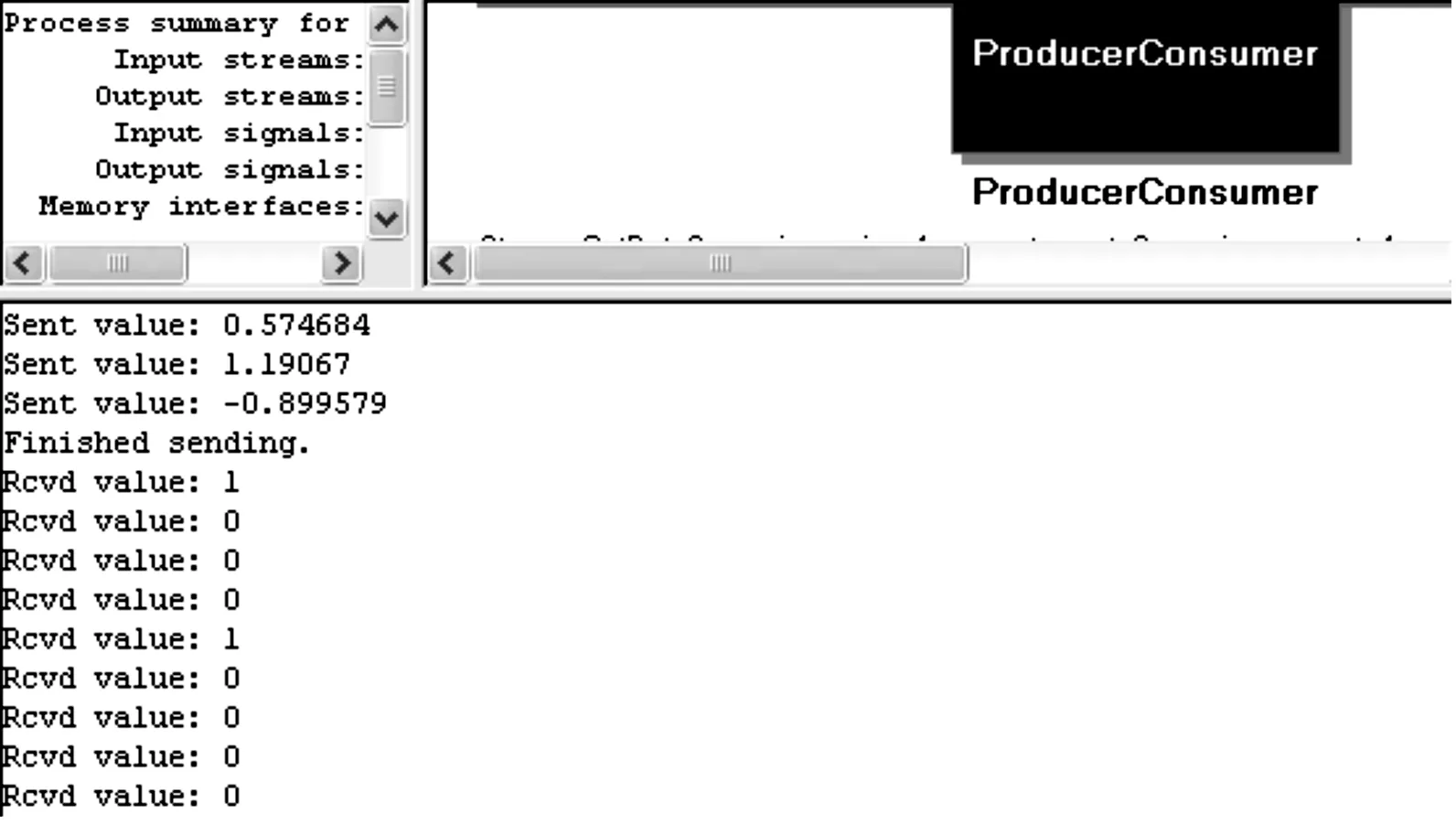

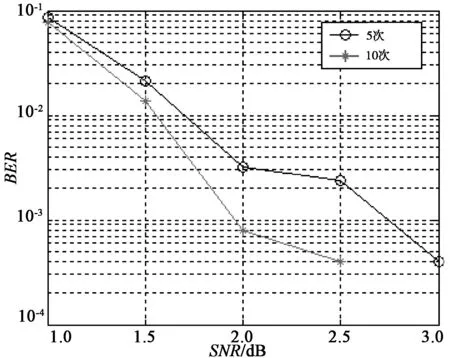

for ( i =0;i { pragma CO PIPELINE if( co_stream_read(InDataF, &nSample, sizeof(float))==co_err_none); IF_SIM(samplesread++;); Lc[i] = nSample; } 这里使用了CO PIPELINE流水线指令,因为流水线技术允许循环的多重迭代并行执行。假设N取1,若不使用流水线,处理100个数据需要200个时钟周期。现在使用流水线后,将产生一个二级流水线。当第一个数据被读进来以后,第一级立刻开始读取第二个数据,与此同时,第二级使用刚读进来的数据进行计算,这样只需要101个周期就能处理100个输入数据了。可见,以数据流的形式来读取数据和输出数据,应用程序可以一边从外部接收数据,一边处理数据,效率更高,也能大大简化硬件软件系统的设计和调试。 编译器首先确定应用中的硬件和软件进程,将相应的循环转化为等价的并行语句,再生成可仿真的HDL文件。底层模块描述了原来用co_process_config声明的硬件进程,顶层实体引用了包含LDPC译码器实际功能的底层实体,这些功能是用寄存器传输级(RTL)代码表示的。实际上,硬件生成器把每一个进程当作一个独立的状态机来实现。在LDPC译码算法的状态机中,共有195个状态,分别描述译码算法的初始化和迭代部分,以及用来驱动状态机的时钟逻辑。构造规则(3,6)LDPC码,取125×250的校验矩阵,将经过AGWN信道后的数据作为译码前数据,每次读取一组250 bit数据进行译码,共读取10次。在CoDeveloper开发环境下进行桌面仿真,结果包含一个生产者测试进程、一个代表LDPC码译码算法的Impulse C进程和一个消费者测试进程。数据流在系统各个不同进程的流动情况,以及译码输出桌面仿真结果如图3所示。 图3 数据流在不同进程的流动及桌面仿真结果Fig.3 Data flow of the different process and the decoding output of the desktop simulation 最大迭代次数分别取5次和10次时的BER性能比较如图4所示。可见,由于迭代次数增多,在相同时间内所得误码率明显下降,这在一定程度上弥补了标准最小和算法由于采用近似计算而带来的性能损失。 图4 不同迭代次数下的性能比较Fig.4 Performance comparison with different iteration number 本次设计中选用的FPGA芯片是XC2V2000-4-bf957,这是由于该芯片的片内资源丰富,无需外部缓冲就可实现高速数据采集,而且适合进行浮点运算和数据存储操作。当时钟频率为50 MHz,迭代次数为10次,本设计耗费了5 493个LUT,译码速率为10 Mbit/s, 功耗为367 mW。 基于传统的HDL硬件描述方法,当时钟频率为50 MHz,译码迭代次数为10次,文献[5-7]分别采用3种不同的结构在FPGA上实现了3种码率为1/2的LDPC码译码器芯片。其中,采用串行结构实现的译码器耗费了3 039个LUT,速率仅为1 Mbit/s。采用全并行结构实现的译码器速率可达1 Gbit/s,却是以增加极高的芯片复杂度为代价的。采用半并行结构实现的译码器速率为54 Mbit/s,是译码速率和资源消耗的一种折中,但由于构造方法的限制,现有的大多数LDPC码并不适合采用半并行结构。 译码器的译码速率和硬件资源消耗是考虑 LDPC 码译码器硬件实现时两个重要的因素,较高的译码速率往往意味着更大的资源消耗。对比相同功能的传统硬件描述方法,在本设计中由于Impulse C库可以有效地利用Streams-C编译器提供的“流式编程”方法,芯片内部并行译码结构采用流水线结构,降低了逻辑单元的使用量,硬件规模相对较小;同时,有些系统并不要求很高的译码速率,例如第三代移动通信系统要求达到的最高译码速率为10 Mbit/s。 因而本设计实现的译码器占有较低的资源利用率,数据吞吐量也能够满足实际工程的需要,具有良好的工程应用能力。 本文基于Impulse C语言的FPGA编程技术的优势,创建实现了一个面向数据流的LDPC译码硬件算法,为软件工程师从C到开发基于FPGA 的嵌入式硬件系统提供了一种快捷的新思路。面向FPGA性能,进一步优化Impulse C代码,从而提高其纠错性能;采用系统级并行改善吞吐率,从而得到更高的译码速率以及更低的资源利用率将是下一步的研究方向。 参考文献: [1] Davide Pellerin,Scott Thibault. Pratical FPGA Programming in C[M].New York: Prentice Hall PTR,2007:19-51. [2] 朱嘉,张海滨,潘宇.一种低复杂度的LDPC码迭代译码算法[J].电讯技术,2006,46(5):94-97. ZHU Jia, ZHANG Hai-Bin, Pan Yu. A Low-complexity Iterative Decoding Algorithm for LDPC Codes[J]. Telecommunication Engineering,2006,46(5):94-97.(in Chinese) [3] 邓炯.几种LDPC码的性能比较[J].电讯技术,2009,49(5):82-85. DENG Jiong. Performance Comparison of Several LDPC Codes[J]. Telecommunication Engineering,2009,49(5):82-85.(in Chinese) [4] Thomas J Richardson,Rudiger L Urbanke.Efficient Encoding of Low-Density Parity-Check Codes[J].IEEE Transactions on Information Theory,2001,47(2):638-656. [5] Levine B, Taylor R,Schmit H. Implementation of near Shannon limit error-correct codes using reconfigurable hardware[C]//Proceedings of IEEE Symposium on FCCM. Los Alamitos:IEEE,2000:217-226. [6] Andrew J Blanksby,Chris J Howland. A 690mW 1Gbit/s 1024bit, rate-1/2 low-density parity-check code decoder[J].Journal of Solid-State Circuits,2002,37(3):404-412. [7] Zhang T,Parhi K K. A 54Mbit/s (3, 6)-regular FPGA LDPC decoder[C]//Proceedings of IEEE SIPS.[S.l.]:IEEE,2002:127-132.2.3 硬件实现

3 结果分析

4 结论