基于流水线ADC的高速数据采集系统设计

黄 峰

(黄山旅游发展股份有限公司云谷索道分公司,安徽 黄山 242709)

1 引言

随着雷达、 通信、 遥测遥感、 医学成像、精确控制等技术应用领域的不断扩展,电子系统需要处理的模拟信号带宽以及动态范围越来越大,人们对数据采集系统的采集精度、 数据采集速率、数据采集系统的存储量等都提出了更高的要求。由于高速与高精度数据采集所需要的存储带宽变得越来越大,数据采集系统对模数转换器(ADC)的采样速度与精度要求也越来越高,因此了解ADC的特性并选择合适的ADC对高速高精度数据采样系统的设计至关重要。目前新一代雷达和医学成像应用系统对于其所使用ADC的精度要求达14位,并且采样速度要求达到100Msps以上,而能满足上述应用需求的ADC为流水线结构。本文通过以高速高精度流水线ADC的结构和原理为信号分析的出发点,进一步采用ADI公司的14位125Msps高速ADC芯片AD9246为核心,给出了一套设计完整的高速数据采样系统的实现方案。

2 流水线ADC原理及最新发展状况

2.1 流水线ADC原理分析

基本的流水线结构ADC由多级流水线构成,每一级都包含采样保持电路、低分辨率的子ADC、子数模转换器电路(DAC)、余量和增益电路(最后一级电路没有子DAC)[1],图1所示为流水线ADC的典型系统结构图。流水线ADC电路由许多级组成,级的数目一般与ADC的分辨率相关。每一级是由低分辨率的ADC电路和D/A转换电路、采样保持器及增益为2ki的电路组成。电路由两相互不交叠时钟进行控制,使得每级结构中的采样保持电路和级间增益电路分别工作在采样相ΦS和放大相Φf。图1中所示的1~n级转换电路(Stagel~Stagen)的方框中,时钟ΦS和Φf的排列次序就代表了各级电路之间的工作状态对应关系。

在进行模数转换时,stagel中的S/H电路对Vi进行采样和保持,同时子ADC对其进行A/D转换,所得的转换结果不仅作为本级转换结果输出到延迟对准寄存器阵列,而且也作为子DAC的数字输入以实现对Vi信号的估计,模拟减法电路实现Vi与估计值相减,所得的余量信号在放大相通过残差放大器放大后,作为本级模拟输出量传输给Stage2。以此类推,每级的转换输出通过延迟对准寄存器阵列在时序上对齐后输出。

图1 流水线ADC典型结构图

从整个转换过程来看,流水线工作方式可以看作是串行的,但就每一步转换来看是并行工作的。因而总的最大转换速率取决于单级电路的最大速度,而且总的转换速率与流水线结构的级数没有关系。流水线型结构在所有这些改进的结构中对于精度、速度和功耗等性能指标的折中具有最大的自由度,因而在高速高精度领域获得了最广泛的应用。

2.2 流水线ADC最新发展状况

目前国内外比较成熟的高速高精度流水线ADC大多是基于高增益大带宽的OTA和开关电容电路来实现的。采用该技术实现的精度达14~16位、采样速度超过百MHz、SFDR超过90dB的中频采样流水线ADC报道已经很多[2]。ADI公司的Ahmed M. A. Ali等人在2006年就发布了一种10MHz输入条件下SFDR达100dB的14位125Msps中频采样流水线ADC[3];2010年他们又发布了一种16位250Msps中频采样流水线ADC,该ADC在250MHz全速采样条件下对于10MHz输入信号SFDR同样达100dB[4], ADI公司的Siddharth Devarajan等人在2009年发布了一种采用CMOS工艺实现的16位125Msps中频采样流水线ADC,该ADC在125MHz全速采样条件下对于30MHz输入信号SFDR达96dB[5]。同时TI公司也推出了14位400Msps ADC电路产品ADS5474和14位250MspsADC电路产品ADS6149,其中ADS6149的功耗为687mW,而ADS5474的功耗达2500mW[6~7]。总的来说流水线ADC的发展脉络是追求更高的精度和更高的采样速度,以满足不断突飞猛进的应用系统的需求。

3 高速数据采集系统架构及实现

3.1 高速数据采集系统结构

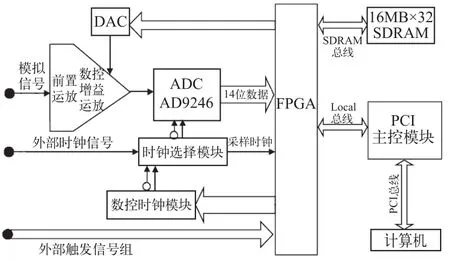

本文所针对高速高精度控制系统要求数据采集系统的时钟采样频率至少为100MHz,模数转换器分频率至少为14bit,因此本文设计了1个14bit 150MS/s的数据采集系统。该采集系统采用PCI总线与计算机相连,数据采集系统利用板卡大容量存储器对有用信息进行实时存储,信息采集由系统外部触发信号控制[8]。数据采集系统的框架结构如图3所示。整个采集系统分为4个部分:模拟信号调制部分、时钟处理模块、数据高速缓存模块、数据传输与触发模块。

图2 14-bit 125 MS/s数据采集系统框图

3.2 模拟信号调制

模拟信号调制包括模拟信号前放、信号数控增益以及单端转差分部分。模拟信号前置运放实现输入信号的阻抗匹配及信号的低通滤波。在数据采集系统中为了提高采集系统的信噪比,应该使ADC的模拟输入信号幅度接近满幅度。因此,在前置运放之后增加了一个压控增益运放芯片以调整ADC输入信号的幅度。压控增益芯片在90MHz的模拟带宽下,其增益范围为-11dB~30dB,该压控增益芯片的控制电压由一片8bit的DAC产生,DAC芯片的数字控制输入由FPGA控制与产生。数据采集系统的ADC采用ADI公司的125Msps 14bit芯片AD9246。由于该ADC模拟信号为差分输入,因此从压控增益芯片输出的模拟信号经过单端转差分电路连接到ADC芯片上,从ADC输出的14bit数字信号直接连接到FPGA芯片上。

3.3 时钟模块

为了增加采集系统的灵活性和普适性,ADC芯片的采样时钟可以来自外部时钟,也可以来自内部时钟。采样时钟的选择是由板卡跳线器决定的。外部时钟通过一个SMA接插件连接到采集板卡上,外部时钟信号为TTL电平,由于ADC采样时钟需要PECL电平,因此外部时钟通过TTL到PECL电平转换芯片连接到时钟选择模块上。ADC系统的内部时钟由数控时钟模块产生,数控时钟模块的时钟输出范围为25MHz~400MHz,输出信号为PECL信号,可以直接与ADC的采样时钟连接。该频率合成器的输出时钟可以由FPGA芯片的数字信号进行控制,输出时钟调整精度可以精确到1MHz。

在数据采集系统中,尤其是高速数据采集系统中,时钟是一个非常重要的信号。不同时钟的抖动相差比较大。当采集系统的输入模拟信号带宽较大时,时钟抖动对采集系统的信噪比影响不能忽略。把量化噪声的因素也考虑进去,对于14bit的ADC,当输入信号频率为40MHz时,若要使ADC采集系统的信噪比大于60dB,采样时钟的抖动必须控制在10ps以内,否则,外部时钟抖动造成的信噪比损失会降低AD9246的性能。本系统输出时钟抖动峰值最大为25ps,时钟抖动均方根为10ps左右,满足系统的设计要求。如果要使用外部时钟,必须选择具有低抖动的外部时钟源。为了增加采集系统的灵活性和普适性,ADC 芯片的采样时钟可以来自外部时钟,也可以来自内部时钟。采样时钟的选择是由板卡跳线器决定的。

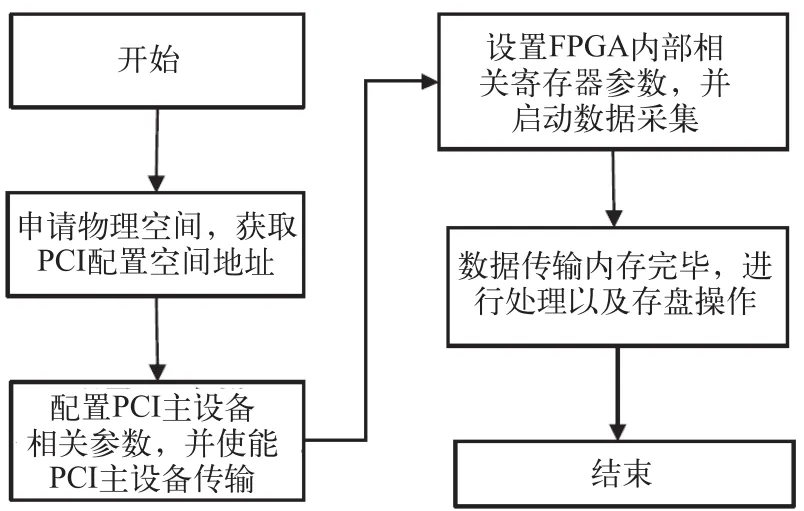

3.4 数据采集软件设计

为了提高数据的传输率和减少CPU资源的占用,采用PCI主控方式实现数据采集到计算机内存的数据传递。在数据传输过程中,CPU不对这一过程进行控制,图3为单次数据传输时的软件工作流程。软件首先执行PCI总线扫描,获取PCI控制芯片所占用的PCI配置空间地址,接着向操作系统申请采集数据传递到计算机内存的物理空间,并把该物理空间地址映射到PCI主设备上。然后软件配置控制芯片内部寄存器,包括DMA传输数据总量以及PCI总线传输特性等寄存器,并使能控制芯片PCI主控操作。控制芯片等待FPGA 向其发送采集数据,若控制芯片内部写FIFO通道非空,则发起PCI总线操作把数据传递到计算机内存中。软件根据实际雷达需求通过控制芯片的对FPGA内部相关寄存器进行配置,设置数据采集系统相关参数,并触发使能FPGA数据采集。信号的数据采集及存储由硬件全自动完成,当采样数据达到控制芯片单次数据传输总量时,控制芯片向计算机发起中断申请。软件在该中断处理程序中完成采样数据的读取及存盘操作,并能对采样数据进行相应的处理,如FFT变换。在计算机进行多次DMA数据传输参数设置期间,数据采集卡大容量缓存保证了采样数据的无丢失存储。

图3 软件工作流程

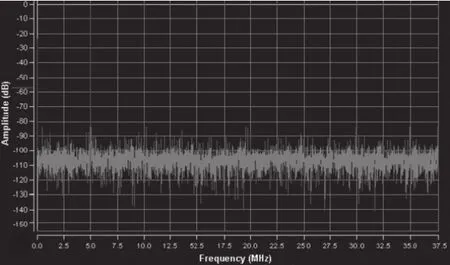

3.5 测试结果

本文的数据采集系统采样频率为25MHz~125MHz。采集系统支持多种外部触发模式,外部触发模式由可编程逻辑器件动态设计。板卡内置的32MB片内存储器决定了有用信息的采集时间,在125MHz采样频率下,有用信息持续采集时间能够达到128ms。测试表明,该系统在75Msps采样速率下对于4.9MHz输入信号的信噪比达到65dB,无杂散动态范围(SFDR)达84dB,满足系统的性能需求。

图4 数据采集系统测试动态性能

4 结束语

本文以高速流水线ADC性能特点为出发点,完成了14位精度125Msps高速数据采集系统的设计。测试结果表明,本系统能够完成各类高频信号的实时采集与存储,系统信噪比性能达到设计要求。由于采用可编程逻辑器件,因此系统还能满足其他场合的需求。

[1] Stephen H.Lewis, Paul R. Gray. A Pipelined 5-M/s 9-bit Analog-to-Digital Convert [J]. IEEE J. Solid-State Circuits, 1987, 22(12): 954-961.

[2] 陈飚,姜思晓,周洁,等. 流水线模数转换器研究现状[J].电子与封装,2011,11(1):13-17.

[3] Ahmed M.A. Ali, Chris Dillon, Robert Sneed,et al. A 14-bit 125 MS/s IF/RF Sampling Pipelined ADC With 100 dB SFDR and 50 fs Jitter[J]. IEEE J.Solid-State Circuits,2006, 41(8):1846-1855.

[4] Ahmed M.A. Ali, Andy Morgan, Chris Dillon, et al. A 16b 250MS/s IF-Sampling Pipelined A/D Converter with Background Calibration[C]. ISSCC 2010, Dig.Tech.2010: 292-294.

[5] Siddharth Devarajan, Larry Singer, Dan Kelly, et al. A 16b 125MS/s 385mW 78.7dB SNR CMOS Pipeline ADC[C]. ISSCC 2009, Dig.Tech,2009: 86-88.

[6] Texas Instruments. 14-Bit 250MSPS ADCs With DDR LVDS and Parallel CMOS Outputs[J].ADS6149, 2008.

[7] Texas Instruments. 14-Bit 400MSPS Analog to Digital Converter, ADS5474, 2008.

[8] 张俊杰,章凤麟,叶家骏. 高速数据采集系统设计[J]. 计算机工程,2009, 35(1):207-210.