基于边缘的实时视频缩放引擎的设计与实现

杨金孝, 张金凤,, 周坚峰, 万 鹏

(1.西北工业大学 电子信息学院,陕西 西安 710129;2.中航工业无线电电子研究所 上海 200233;3.中国人民解放军边防学院训练部办公室 陕西 西安710108)

由于显示器分辨率是固定的,所以当源输入图像分辨率与显示器的分辨率不匹配时,必须使用图像缩放引擎对输人图像分辨率进行调节使其在显示器上满屏显示。

图像缩放的算法很多,目前应用于图像缩放的算法主要分两大类[1],第l类是不基于边缘的图像缩放算法,主要包括:最近邻插值算法、双线性插值算法、双三次插值算法、B样条插值算法等,在这类算法中,新得到的目标像素值与图像的边缘信息无关,只与其位置及其邻域的像素值有关,这些经典算法硬件实现比较容易,数据处理过程容易控制,计算时间相对较短,但是低阶算法得到的图像会出现“马赛克”现象[2],而高阶算法由于“振铃”效应会使图像边界模糊[3]。第2类是基于边缘的图像插值算法,这类算法新得到的目标像素点的灰度值与源图像的边缘相关,缩放后的图像有很好的视觉效果,图像失真度比较小,但是此类算法硬件实现复杂,数据运算的时间长,占用了比较多的片上资源,很少应用于实时条件下的图像缩放[4-5]。文中设计的缩放引擎用到的图像插值方法是一种用于实时条件下的基于边缘的自适应图像插值算法。该算法通过比较相邻源像素的二阶差商[6]的绝对值自动选取一组源像素,之后根据二阶牛顿插值公式获得目标像素的值。文献[6]通过比较各种插值算法处理图像的主观视觉效果、峰值信噪比及边缘信息,得出该算法不仅获得了比不基于边缘插值算法更满意的视觉效果,而且复杂度比不基于边缘的双三次插值算法更低,远低于传统的基于边缘的插值算法。

1 自适应插值算法原理

传统的基于边缘的插值算法通过检测源图像的边缘,根据图像的边缘信息对图像的不同区域采用不同的插值方法。此方法不但对图像进行边缘检测,而且要存储图像的边缘信息。因此,由于其复杂性高一般不用于实时图像处理。

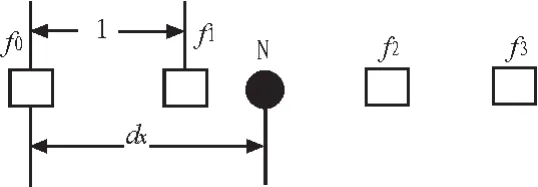

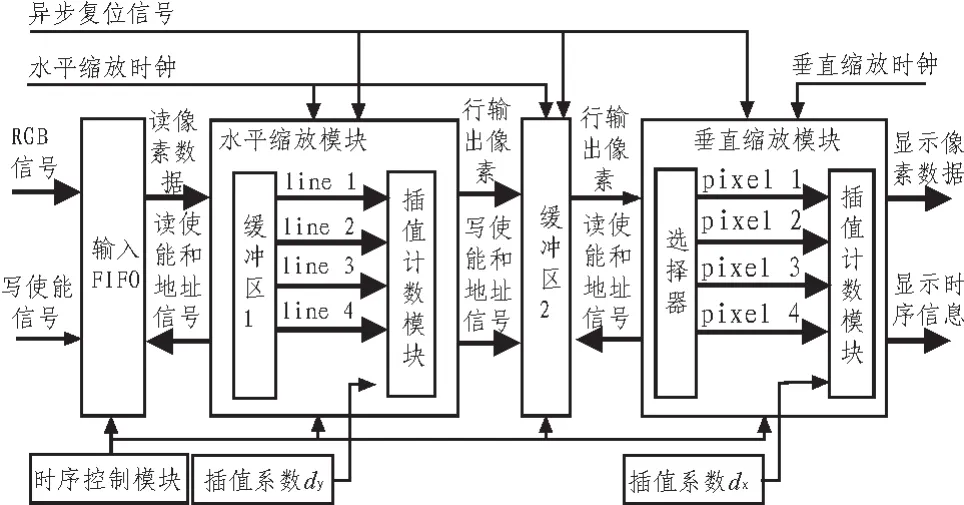

对图像进行实时缩放处理时,通常将二维图像分解成水平和垂直两个一维方向分别进行插值处理。除边界像素点外[7],目标图像中任意像素点与源图像像素点的位置关系如图1所示,任何目标像素点F均能找到与之对应的源像素点f0、f1、 f2、 f3,其中 dx(1≤dx<2)为目标像素点 F 与源像素点间的距离。这样,采用二阶牛顿插值函数得到目标像素点F的灰度值为:

当采用公式(1)来计算目标像素的灰度值时,图1中的目标像素灰度值 F 可以通过源像素(f0、 f1、 f2)或(f1、 f2、 f3)计算得到。当f0、f1、f2、f3灰度值差别不大,处于图像的平坦区域时,使用以上两组源像素计算得到F的灰度值基本相同;而当f0、f1、f2、f3灰度值差别很大,处于图像细节部分或边沿时,使用以上两组源像素计算得到F的灰度值将差距很大。

图1 自适应牛顿插值的一维计算模型Fig.1 Adaptive Newton interpolation’s one dimensional calculate model

若采用传统的差值算法,如最近邻插值和双线性插值,目标像素点F只与源像素点f0、f1有关,而采用双三次插值计算的目标像素点F与源像素点f0、f1、f2、f3有关。但这些算法都不判断源图像中各像素点之间的相关性,结果不同程度地导致包含丰富信息的图像边缘模糊。各像素点间的相关性隐含在图像本身,只要选择一个合适的参数便能得到这一重要特征。

源像素点(f0、 f1、 f2)和(f1、 f2、 f3)的二阶差商定义如下:

这样,将相邻3个点的二阶差商的绝对值作为衡量该3个点的相关性大小的标准,绝对值越小,相关性越大,表明该组各像素处在同一图像区域的可能性越大,反之亦然。通过比较两组源像素点的相关性,选择计算目标像素F的值的一组源像素,然后再采用二阶牛顿插值公式完成目标像素点的计算。综上所述,基于图像边缘计算目标像素F的值的插值公式如下:

2 算法的硬件实现与验证

2.1 系统结构

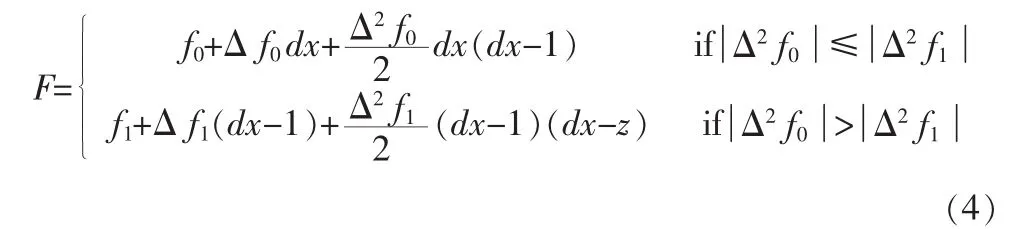

按照第2章介绍的自适应牛顿插值算法,对算法进行面向硬件设计的优化和改进,完成了视频图像缩放引擎的硬件实现。系统对数据的处理过程可以分为两个阶段:首先对每个有效扫描行中的有效像素作水平方向的缩放处理,之后以扫描行为单位作垂直方向的缩放处理。整个图像缩放引擎由四个顺序连接的子模块即输入FIFO、水平缩放模块、行缓冲存储器1以及垂直缩放模块所构成,如图2所示。每个缩放单元输出的插值点只和输入的四个点关联,使自适应牛顿插值算法得以硬件实现的同时又节省资源。使用同一个缩放引擎可以实现放大和缩小操作,可移植性好,且不限制缩放倍数的范围和取值(如有些缩放模块限制缩放倍数必须为2k)。

图2 缩放内核模块结构框图Fig.2 System block diagram of image scaling program

2.2 数据缓冲模块

缓冲存储器用来存储缩放前后的图像数据信息,本设计中使用异步FIFO和双端口RAM作为缓冲。由于缩放内核工作在多时钟域,因此在本设计中采用异步FIFO作为数据缓冲区来完成图像的暂存功能,一方面以源时钟将图像数据信号写入FIFO,两一方面以水平缩放时钟从FIFO中读取水平缩放模块需要的数据。

在进行水平插值之前,需要先接受四行数据后才能开始处理。为保证系统能连续、快速处理接受的数据信号,在水平缩放模块和输入FIFO之间加上一个由4个双端口RAM组成数据缓冲区1,每个双端口RAM的容量为一行目标分辨率的图像数据,从FIFO读取的数据只能写入缓冲区1,水平缩放模块只能读取缓冲区1。使用HDL代码编写状态机对4个RAM缓冲模块控制,并产生一个FIFO读取命令fifo-rd,控制从FIFO读取数据,使FIFO不溢出,且能满足输入和水平处理的速度要求。

水平缩放模块输出的数据是按行输出的,而垂直缩放模块需要四行中的同列数据来进行垂直方向上的缩放。而根据缩放比例的不同,时域上行与行间可能存在间断,为了进行垂直方向上的缩放运算,在水平缩放和垂直缩放模块之间需要一个由5个双口RAM组成的数据缓冲2,每个双端口RAM的容量为一行目标分辨率的图像数据。水平缩放模块只能对缓冲区2进行写操作,垂直缩放模块只能对缓冲区2进行读操作。

2.3 运算系数生成模块

根据插值运算公式(4)进行实时插值运算时,需要准确及时的求出两个运算系数dx和dy[8-9]。由于FPGA本身不支持浮点运算,需要设计一种浮点运算器来实现计算过程中的浮点运算。为了保证计算精度,将缩放因子扩展到16位,高4位表示整数部分,低12位表示小数部分,即Fix_16_12。根据不同分辨率之间可能出现的缩放比例关系,把水平方向和垂直方向缩放因子的累加和输出分别设计为Fix_21_12和Fix_22_12。采用上述浮点表示方法后,dx和dy就变成累加和的小数部分与13’b1的和,恰好可以通过把1与截取的Fix_21_12和Fix_22_12的低12位并位得到dx和dy系数。用FPGA内数字逻辑完成浮点运算时,我们必须时刻记住每个浮点数表示为二进制码的小数位在哪位上。扩展后的数据运算后需要将结果除以,即右移12位。

2.4 插值计算模块

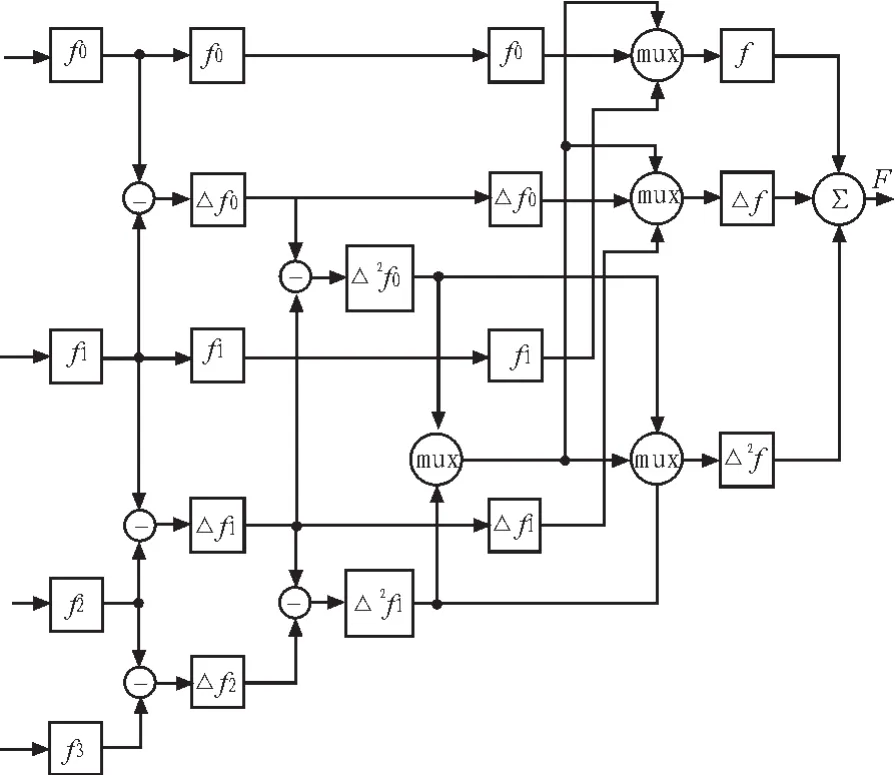

插值计算模块是缩放模块中占用资源较大的模块,运算器结构的简化可以极大的降低所消耗的资源,降低缩放模块实现的复杂度。由(1)可以看出,本方法需3次乘法和5次加法完成一次插值运算。而双三次插值计算一目标像素点需5次乘法和10次加法运算,对比这两种算法,本算法约减少40%的计算量[10]。根据公式(4)设计了一种具有3级流水线特性的运算逻辑结构,如图3所示。系统的输入f0、f1、f2、f3由缓冲区1、缓冲区2提供,通过并行的加法运算即可得到一阶差 商 Δ f0、Δ f1、Δ f2和 二 阶 差 商 Δ2f0、Δ2f1, 比 较和的大小产生的逻辑量作为3个多路选择器 (MUX)的判断条件,多路选择器自动选择一组值参与式(4)所示的求和运算最终得到插值结果F。

图3 插值计算模块单元Fig.3 Logical structure of interpolation calculating unit

2.5 验证

在自适应牛顿插值图像缩放算法的上述功能模块设计完成后,用Verilog HDL语言对算法进行描述,并在Xilinx公司提供的可编程逻辑器件集成开发环境Xilinx ISE10.1中进行编译和综合,目标FPGA芯片选为Virtex-4系列的XC4VSX-35。经实验验证,本文采用的算法能较好的消除插值后出现的图像边缘模糊,提高插值后图像的质量,得到令人满意的图像缩放效果,且计算复杂度小、硬件资源需求少。

3 结束语

提出了一种基于边缘自适应插值算法的缩放引擎的有效设计方法,设计了硬件实现结构,并用Verilog语言进行描述,综合出目标代码,最后搭建FPGA验证平台。从实验结果可以看出,采用该算法进行图像缩放可得到满意的视觉效果,而且算法复杂度低,便于硬件实现。综上所述,该算法适应于实时条件下的图像缩放。

[1]赵慧波.用于平板显示器的图像缩放引擎的设计与研究[D].武汉:华中科技大学,2005.

[2]刘志军,蔡超,彭晓明,等.一种新颖的基于遗传算法的正则化图像插值方法 [J].中国图象图形学报,2004,9(8):935-940.LIU Zhi-jun,CAI Chao,PENG Xiao-ming,et a1.A novel regularized image interpolation algorithm based on genetic algorithm[J].Journal of Image and Graphics,2004,9 (8):935-940.

[3]OHIRA M,MORI K,WADA K,et al.High quality image restoration by adaptively transformed sampling function[C]//Proceedings of IEEE Conference on Communication,Computer and Signal Processing,in Victoria,Canada,1999:201-204.

[4]Jensen K,Anastassiou D.Subpixel edge localization and the interpolation of still images[J].IEEE Transactions on Image Processing,1995,4(3):285-295.

[5]Xin L,Orchard,M T.New edge-directed interpolation[J].IEEE Transactions on Image Processing,2001,10(10):1521-1527.

[6]XIAO Jian-ping,ZOU Xue-cheng,LIU Zheng-lin,et al.Adaptive interpolation algorithm for real-time image resizing[C]//IEEE Proceedings of the First International Conference on Innovative Computing, Information and Control(ICICIC'06),2006:221-224.

[7]刘政林,肖建平,邹雪城,等.基于边缘的实时图像缩放算法研究[J].中国图象图形学报,2008,13(2):225-229.LIU Zheng-lin,XIAO Jian-ping,ZOU Xue-cheng,et al.Edgebased algorithm of real-time image resizing[J].Journal of Image and Graphics,2008,13(2):225-229.

[8]郑俊杰,陆虎敏,方向忠.基于自适应插值算法的视频图像缩放技术及其FPGA实现[J].航空电子技术,2008,39(2):46-50.ZHENG Jun-jie,LU Hu-min,FANG Xiang-zhong.Video image sealing technology based on adaptive interpolation algorithm and its implement by using FPGA[J].Avionics Technology,2008,39(2):46-50.

[9]盛磊.面向特种LCD图像处理方法与FPGA实现研究[D].合肥:合肥工业大学,2005.

[10]Han J K,Baek S U.Parametric cubic convolution scaler for enlargement and reduction of image[J].IEEE Transactions on Consumer Electronics,2000,46(2):247-256.