面向存储测试系统的FT245RL数据传输控制器设计

裴峰,吴健,魏海潮,王珺楠

(中北大学 信息与通信工程学院,山西 太原,030051)

0 引言

存储测试是指在对被测对象无影响或在允许范围的条件下,在被测体内置入微型数据采集与存储测试仪,现场实时完成信息的快速采集与记忆,事后回收的记录仪器[1]。存储测试技术在载人航天测试、爆炸冲击波测试、炮弹膛压测试等诸多领域应都有广泛的应用[2],目前大多数的存储测试系统都是由CPLD和单片机配合工作来实现,由于系统包含的器件较多这为系统的设计和调试带来了很大的难度,而且最终的系统在稳定性和可靠性都较差[3]。为了解决上述问题本文设计了一种基于单片FPGA的存储测试系统。为了实现整个系统由单片FPGA来控制,在FPGA内部运用有限状态机设计方法设计了一个针对FT245RL的数据传输控制器实现了过去由单片机和CPLD配合才能完成的功能。

1 硬件设计

1.1 基于FPGA的存储测试系统

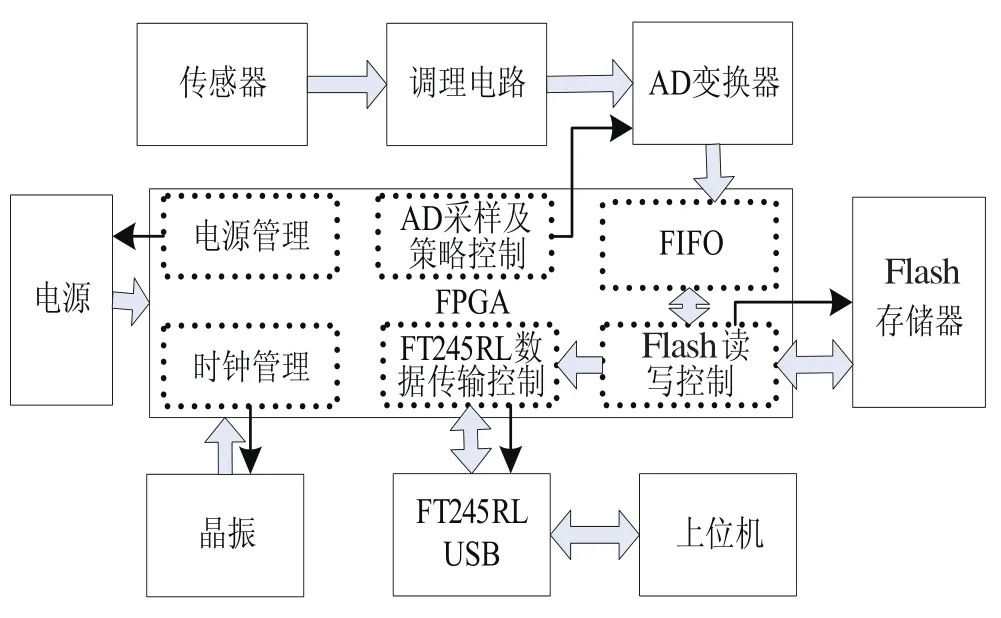

图1给出了基于FPGA的存储测试系统总体结构图,本系统采用XILINX公司的XC4VSX25 FPGA作为系统核心控制单元、采用AD公司的AD7492作为系统模数转换器,采用三星公司的k9k2G8U0M FLASH作为系统数据存储介质(存储空间满足实际需要),采用FT245RL芯片作为系统板与上位机链接的通信接口芯片[4-5]。

系统的总体工作流程为:传感器输出的模拟信号经过调理电路调整到AD可采范围后AD转换器对其进行转换,FPGA提供AD转换的时钟,在一次模数转换周期内,AD转换的12位的数据分高6位和低6位存储到FPGA内部的FIFO中,最后在FPGA的控制下将FIFO中的数据存入FLASH。当整个采集完成后,在需要的时候就可以通过USB接口将Flash中的数据传输到上位机来显示和分析。

图1 基于FPGA的存储测试系统结构图

1.2 USB协议及集成芯片

目前,USB有两个规范,即USB1.1和USB2.0。USB1.1是目前较为普遍的USB规范,其低速方式的传输速率为1.5Mbps,高速方式的传输速率为12Mbps(1.5MByte/s)。USB2.0规范是由USB1.1规范演变而来的,其理想传输速率为480Mbps(60MByte/s),足以满足大多数外设的速率要求[6]。USB是一种复杂的传输协议,这给USB接口的设计和开发带来很大难度。文献[7-8]的研究表明,在应用层对数据采集系统进行USB接口设计时,可以选择集成USB协议的专用芯片进行二次开发应用,从而降低了系统开发难度。鉴于此,通过查阅大量资料,本设计选用美国FTDI公司的FT245RL芯片进行USB接口的设计。

1.3 USB接口硬件设计

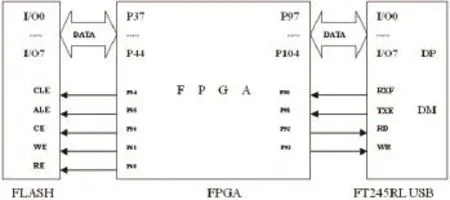

图2给出了以FPGA和FT245RL为核心器件的USB接口原理框图。图2中,Flash是集成于存储测试系统中的数据存储器,测试过程结束后,Flash中存满了测试数据。FPGA在USB接口中起到桥梁的作用,其I/O端口37-44与Flash的8bit数据位相连,作为数据总线。同样,FPGA的I/O端口97-104与FT245RL中的8bit数据位相连,成为另外一条数据总线。Flash的片选端CE,命令控制端CLE, 地址控制端ALE,写控制端WR,读控制端RE分别和FPGA的I/O端口56、54、55、61、60相连接,而FT245RL中4个与数据传输有关的控制信号则与FPGA的I/O端口90-93相连。控制信号的方向参照图2中箭头方向。

图2 USB接口原理框图

2 软件设计

2.1 状态机设计

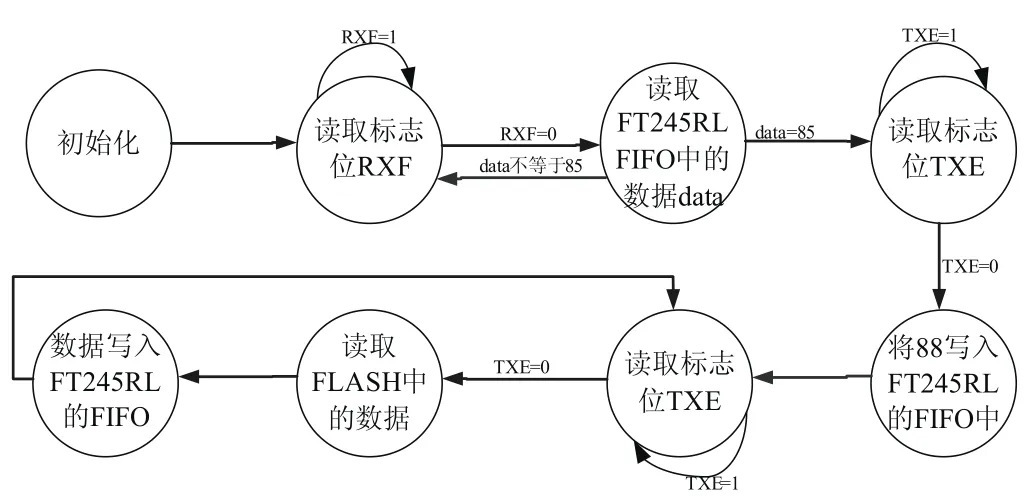

本文采用有限状态机的方法来设计FT245RL控制器,其状态转换和控制输出如图3所示。在图3中,系统上电复位后进入初始化状态,然后CPLD就开始不断的去读取FT245RL的RXF端口并判断其是否为零,当RXF=0时就说明上位机有数发过来然后系统进入读数状态,当读取的数据和上位机软件给出的数据(这里设定这个数为85)一致时系统就开始不断读取FT245RL的TXE端口并判断其是否为零,当TXE=0时就说明可以向FT245RL的FIFO中写数了,进入写数状态首先应写入和上位机约定的数据(这里设定为88)从而表示上位机发出的数据已经正确的收到上位机和测试系统已经建立起正确的通信,接下来就可以循环读取Flash中的数据并依据FT245RL的TXE端口依次将数据写入FT245RL的FIFO中。

图3 FT245RL控制器状态机状态图

2.2 上位机程序设计

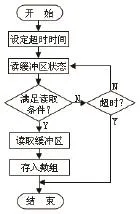

计算机端程序采用VB6.0编写,通过调用FTDI提供的动态链接库,进行读、写函数等的调用与操作。当FT245RL初始化完成后,就可以进行数据发送和接收。发送数据时,将数据赋值到发送数组,调用发送函数FT_Write,然后判断函数返回值是否等于1。若为1,说明数据发送成功;若不为1,则需要重新发送。接收数据时,首先需要设定接收超时时间。然后,调用FT_Getstatus函数读取接收缓冲区的状态,判断接收队列中是否有数以及是否满足设定的读取字节数阈值。若满足读取条件,则调用读数函数FT_Read,读取当前缓冲区的数据并存入数组;若不满足读取条件,则一直等待,直到满足读取条件或产生接收超时。若产生超时,程序自动跳出接收程序,避免陷入死循环。接收流程如图4所示。

图4 上位机接收流程图

3 实验结果及分析

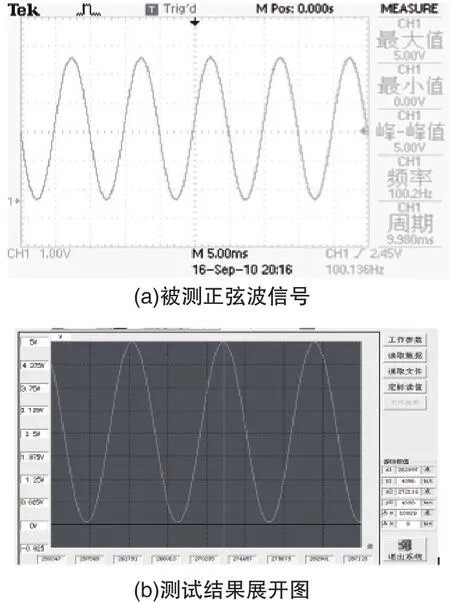

为了验证本数据传输控制器及测试系统的可行性,系统被用来采集了一路最大值5V,最小值0V,频率为100Hz的正弦信号,如图5(a)所示。测试系统在采样频率为1MHz的情况下,测试结果在FT245RL数据传输控制器的控制下通过USB接口传输到上位机的结果如图5(b)所示。从图5(b)可以看出一个周期内采样点数为10000,这正好吻合了测试系统的采样频率,测试结果幅值和数据量上也和被测信号一致,而且数据曲线平滑噪声较小。

图5 正弦波测试结果

4 结论

在FPGA内部准确的实现针对FT245RL的数据传输控制器从而使得整个存储测试系统在一片FPGA的控制下得以实现,经过实验证明该存储测试系统实现简单,调试容易、性能稳定可靠、最高采样率可达1M/s。

[1]何瑛,朱明武,李永新.膛内多路瞬态信号存储测试技术[J].仪器仪表学报,2001,22(3):134-136.

[2]文丰,乔建忠,李艳.高过载存储测试中抗过载技术的研究[J].传感器与微系统,2009, 28(9):31-33.

[3]董健,蒋建伟,万丽珍.CPLD与单片机在超压存储测试系统中的应用[J].测试技术学报,2005,19(1):44-47.

[4]张海峰.基于FPGA的数据采集系统的SOPC实现[D].郑州:郑州大学,2005.

[5]钟雷.基于FPGA的通用存储器控制器的系统设计与实现[D].上海:复旦大学,2009.

[6]戴向华.USB原理及其在数据采集中的应用[J].计算机工程与设计,2004,25(5):840-843.

[7]吴振宇,常玉宝,冯林.基于FPGA和USB2.0的高速数据采集系统[J].仪器仪表学报,2006,27(z1):125-127.

[8]苏彦锋,衣晓峰,周荣政,等.USB外设接口的FPGA[J].仪器仪表学报,2002,22(19):125-127.