基于FPGA的数字电子系统容错机制的研究

杨 燕,黄宇平

(1.广西师范学院数学科学学院,广西 南宁530001;2.广西机电职业技术学院电气工程系,广西 南宁 530007)

随着数字电路系统设计的规模增大,复杂性提高,系统运行的可靠性问题日益引人注目。特别在一些特殊的应用场合,例如电子设备需要长期工作且运行环境恶劣、技术人员又无法及时提供维修的场合,对于系统自适应能力的要求就更为迫切。人们希望在故障发生后,系统能够自动检测出错误,并启动系统的自修复机制以完成错误的修正,从而维持系统的正常运行。

基于SRAM编程的FPGA不仅使在系统可编程(ISP)和在系统可重新编程(ISR)得以实现,而且使FPGA动态可重构技术得以创立。基于FPGA的数字电子系统的动态重构特点,为系统故障特别是不可预料故障的动态修复,提供了实现的可能性。

对于随机故障的具有容错能力的数字系统的研究,是容错系统的一个不可忽视的主要研究方向,目前国内已有学者提出利用基于SRAM技术的现场可编程门阵列FPGA,通过芯片重新布局布线及网表数据重载,实现逻辑功能的现场重构和修改,而正是这种系统内的动态重构特点,为系统内的随机故障,特别是对于不可预料故障的动态修复,提供了实现的可能性。

而国外则另辟蹊径,从硬件电路的角度出发,尝试将进化算法与可编程器件有机结合起来,构成了“仿生硬件”(进化型仿生硬件和胚胎型仿生硬件)。进化型仿生硬件,可以通过进化来或得满足给定要求的电路和系统结构,进而使系统可自动地、实时地调整其内部结构,以适应内部条件和外部环境的改变。而胚胎型仿生硬件,则能像生物一样自繁殖和自修复。

本文针对目前国内外在自适应、自修复领域的研究成果及研究方向,主要分析FPGA电子器件实现容错的基本原理,方法并对该技术的发展趋势给出了展望。

1 系统可重构

提高系统可靠性的基本方法,有故障预防和故障容错。

故障预防,是抑制故障的产生;而容错,则是指系统运行出现错误时,依靠内部容错机制仍能继续保持其正常工作。

容错系统最基本的设计方法,是利用冗余的逻辑资源来屏蔽故障对系统的影响。但对于不可预料的故障,根本无法用若干有限模型去描述,传统的冗余模块的容错设计也无能为力。

对于随机故障的具有容错能力的数字系统的研究,是容错系统的一个不可忽视的主要研究方向。实时电路重构,是解决随机故障容错的最佳方案。实时电路重构,就是在电子系统的工作状态下,动态改变电路的结构。这主要是通过对系统中的可编程器件,进行重配置或部分重配置来实现的。利用这一技术设计的可重构系统,能轻而易举地将系统软件实现和系统硬件实现的优点合二为一。

在可重构系统中,硬件信息(可编程器件的配置信息)也可以像软件程序一样,被动态调用或修改。这样既保留了硬件计算的性能,又兼具软件的灵活性。形象地说,可重构系统就是把硬件软件化,使硬件可以像软件一样被使用。

2 可重构的分类

2.1 按重构粒度大小分类

可重构系统的重构方式,按重构粒度的大小不同,可分为模块级重构和元件级重构。

(1)模块级重构。此时,将改变某一个或若干个子模块的结构,不仅需要电路逻辑的改变,连线资源也需重新进行分配。通常此类重构时,系统可能需要系统暂停工作,故存在灵活性不足的缺陷,使得此类重构不适合应用于在线系统自修复的场合。

(2)元件级重构。在重构时仅改变若干元件的逻辑功能。通常情况下,重构时连线资源的分配状况不作修改,重构时系统可以边重构边工作。这种重构系统设计复杂,但灵活性大,能充分发挥出硬件运算的效率,较适合应用于在线修复。

2.2 按重新配置方式分类

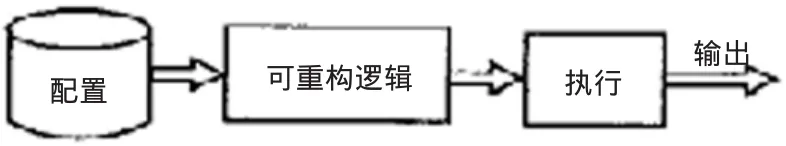

可重构系统还可按照重新配置方式的不同,分为动态可重构(图2)和静态可重构(图1)。

(1)静态重构。必须中断当前系统运行任务,来进行新的数据流配置,主要针对具有重构能力但配置数据时速度较慢的器件。

图1 静态重构系统

(2)动态重构。在改变电路的功能同时,仍然可以保证电路的动态接续。动态重构可以使FPGA内的硬件资源实现分时复用,提高了FPGA资源的使用率。

图2 动态重构系统

2.3 按实现重构面积分类

可重构系统还可就其实现重构的面积不同,分为全局重构和局部重构。

(1)全局重构。对FPGA器件或系统能且只能进行全部的重新配置,在配置过程中,计算的中间结果,必须取出存放在额外的存储区,直到新的配置功能全部下载完为止,重构前后电路相互独立,没有关联。

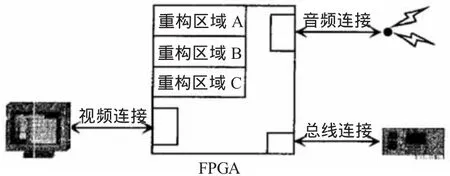

(2)局部重构。对重构器件或系统的一部分进行重新配置,而在此过程中,其余部分的工作状态不受影响。这种重构方式减小了重构范围和单元数目,从而可以大大缩短重构时间,具有相当的优势。图3给出了一种典型的FPGA部分动态重构的应用示意图。

图3 局部动态可重构应用

3 主要技术特征及典型原理

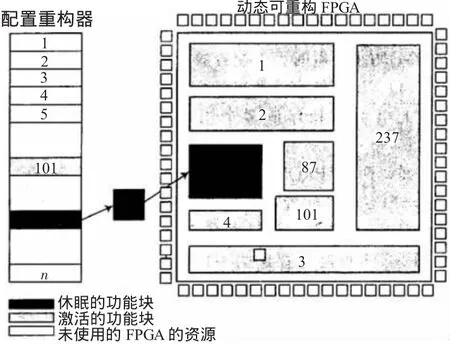

FPGA局部动态可重构技术的特征,就是将整体按功能或按时序分解为不同的组合,并根据实际需要,分时对芯片进行局部动态重构,以较少的硬件资源实现较大的时序系统整体功能。图3给出一种典型的FPGA局部动态可重构。

由图4可以看出,在外部逻辑的控制下,可以实时动态地对芯片逻辑实现局部重构。通过控制布局、布线的资源,实现系统的动态重构。

图4 典型的FPGA局部动态可重构原理图

4 FPGA动态可重构的实现

Xilinx的Virtex系列支持局部重构。Virtex-2和Virtex-2 Pro重构存储介质可被看作是长方形的bit阵列(array),该阵列由1 bit宽、整个阵列高的垂直帧(frame)组成,该帧(图5)是存储介质局部可重构的最小单元。

图5 Virtex FPGA重构存储帧

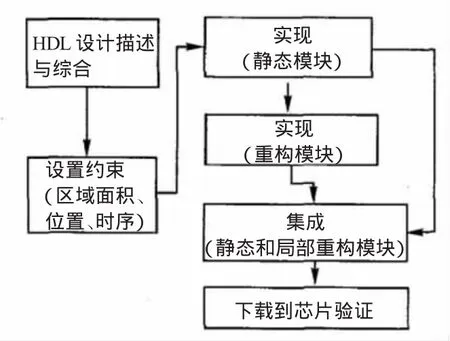

EAPR (Early-Access Partial Reconfiguration)是Xilinx推荐的一种DPR(dynamical Partial Reconfiguration)设计方法,基于EAPR的动态可重构方法的设计流程(图6)包括:

4.1 硬件描述语言设计和综合

(1)顶层模块设计和综合。顶层模块描述必须只包括使用黑盒子实例化的I/O、时钟缓存、静态模块、局部重构模块、总线宏以及信号声明;

(2)静态模块的设计与综合。静态模块是在动态可重构执行时间状态不变的模块,因此这一步与传统硬件描述语言设计方法一样,但是静态模块不能包括任何时钟和复位逻辑,在综合时不加入I/O缓存;

(3)每个可重配置子模块的设计和综合。每个局部重构子模块要保证没有时钟逻辑,并且具有相同的端口定义和实体名字。

4.2 设置约束

除了传统的I/O端口位置约束,还要对顶层的时钟缓存添加位置约束,对可重构区域添加面积约束,还可以添加布局布线和时序约束,在可重构区域的边界添加总线宏的位置约束。

4.3 实现静态模块

实现静态模块产生的信息,将用于可重构模块的实现阶段,所以必须首先完成静态模块的实现。实现静态模块包括3个步骤:转换、映射和布局布线。

4.4 实现每个可重配置模块

在静态模块实现之后,每个局部重构子模块必须分别进行实现。

4.5 bit流合并

局部重构设计流程的最后一步,是合并顶层、静态模块和重构模块。在合并这一步中,从重构模块和静态模块中建立一个完整的设计。

4.6 验证

下载bit流文件到开发板上运行验证。

图6 EAPR的动态可重构方法的设计流程

5 可重构技术的发展趋势

随着FPGA的发展,超大规模、高速低耗的FPGA不断推陈出新,新一代的FPGA集成了中央处理器或数字处理器内核,可在同一片FPGA上进行软硬件协同设计。FPGA的动态局部重构技术有以下发展趋势。

(1)重构粒度单元更小。目前最新的Xilinx Virtex-4系列和Virtex-5系列的最小重构单元做的更小,其每个最小单元只有13l2 bit,可以在垂直方向设计多个动态重构模型,提高设计的灵活性。

(2)FPGA实时重构。随着片上操作系统技术的成熟,越来越多的FPGA片内包含着嵌入式处理器核,通过嵌入式处理器核利用内部配置端口,不仅可以使动态重构设计更加灵活,而且可以提高动态重构的下载速度,这种特性对于实时任务的处理尤为重要。例如,Xilinx FPGA推出了内部配置接口ICAP(Internal Reconfiguration Access Ports),该端口具有两条并行的输入输出数据通道。当ICAP接口和片内处理器相互配合,就可以设计一个具有自控能力的动态重构系统。

6 结束语

国外动态可重构研究比较多,如自重构可适应FIR滤波器的设计和软件无线电设计等。国内动态可重构研究相对较少,目前动态局部可重构技术发展的水平,远没有达到成熟的地步,但是动态局部可重构技术自身具有的优势,使得这一领域成为FPGA研究的热点问题,相信未来此技术会有广阔的应用前景。

致谢

本研究得到广西师范学院基础研究基金资助。

[1]谷 銮,徐贵力,王友仁,等.FPGA动态可重构理论及其研究进展[J].计算机测量与控制,2007,15(11):1415-1418.

[2]吴冬冬,杨晓君,刘新春,等.一种基于FPGA的可重构计算系统设计[J].计算机工程与应用,2006,42(21):74-77.

[3]罗毅辉,李仁发,熊曙初.可重构计算系统的研究与应用[J].计算机应用研究,2006,23(1):154-156.

[4]覃祥菊,朱明程,张太镒,等.FPGA动态可重构技术原理及实现方法分析[J].电子器件,2004,21(2):277-282.

[5]蔡启先,蔡洪波,黄晓璐,等.基于的动态可重构体系结构[J].计算机应用,2006,26(7):1741-1743.

[6]Lohn J,Hornby G.Evolvable Hardware:Using Evolutionary Computation to Design and Optimize Hardware Systems[J].IEEE Computational Intelligence Magazine,2006,1(1):19-27.