不同ALU实现方法的功耗研究

孙军凯,蒋安平

(北京微电子技术研究所,北京100076)

1 引言

随着手持设备和电池供电设备的普及和不断发展,设计者对微处理器在功耗方面的要求越来越高。低功耗微处理器的设计可以从不同的抽象层次采用相应的低功耗设计技术进行,也可以通过分别对微处理器的各个组成部分进行功耗优化来实现。ALU是进行数据处理的场所,是微处理器的重要组成部分,其工作频率直接决定了微处理器的性能。由于在几乎100%的时间里都处于工作状态,所以ALU是微处理器中消耗能量最多的组成部分之一,也是最容易形成热点的地方[1]。因此,设计低功耗的ALU可以显著减小微处理器的功耗。

由于ALU的结构与功耗、延迟和面积有着复杂的联系,所以采用不同结构的ALU也通常会有不同的功耗。根据资源复用程度的不同,ALU结构主要有以下三类:①复合结构[2-3];②加法器独立结构[4-5];③树形结构和链式结构[6]。对三类 ALU 结构的详细描述将在文章的第三部分进行。

基于三种不同结构,设计了一个8比特的执行加、减运算和逻辑运算的ALU,并且用三种常见的ALU结构分别予以实现。通过对三种ALU结构的比较,结合功耗分析的结果,我们得到了采用复合结构的ALU更有利于低功耗设计的结论。

2 ALU设计

ALU是一个从寄存器堆、写回总线或者数据存储器取操作数,并对操作数进行处理的单元。ALU的设计主要包括三个方面:功能定义、核心加法器设计以及结构设计三个方面。由于主要关心不同的ALU结构对功耗的影响,所以这里主要进行的是结构设计。

2.1 ALU 功能设计

通过研究发现通用微处理器的ALU执行的指令都可以使用加、减、与、或、非等基本运算来完成。为了研究ALU结构对功耗的影响,设计了一个执行10种基本运算的8比特ALU,并分别用三种结构来实现它。表1列出了所设计的ALU执行的运算和操作。

表1 ALU的功能表

2.2 核心加法器

加法器是运算电路的核心,通常处于ALU的关键路径上[4]。设计低功耗高速加法器单元是获得低功耗高速运算电路的关键。

行波进位加法器(Ripple Carry Adder,RCA)是最早的最基本的加法器,其延时正比于加法器的位数N,面积也正比与加法器的位数N。超前进位加法器(Carry Look-ahead Adder,CLA)凭借着速度快和模块化的优势而被广泛采用,其延时正比于加法器位数N的对数logN,面积正比于N·logN。除此之外,相同位数的CLA功耗也要比进位选择加法器(Carry Select Adder,CSL)和进位保留加法器(Carry Save Adder,CSA)低[7]。

N位全加器中,第k位的进位输出与第k位的加数、被加数以及第k-1位的进位输出之间存在如下关系:

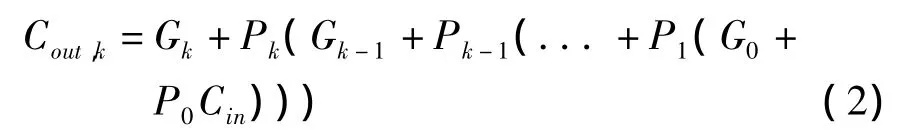

CLA通过消除行波进位来加速加法运算,因此CLA中Cout可以表示为:

其中Pk表示第k位的进位传播信号,Gk表示第k位的进位产生信号。

由于公式(2)所建议的超前结构只在N值较小(N≤4)的时候有效[7],因此可以采用两个4比特的超前进位加法器串联设计来实现ALU中的8比特全加器。

3 三种典型的ALU结构

复合结构ALU将执行算术运算和逻辑运算指令的电路复用起来,用几个控制信号来控制电路执行相应的指令操作。加法器独立ALU开始只考虑用单独的加法器实现所有算术运算指令,然后再加上独立于加法器的其他电路以实现所有逻辑运算指令。这种ALU结构中,实现算术运算的电路和实现逻辑运算的电路相互独立。树形结构和链式结构ALU是把一些功能单元组织成树状或者链状,每一个功能单元执行某一种算术运算或逻辑运算,利用这些功能单元的组合来实现所有的算术运算指令和逻辑运算指令。

3.1 复合结构

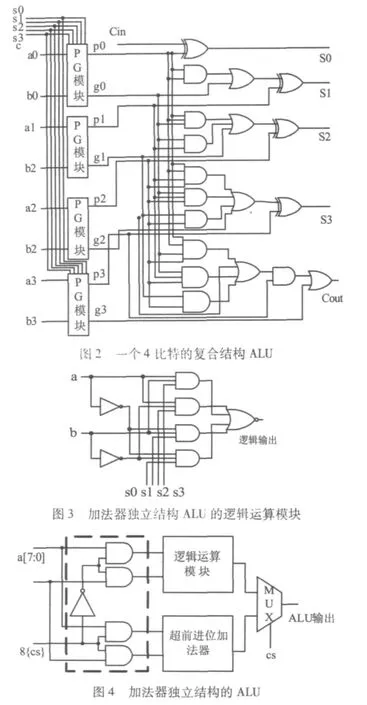

在复合结构ALU中,通过修正核心加法器的进位传播(Propagation)和进位产生(Generation)模块,使进行算术运算和逻辑运算的电路得以复用。图1显示了修正后的P G模块。图2显示的是一个4比特的采用复合结构的ALU。

图2中,s0、s1、s2和s3是控制P G模块功能的控制信号,c是选择ALU进行算术运算或逻辑运算的选择信号。

由于ALU中8比特的加法器是由两个4比特CLA串联组成,所以8比特复合结构的ALU也采用两个图2所示的4比特ALU串联组成。

3.2 加法器独立结构

这种结构中,一个CLA用于执行算术运算,一个独立于加法器的模块用于执行逻辑运算。逻辑运算模块的电路如图3所示。加法器独立结构的ALU如图4所示。出于低功耗考虑,我们对加法器独立结构的ALU采用操作数隔离技术,如图4中虚线框所示。

3.3 链式结构

根据文献[6],链式结构ALU比树形结构ALU有更小的面积和潜在的更快的速度。此外,对于链式结构ALU,功能单元在链中位置的不同也会导致功耗的不同。因此,这里我们选择链式结构ALU作为研究对象。基于Dhrystone基准测试程序,通过改变功能单元在链中的位置,我们找到一种功耗最低的链式结构ALU,如图5所示。

出于低功耗考虑,我们对链式结构ALU采用操作数隔离技术,在两个操作数后面分别增加了一个隔离单元,如图5中虚线框所示。

图5 链式结构ALU

4 仿真结果分析和讨论

使用Verilog HDL硬件描述语言在RTL级对该8比特ALU进行描述,用Modelsim仿真软件进行功能仿真,完成ALU的设计。再用Synopsys公司的Design Compiler对设计好的RTL级代码进行逻辑综合(采用SMIC 0.18μm工艺)生成该8比特ALU的门级网表。为验证综合正确与否这里需要对门级网表进行门级的功能仿真,此时需要生成记录节点翻转信息的VCD文件。最后用Synopsys公司的Prime Power功耗分析工具,采用基于事件的功耗分析方法进行功耗分析。

在100MHz的频率下执行Dhrystone基准测试程序时,三种不同结构ALU的功耗、延时和面积如表2所示。从表中可以看出,复合结构ALU具有最小的功耗和最小的面积。

表2 不同结构ALU的功耗、延时和面积

比较图1和图3,可以发现复合结构中修正后的P G模块仅仅比加法器独立结构中的逻辑运算单元多了一个3输入的“或”门。但是在加法器独立结构中,CLA需要一个“与”门和一个“异或”门来产生P G信号。此外,加法器独立结构ALU需要一个多路选择器来选择合适的输出。由于多路选择器处于关键路径的末端,其开关活动性比ALU的其他部分都要大。因此,加法器独立结构ALU的功耗比复合结构ALU的功耗大就不足为奇了,面积也是如此。仿真的结果也印证了这一点。

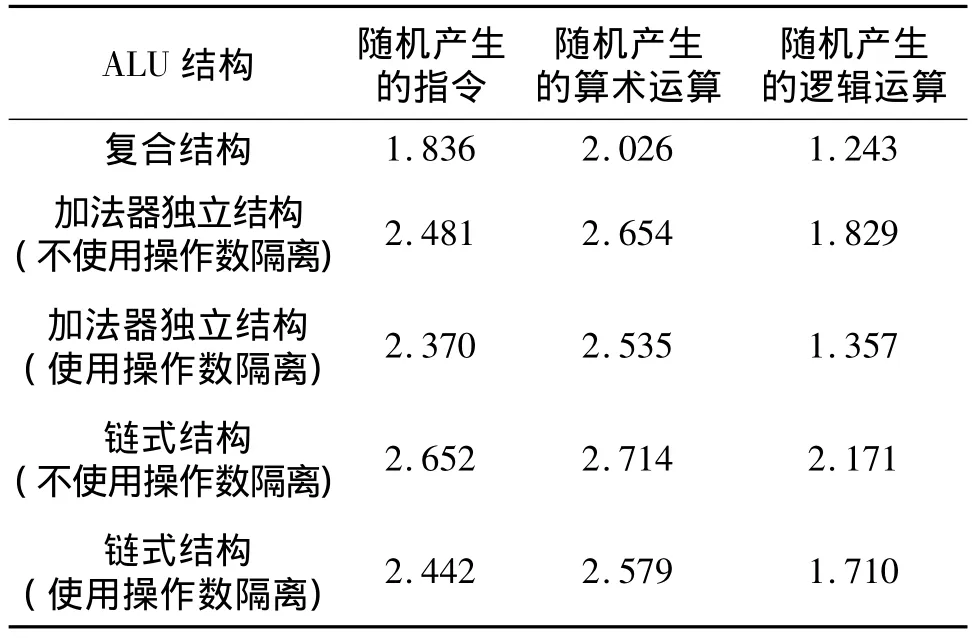

对比图3、图4和图5,可以发现加法器独立结构ALU与链式结构ALU的不同之处仅在逻辑运算单元。然而由于二者的逻辑运算单元结构差别比较大,很难从直观上判断哪种结构更有利于低功耗设计。应该注意到这里逻辑运算单元的功耗在总功耗中所占的比例是比较小的,所以两者功耗的差别也会比较小。为了探明哪种结构更省功耗,选取另外三组随机产生的测试向量对这三种不同结构的ALU进行功耗分析,其结果如表3所示。

表3 不同结构ALU在不同类型的测试向量下的功耗(mw)

从表3中可以看出,当执行随机产生的操作时与执行Dhrystone基准测试程序时相比,复合结构ALU和加法器独立结构ALU的功耗都有明显的下降。这是因为在Dhrystone基准测试程序中算术运算的比例远比随机产生的指令中算术运算的比例高,而且ALU执行一条算术运算指令消耗的功耗要远比执行一条逻辑运算指令消耗的功耗高。当执行Dhrystone基准测试程序的时候,加法器独立结构ALU的功耗要比链式结构ALU的功耗高,但是当执行随机产生的指令时,加法器独立结构ALU的功耗又比链式结构ALU的功耗少。这是因为链式结构ALU中功能单元的排放顺序是根据Dhrystone基准测试程序来设计的,而不同的测试向量对链式结构ALU功耗的影响是比较大的。

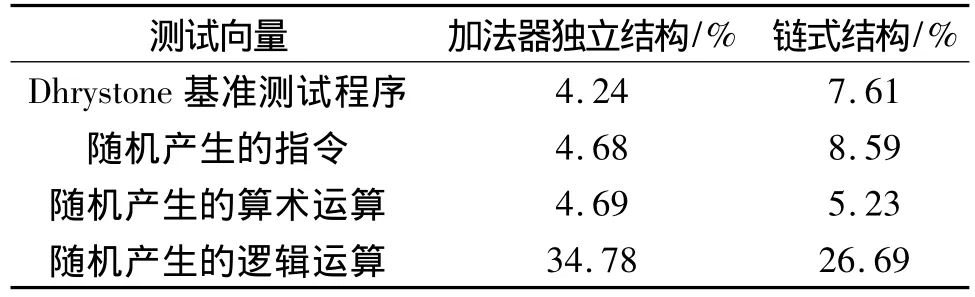

从表2和表3,可以发现采用操作数隔离技术后,加法器独立结构ALU和链式结构ALU的功耗都有一定程度的下降,但是效果并不理想。

从表4中可以看出,这里采用操作数隔离技术对低功耗设计有帮助,但是效果不明显。这是因为一方面ALU一直处于工作状态,另一方面ALU多数时间在执行消耗功耗较多的算术运算指令,再加上隔离单元本身也要消耗功耗,所以能节省下来的功耗是非常有限的。当仅仅执行逻辑运算的时候,由于功耗较大的算术运算单元被隔离,所以此时使用操作数隔离技术有比较好的效果。

表4 操作数隔离技术对ALU功耗的影响

5 结束语

低功耗设计是一项复杂的工程,需要从不同的设计层次进行设计才能达到较好的效果。这里设计一个执行10种运算的8比特ALU,并分别用三种不同的结构实现它。通过对这三种不同结构ALU的功耗分析和结构比较来研究ALU结构对功耗的影响。仿真结果表明:复合结构ALU面积和功耗都是最小的。与其它两种ALU结构相比,复合结构ALU的功耗节省范围是19.38%和33.87%。

[1]Swaroop Ghosh and Kaushik Roy.Exploring High - Speed Low-Power Hybrid Arithmetic Units at Scaled Supply and Adaptive Clock - Stretching[C].2008 Asia and South Pacific Design Automation Conference,2008:635.

[2]David A Patterson,John L Hennessy.Computer organization and design:The hardware/software interface[M].third edition,Elsevier Inc,2005:B -26.

[3]Beom Seon Ryu,Jung Sok Yi,et al.A design of low power 16- B ALU[C].Proceedings of the IEEE Region 10 Conference,IEEE TENCON,1999:868 -871.

[4]Patanjali Prakash,Saxena A K.Design of low power high speed ALU using feedback switching logical[C].2009 International Conference on Advances in Recent Technologiesin Communication and Computing, Kottayam,India,2009:899 -902.

[5]Rajesh Kannan Megalingam,Venkat Krishnan B,et al.Gating and serializing the data path of CPU for low power consumption[C].2009 International Conference on Parallel Processing Workshops,Vienna,Austria,2009:550 -557.

[6]Yu Zhou,Hui Guo.Application specific low power ALU design[C].2008 IEEE/IFIP International Conference on Embedded and Ubiquitous Computing,Shanghai,China,2008:214-220.

[7]Chetana Nugendra,Mary Jane Irwin,et al.Area - Time -Power Tradoffs in Parallel Adders[J].IEEE Transactions on circuit and systems- II,1996:689 -702.

- 微处理机的其它文章

- 视频压缩1/2ME模块设计

- “微处理机全国理事会”邀请函