基于FPGA和USB接口的多通道数据采集系统

王寅超,郑正奇

(华东师范大学 信息科学与技术学院,上海 200241)

数据采集技术在工业测量与控制,自动化测试等领域有着广泛的应用,笔者以多通道测距雷达信号的采集为研究背景,开发了一种以FPGA为核心的多通道数据采集系统,由于FPGA采用硬件描述语言进行模块化编程,在无需对系统硬件做任何调整的情况下便可对系统功能进行修改和升级。

将USB2.0接口作为系统的数据接口,将各通道的采样数据发送至上位机,既保证了采样数据的传输速度,又使该系统具备了即插即用的特性,还可使用VC、LabVIEW等多种程序语言进行上位机程序的编写,提高了软件开发的灵活性。

1 系统组成

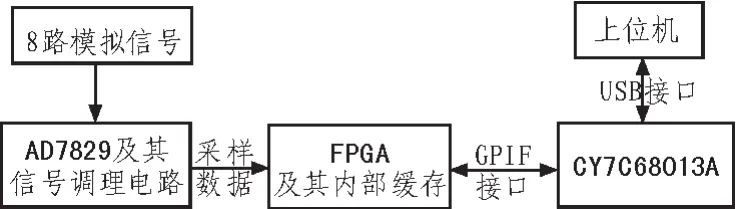

本数据采集系统最多可以对8路模拟信号进行采样,其系统框图如图1所示。

图1 系统框图Fig.1 System block diagram

AD转换器件选用AD公司的AD7829[1],其最高采样率为2 MSPS,采样位数8位,数据接口类型为并口,有8路模拟信号输入并自带模拟开关以及采样保持电路,内部参考电压为2.5 V。

USB接口芯片采用Cypress公司的CY7C68013A[2],内置增强型8 051处理器和USB2.0引擎,向下兼容USB 1.1协议,并具有GPIF接口可与多种外设相连。使用keil3作为USB固件的开发平台。

FPGA选择Altera公司的EP1C12Q240C8[3],具有两个PLL,12 060个逻辑单元,可以实现复杂的逻辑功能,并能构建一定深度的缓存空间。FPGA的程序使用Verilog硬件描述语言在QuartusII平台下编写。

2 多通道数据采集控制和数据缓冲

本设计中通过FPGA产生AD7829的采样控制逻辑[4],并通过在FPGA中构建一定深度的FIFO来实现采样数据的缓冲。

2.1 AD采样控制逻辑

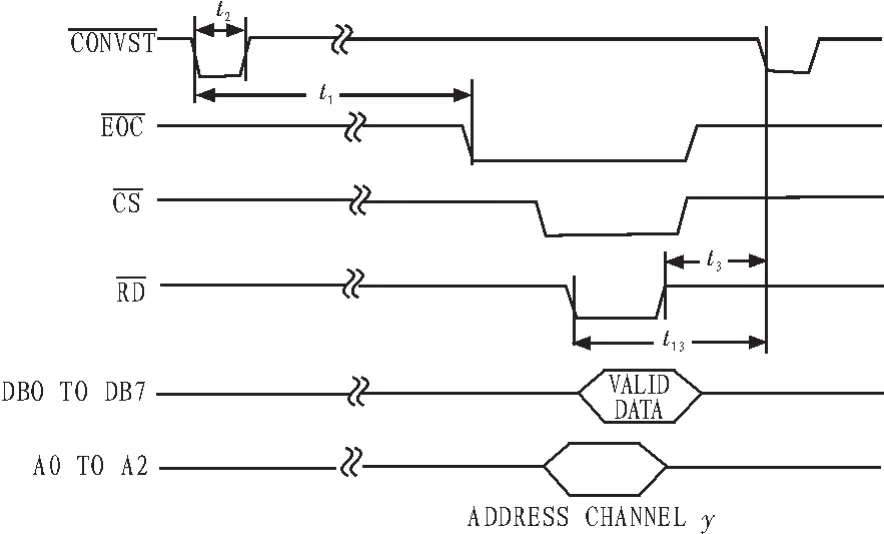

AD7829的采样逻辑如图2所示。

图2 AD7829的采样时序逻辑Fig.2 AD7829 parallel port timing diagram

FPGA对于AD采样的控制逻辑按照图2的时序要求来设计[5],主要分为两个模块:带PWM功能的采样时钟发生模块和采样过程控制模块,具体工作过程如下:首先由FPGA产生频率为2 MHz、占空比为80%的采样频率来启动AD7829的模数转化,然后FPGA在每次接收到AD7829反馈的转换完成信号EOC后,分别控制CS,RD的状态,从而得到每次转换的有效数据。

在每次转换过程中FPGA通过控制AD7829的模拟开关控制位A0-A2(二进制000-111分别对应AD7829的1-8通道)来选择当前转换的模拟通道,在本设计中,FPGA在每次模数转换完成后对模拟开关控制位进行加1操作,从而实现了对8通道信号的轮流采集。由于本系统采样时钟为2 MHz,因此8路信号的单路采样率为250 KSPS。若要对采集的通道总数进行更改,只需对FPGA逻辑中控制通道模拟开关的部分稍作修改即可。

AD采样逻辑的FPGA仿真时序如图3所示。

图3 FPGA仿真时序Fig.3 FPGA simulation timing diagram

2.2 数据缓冲

利用QuartusII提供的IP核,在FPGA中构建一块异步FIFO作为采样数据的缓存器[5]。在每次得到的有效采样数据后,FPGA将8位转换数据与其对应的通道号码 (A0-A2)进行拼接后存入该异步 FIFO中(见图3中的data_add),等待通过USB接口发送到上位机进行进一步的数字信号处理。

在本设计中异步FIFO的写入时钟 (见图3中的fifowdclk)根据AD7829的采样逻辑而产生,以保证写入时钟上升沿到来时,AD7829的数据线处于有效数据状态,因此其频率与系统的采样频率相同,也为2 MHz,而异步FIFO的读取时钟高达48 MHz(由CY7C68013A的 IFCLK提供),因此只要设置合适的FIFO深度和读取时机就可以避免出现异步FIFO溢出的情况,从而确保多通道采样数据能够被及时发送至上位机。

3 USB接口设计

本设计中采用USB2.0接口传输AD采样得到的数据,USB2.0接口在高速模式下的最大传输速率高达480 Mb/s,完全满足本数据采集系统对传输速率的要求,且能够通过相应的设备驱动进行自动配置,实现即插即用。

USB接口芯片选用CY7C68013A,在FPGA数据采集模块和上位机之间建立通信。

3.1 通用可编程接口

通用可编程接口(GPIF)是CY7C68013A内部端点FIFO的主控制器[6],它的作用是将USB端点FIFO与外设FIFO进行逻辑连接,从而控制数据的读写操作。

在本设计中,CY7C68013A与FPGA通过GPIF接口相连,如图4所示,其中FIFO_RCLK和REN#分别是构建在FPGA内部的异步FIFO的读取时钟和读使能信号,具体工作过程如下:通过AD采样得到的有效数据存储在FPGA内的异步FIFO中,当FIFO达到半满状态时,FPGA产生一个Data_Ready信号通知CY7C68013A通过GPIF接口将这些数据读入其USB端点的内部FIFO中。

图4 GPIF硬件连接Fig.4 GPIF hardware connection

3.2 USB固件

USB固件通过Keil3软件进行编写,Cypress公司提供固件工程的基本架构[7],在多数情况下,只需在此架构中添加功能代码就可以实现相应的功能。

而对于包含GPIF接口控制的固件设计来说,还需要使用Cypress公司提供的 GPIF Designer软件,根据不同外设的特定时序要求,对GPIF接口的读写时序进行设置,生成GPIF波形文件并导出相应的.C文件,添加到固件工程中,并对其进行调用,以实现GPIF波形的设计功能。

在本设计中,固件程序检测FPGA的Data_Ready信号,一旦该信号为高电平则通过启动预先设置好的GPIF波形逻辑,将FPGA内异步FIFO的数据读入USB端点的FIFO中,并进行发送,实现了AD采样数据向上位机的传输。

3.3 上位机程序接口

通过Cypress公司提供的调试软件Cypress USB Console,可对CY7C68013A进行固件下载和简单的调试,同时此软件还提供适用于CY7C68013A的驱动程序,以及丰富的API函数,使用VC编写上位机程序的时只需将CyAPI.h和CyAPI.l ib添加到MFC工程中[7],便可直接调用这些API函数,对USB接口的数据读写操作进行控制,从而大大降低了编写上位机程序的难度和周期。

此外,还可以利用LabVIEW的VISA软件,根据固件中配置的VenderID和ProductID直接生成适用于LabVIEW程序的USB驱动,从而在本数据采集系统和LabVIEW之间建立通信,直接利用LabVIEW编写上位机程序。

4 结 论

本系统使用FPGA控制数据采集和缓存,以USB2.0作为数据传输接口,实现了单路最高采样率达250 KSPS(8路情况下)的多通道数据采集和发送功能,经实验验证可以对多路测距雷达信号进行采集。

同时,该系统也具有较强的通用性和扩展性,通过使用采样率和采样精度更高的AD转换器件,并对FPGA逻辑进行升级,便可使其适用于更为广泛的数据采集场合。

[1]Analog Device.AD7822/AD7825AD7829 datasheet[EB/OL].(2006).http://www.analog.com/static/imported-files/data_sheets/AD7822_7825_7829.pdf.

[2]Cypress Semiconductor.EZ-USB FX2 Technical Reference Manual [EB/OL].[2011-09-15].http://www.cypress.com/docID=27095.

[3]Altera Corporation.Cyclone Device Handbook[EB/OL].[2011-09 -15].http://www.altera.com.cn/literature/hb/cyc/cyc_c5v1.pdf.

[4]王金明.数字系统设计与Verilog HDL[M].北京:电子工业出版社,2009.

[5]于亚萍,钱建平.基于FPGA数据采集系统的研究[J].工业控制计算机,2007,20(7):33-34.

YU Ya-ping,QIAN Jian-ping.Data acquisition system research based FPGA [J].Industrial Control Computer,2007,20(7):33-34.

[6]荆蕾,黄惟公,徐鹏,等.基于GPIF的高速数据采集方案设计[J].仪表技术,2007(12):23-24+27.

JING Lei,HUANG Wei-gong,XU Peng,et al.A design of high speed sampling based on GPIF[J].Instrumentation Technology,2007(12):23-24+27.

[7]李英伟,王成儒,练秋生,等.USB2.0原理与工程开发[M].2版.北京:国防工业出版社,2007.