一种固态飞行参数记录仪的研制

韩勇豪,王少云

(1.南京航空航天大学 电子信息工程学院,江苏 南京 210016;2.南京航空航天大学 无人机研究院,江苏 南京 210016)

机载飞行数据记录仪常被称作黑匣子(FDR),它是记录飞机飞行过程中各种状态参数的高性能机载电子设备。能在飞机飞行过程中实时监测并记录飞机飞行状态及各种机载设备的性能和使用情况。飞行完毕后可将存贮在记录介质上的数据进行下载回放,以便对其研究,可为飞行试验,飞机维护和改进提供强有力的支持。

随着科技的迅速发展,机载飞行数据记录仪也在不断更新换代。20世纪60年代问世的黑匣子(FDR)只能记录5个参数,误差较大。70年代开始使用数字记录磁带,能记下100多种参数,保存最后25 h的飞行数据。90年代后随着超大规模集成电路,微处理器,数据采集技术,数据总线技术的高速发展,机载飞行数据记录仪普遍运用固态记录仪[1]。记录仪的记录容量不断增大,记录数据越来越多,机载飞行数据记录仪除了用于飞行事故分析外,还广泛用于飞行安全,飞行维护管理以及飞行训练管理等。若对飞行数据进行深入挖掘,还可为飞机的地面维护,故障分析,训练效果与作战性能进行深入评估。根据某航空设备的实际需求,笔者将探讨如何研制一种具有大容量、高速数据接口及系统总线接口的飞行参数记录系统。

1 系统组成

笔者所设计的飞行参数记录仪具备以下功能:

1)采用机载系统各种数据总线的能力 传统飞行参数记录仪总线有RS422、RS485及ARN1C429,本系统采用成熟的RS422总线作为系统总线。

2)具备大存储容量 现代飞行参数记录仪普遍采用固态存储介质存储飞行数据,固态存储介质的种类繁多,常用的固态存储介质包括:SDRAM、NORflash、NANDflash、CF 卡等。与其他大容量固态存储介质相比,NANDflash具有存储方式简单、成本低并且可以通过串联或并联来增加数据容量等特点。因此,本系统采用NANDflash作为飞行数据记录仪的存储介质。

3)便利的数据导出接口 传统的数据导出接口常采用RS422作为与PC机的通信接口,但其具有数据传输速率低,错误概率高等缺点。结合实际应用需求,笔者采用USB接口作为与PC机的通信接口,使得本系统可与其他系统轻松实现数据交换和共享,解决了以往飞参数据卸载过程复杂,卸载时间长的缺点。系统框图如图1所示。

图1 飞行参数记录系统框图Fig.1 Block diagram of flight parameter recording system

本系统主要模块有:SRAM缓存模块、大容量数据存储模块、USB数据接口模块。

SRAM缓存模块缓存飞控计算机通过RS422总线传送至FPGA的各类飞行参数,总线数据经过缓存后由FPGA控制写入大容量数据模块中。大容量数据模块采用NANDFlash串联方式,共串接9个NANDFlash,使整个固态飞行参数记录系统容量达到72 G。当完成数据记录后可将固态记录仪与PC机相连,通过USB接口进行数据卸载、处理及显示。

2 芯片选择

本系统所涉及的存储芯片采用三星公司的NANDFlash芯片K9F8G08U0M。它的外部接口速度为40 MHz,接口位宽为8位。每个芯片包含4 096块,每块包括64页,每页共有4 224字节,总存储容量为8 G[2]。

核心控制芯片采用ALTERA公司的EP1C6Q240C8N,它有着丰富的触发器和IO口,非常适合作为NANDFlash阵列的控制器。

USB数据接口采用USB2.0协议,它向下兼容USB1.1协议,数据的最高传输速率提高到 480 Mb/s,为了满足USB传输速度较高的需要,选择Cypress公司的内置USB接口微控制器芯片CY7C68031作为USB芯片,芯片内部集成了一个具有8.5 kB片上RAM的增强型8051单片机、4 kB FIFO存储器、通用可编程接口(GPIF),串行接口引擎(SIE)和USB2.0收发器[3]。

采用IS61LV25616芯片作为SRAM缓存芯片,其具有4 M容量且读写方便,适合作为双缓存RAM使用。

3 重要模块设计

3.1 SRAM乒乓缓存

由于RS422总线速率比FPGA写NANDFlash速率低,为了速率匹配,采用SRAM进行双缓存处理。将4 M字节的SRAM分为2块,每块为2 M字节。首先将RS422总线传送来的数据存入其中一块中,数据写满后设置满标志,FPGA读取SRAM中的数据,并写入NANDFlash后清除该标志,两块RAM交替进行,保证数据的读写操作。SRAM兵乓缓存读写如图2所示。

3.2 NANDFlash动态坏块管理策略

NANDFlash内部有随机分布的坏块,需建立坏块信息管理表,对NANDFlash的操作都要基于此坏块信息统计表[4]。本文提出一种动态坏块管理思想屏蔽NANDFlash中出现的坏块。

图2 SRAM乒乓缓存流程图Fig.2 Flow diagram of SRAM ping-pong cache

动态坏块管理算法的思想在于:在对NANDFlash进行擦除、写入操作,当NANDFlash存储空间出现坏块时,采取动态坏块管理算法标记坏块,将坏块放入映射表的坏块区,从系统预留的替换块区选择一个好块,代替坏块进行操作;同时,更新逻辑—物理块地址映射表。

动态坏块管理算法的一大特色在于使用交换块,将所有对已用块的写入操作都改为对交换块的操作,非常有利于NANDFlash存储空间的管理及逻辑—物理地址映射表的更新。

动态坏块管理算法以zone为单位,每512个块划分为一个zone,每个zone建立一张逻辑—物理块地址映射表,并将映射表划分为:

1)数据区 用于存储数据、系统应用程序等,用作数据区的块都是好块。

2)交换块 所有对已用块的写入操作均改为对交换块的写入,交换块同时起着在更新映射表时防止掉电情况发生,保存原始的映射表,在更新NANDFlash中映射表完成后,再将旧表擦除,可以有效地应对掉电情况。

3)替换块 替换块用于当写入块是一个坏块时,可以从替换块中找一个空块,代替坏块进行编程操作,替换块数量可以由软件设定,一般坏块数量不会超过总量的2%。

4)坏块区 坏块区用于存放初始上电扫描发现的坏块以及使用过程中出现的坏块。在映射过程中将坏块放在映射表的最后。

3.2.1 建立坏块统计表

根据所使用芯片的特点,可将NANDFlash划分为8个zone,每个zone包含512个块,统计每个zone的坏块信息。

坏块信息包括每个zone的坏块数量,坏块分布等,是进行坏块标记的依据和地址映射的相关凭证。所以动态坏块管理算法的第一步就是建立每个zone的坏块信息统计表。坏块统计流程如图3所示。

图3 坏块统计流程图Fig.3 Flow diagram of bad block statistics

3.2.2 建立逻辑—物理块地址映射表

地址转换是NANDFlash逻辑驱动需要完成的重要任务之一。动态坏块管理最主要的思想在于:在对zone为单位进行逻辑—物理块地址进行映射时,将整个zone空间划分为数据区、交换块区、替换块区和坏块区。动态坏块管理算法中地址映射与传统地址映射最大的不同就是增加了交换块区和替换块区。

根据所用芯片的特点将交换块数量设为1、替换块数量设为 20、数据区块数量=512-1-20-坏块区数量,其中坏块区数量根据坏块统计表信息所得。

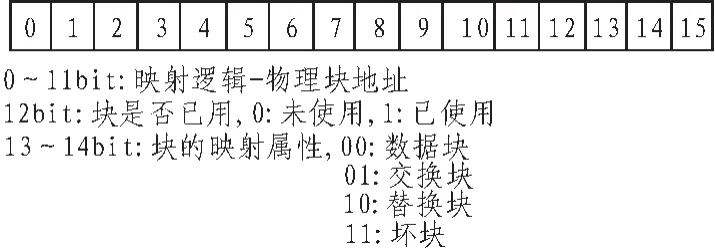

动态坏块管理算法将坏块放到映射表最后,采取每发现一个坏块,对应地址递减的方法实现坏块区的地址映射。为此,建立一个lookuptable[512]数组来映射NAND Flash的一个zone空间,数组元素由两个字节组成,如图4所示。

图4 逻辑-物理地址映射Fig.4 Logical-physical address mapping

建立逻辑—物理地址映射表:

1)初始化 lookuptable[512]数组,将数组元素初始化为0x00;

2)根据坏块统计表信息映射逻辑—物理地址,依次映射数据块、交换块、替换块和坏块;

3)当第 n(n=1~8)个 zone的逻辑—物理地址映射完成后,将此映射表烧写到此zone替换块的第一个物理块上,并将此物理地址烧写入NANDFlash的第一个块的第n(n=1~8)个page中。

3.2.3 更新逻辑—物理块地址映射表

更新逻辑—物理块地址映射表是NANDFlash动态坏块管理的关键环节。当对一个zone进行操作时,主控器件首先将烧写入NANDFlash的逻辑—地址块地址映射表读入RAM中,并根据逻辑—物理块地址映射表对NANDFlash进行读写操作。读写数据发生如下情况时需要更新逻辑—物理块地址映射表:

1)当发生写入、擦除失败时,即产生坏块,从替换块中提取一个块,将坏块的逻辑地址赋给用来代替坏块的替换块,并将替换块的块属性设为“00”,对替换块写入数据,将块是否使用标记设为“1”。同时将坏块的块属性设为“11”,将坏块的逻辑地址对应到地址映射表的坏块区。

2)如果并无发生坏块替换,而将写入数据的块是已用块时,使用交换块代替已用块进行写入操作,并将交换块地址映射到数据块中,擦除此已用块,将其作为新的交换块。

3)最后,当写完一个块后,更新RAM中的映射表,达到动态的映射地址更新。

当对整个zone操作完成后,系统自动更新NANDFlash中存储的映射表,更新映射表也是通过交换块实现,先将旧的映射表存入交换块,再将新的映射表写入NANDFlash的第一块中[5],最后擦除旧映射表,达到了防止掉电情况下映射表丢失的情况。映射表更新如图5所示。

图5 映射表更新示意图Fig.5 Schematic of logical-physical address map update

3.3 USB接口设计

USB接口采用slave FIFO方式与PC机进行通信[6]。USB控制器电路如图6所示。

4 实验结果

根据上述方案实现的机载飞行参数记录系统在实际测试中NANDFlash的读写速度稳定在25 Mb/s,USB的飞行参数卸载速度达到230 Mb/s,能有效实现飞行参数的记录及回放工作,且能有效屏蔽NANDFlash中存在的坏块,大大提高存储数据的有效性。

5 结束语

本文详细介绍了基于固态存储器的大容量机载飞行参数记录仪的实现方法,实践表明该飞行参数记录系统在存储容量及存储有效性方面都达到系统的设计要求。另外,这种飞行参数记录仪为飞行参数卸载提供极大的方便,可在短时间内完成数据卸载任务,从而缩短飞行器再次出动的准备时间,在航空应用中具有良好的前景。

图6 USB控制器电路Fig.6 USB controller circuit

[1]Folio R J,Corp H.Hart C L.Expected applications of the harris solid state compressive recorder(SSCR)to multispectral space-based imageprocessing[J].Porc.SPIE,1997 (3119):125-132.

[2]Samsung.Samsung NAND Flash Memory,Memory Product&Technology Division[EB/OL].(2000-03-15).http://wenku.baidu.com/view/3827f4d7195f312b3169a539.html.

[3]EZ-USB FX2 technical reference manual version 2.0[M/CD].Copress Semionductor Corp data book,2001.

[4]李超,王虹现,邢孟道.高速大容量FLASH存储系统设计[J].火控雷达技术,2007,3(1):82-88.

LI Chao, WANG Hong-xian, XING Meng-dao.Design of a flash storage with high speed and large capacity[J].Fire Control Radar Technology,2007,3(1):82-88.

[5]宁飞.大容量存储中NAND Flash坏块的管理方法[J].电子测试,2010(12):64-68.

NING Fei. Management method of NAND flash ineffectiveness block in high capacity storage[J].Electronic Test, 2010(12):64-68.

[6]汪庆,周凤星.基于USB接口便携式数据采集器的设计[J].微计算机信息,2006,22(31):142-144.

WANG Qing,ZHOU Feng-xing.Designofconvenient instrument of data acquisition based on USB interface[J].Control&Automation, 2006,22(31):142-144.