与ONO反熔丝FPGA匹配的高压器件设计

周云波 于宗光, 封 晴 胡 凯

(1江南大学物联网工程学院,无锡214122)

(2中国电子科技集团公司第五十八研究所,无锡214035)

随着电子技术的发展,航天飞行器越来越依赖于电子系统对航天飞行器实施的控制以及进行数据采集与处理.但是,飞行器内部电子系统对空间辐射的敏感性又威胁着航天飞行器的飞行状态与任务执行,因此对航天电子系统的耐辐射性能提出了更高的要求.存储器是电子系统的重要组成部分,用于存放电子系统的程序和数据信息.辐射引起的存储器数据错误会给电子系统的正常工作带来数据甚至功能的错误,因此抗辐射存储器的研制对宇航电子系统的研发有重要意义[1].基于反熔丝现场可编程门阵列(antifuse FPGA)的反熔丝存储单元具有卓越的抗辐射性能,因而备受航天用户的青睐[2-3].但对于成熟的反熔丝FPGA,除了需要制备具有高可靠性的反熔丝器件外,在电路设计上还需要设计与反熔丝器件特性相匹配的编程电路和读出电路[4].

通常,FPGA中的反熔丝存储单元由1个反熔丝和1个选择管组成.编程选中存储单元时,选择管打开,与编程电路连通.在对反熔丝器件进行编程时,选择管的源极和漏极之间,以及源极或漏极与栅极之间,需要承载较高的编程电压Vpp,因此本文选用高压MOSFET作为反熔丝存储单元的选择管.国外已有基于1.0 μm ONO反熔丝工艺设计生产高压器件的成功范例,其编程电压不低于16 V[4-5].目前,国内也有利用 n-well和 n 管场注作为漂移区,成功将高压nMOSFET嵌入商用标准CMOS工艺中的相关报道,击穿电压在23~134 V之间[6-9].但国内基于ONO反熔丝工艺线并应用于FPGA中的高速高压器件的设计生产尚属空白.

本文采用中国电子科技集团第五十八研究所晶圆的1.0 μm 2P2M ONO反熔丝工艺设计生产高压nMOSFET.对其ONO反熔丝器件的编程特性研究结果显示,有效编程电压为13.5 V,因此本文设计生产的高压MOSFET的最高耐压应大于14 V.此工艺中,常压管栅氧厚度为12 nm,n+注入浓度大约为1×1020cm-3,P型衬底的浓度大约为1×1015cm-3,最小沟道长度为 1 μm,标准 nMOSFET的阈值电压和击穿电压分别为VT=0.76 V,VB=11 V.

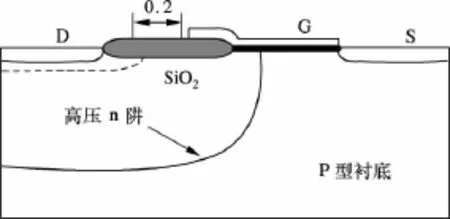

1 高压nMOSFET结构

本文注入HVNwell作为漂移区,高压nMOS管的截面如图1所示,产生一个垂直的和一个水平的pn结.当在漏端加载反向偏压时,横向和纵向耗尽区同时扩展,并在漂移区内产生交叠.漂移区和衬底之间的纵向电场与沟道和漏极之间的横向电场互相作用,使得耗尽区的宽度快速增加,而表面横向电场相对上升缓慢.因此,进一步增加反向偏压时,体内纵向电场将先于表面电场到达临界电场而发生体内击穿,从而提高了器件的整体耐压.并且,此漂移区较薄,浓度较高,在实现高耐压值的同时,保证了更低的导通电阻.图1中,Lc为沟道长度;Lg为n阱纵向结深,采用n阱作为漂移区;Ld为漂移区长度.

图1 高压nMOSFET截面图

2 高压nMOSFET击穿电压

通过对漂移区长度 Ld分别为0.9和1.3 μm的2种高压 nMOSFET进行测试,观察 Ld对高压nMOSFET击穿电压的影响,不同栅源电压VGS下的IV特性测试曲线如图2所示.

图2 高压nMOSFET的IV特性曲线

由图可见,2种高压nMOSFET的击穿电压仅有1 V的差别.这是由于受到阈值电压的限制,n阱纵向结深Lg变化幅度较小,此外漂移区较高的浓度也使得电流通过漂移区时压降较小,因此击穿电压没有显著的变化.此时高压nMOSFET的击穿电压主要由n阱与衬底的pn结的特性决定.适当地调整漂移区的浓度与深度,可以有效地提高器件的击穿电压.

n阱的扩散底部是一个平面,而其侧面则近似为圆柱形曲面,尤其是当扩散结较浅时,扩散窗口4个顶角附近的结面形状近似为球面.柱形和球形结面往往会引起电场的集中,电场强度大于平面结,因而在这些区域中易发生雪崩击穿,导致器件耐压性能降低.为了减小结深对击穿电压的影响,本文采用深结扩散,增大曲率半径,减弱电场集中的现象,从而提高雪崩击穿电压.

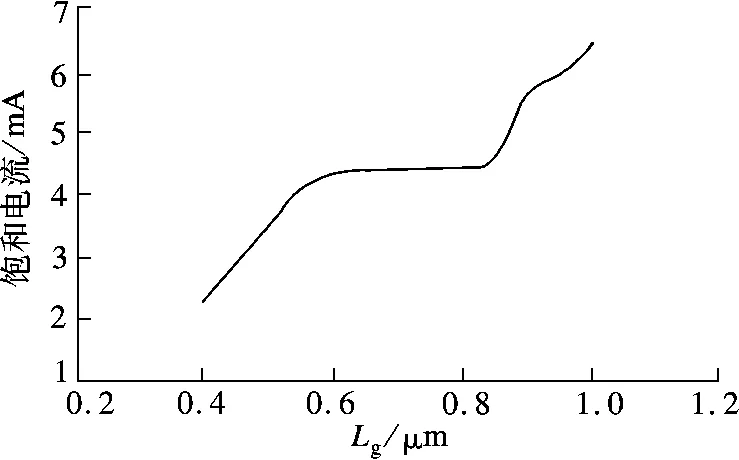

在管子的栅端加载0 V偏置电压进行测试,n阱纵向结深Lg对击穿电压的显著影响如图3所示.测试结果表明,当 Lc=1.2 μm,Ld=1.3 μm时,随着结深由 0.4 μm 增长到 1.0 μm,击穿电压从13.4 V提升到25 V,提升的幅度高达11.6 V.

当Lg=1.0 μm 时得到最大击穿电压25 V,但此时高压nMOSFET的阈值电压仅为0.17 V,不满足要求.因此,最优化的参数值为 Lg=0.6 μm,Ld=1.3 μm,Lc=1.2 μm,在栅极偏压为 0 时,高压nMOSFET的击穿电压为21.8 V.

图3 击穿电压随Lg变化的曲线

3 高压nMOSFET的跨导

MOS器件的跨导gm直接影响器件的速度,是反熔丝FPGA能否提高编程速度的关键因素.但对于高压MOSFET来说,输出跨导gm会受到漂移区串联电阻的影响,即

式中,Gm为有效跨导;Rs为串联电阻.高压器件的漂移区电阻率较高,在栅极偏压的作用下,n漂移区的表面会形成电子的积累区,从反型沟道来的电流首先流入积累区,再扩展进入n漂移区,最后到达漏区.将漏源当作在无限均匀介质中长度为W的2个载流线,假设漏源区结面有效半径为r1和r2,2个中心之间的有效距离为Leff,则n区的串联电阻为

本工艺中,HVNwell采用一次离子注入和高压推进以实现深扩散结.增大pn结的结面曲率半径r,可以增大跨导.

与栅极交叠的长度增加,有效沟长减小,会导致器件阈值电压降低,穿通击穿发生的几率增大,耐压性能下降.为了解决这个矛盾,本设计中将高压注入与栅极多晶之间的间距保持为0.2 μm,截面如图4所示.图中,虚线表示高压n阱注入后推进前的位置,以此说明高压注入与栅极多晶之间的距离.当沟道长度Lc=1.2 μm,漂移区长度Ld=1.3 μm时,漏源电压 VDS=21 V,栅源电压 VGS=VDD,高压nMOSFET饱和电流随纵向结深Lg变化的测试结果如图5所示.

图4 改进后高压nMOSFET截面图(单位:μm)

测试曲线表明,结深的增加提升了器件的饱和电流,从而增加了器件跨导gm值,提高了器件速度.

图5 饱和电流随Lg的变化曲线

4 高压nMOSFET的阈值电压

在管子的漏端加载0.1 V的偏置电压进行测试.图6 为 Lc=1.2 μm,Ld=1.3 μm 时高压 nMOSFET阈值电压随n阱纵向结深Lg的变化曲线.

图6 阈值电压随Lg的变化曲线

在生长局部氧化隔离(LOCOS)的过程中,由于氧在二氧化硅的扩散具有等向性,因此会在靠近刻蚀窗口的氮化硅层底下生长出二氧化硅,产生“鸟嘴”效应[10].“鸟嘴”区与n阱漂移区边缘的相互作用,导致在 Lg=0.4 μm 时,阈值电压上升到0.89 V.当结深足够大使得n阱与沟道的漂移区覆盖了“鸟嘴”区时,源漏之间便会产生一个连续沟道.但是,假如n阱边缘与“鸟嘴”区接近,则高压nMOSFET需要更高的栅压在“鸟嘴”区的拐角产生反型层,或者需要更高的漏极偏压产生到达沟道的耗尽区.

这一现象严重限制了高压nMOSFET的性能.过大的阈值电压会导致器件很难进入饱和区,同时,增加栅压还存在着栅氧击穿的危险.但一味地增大结深又会导致阈值电压过小,器件会在非正常工作状态下开启,导致FPGA产生误编码.

另外,沟道长度Lc的选取也同样影响高压nMOSFET的阈值电压.沟道长度越短,则阈值电压越小.

为了在高压管与常压管之间寻求一个兼容的阈值电压,对沟道进行了一次离子注入,调整高压nMOSFE的阈值电压.调整后的阈值电压如图6所示.同时本设计还需满足 0.6 μm≥Lg>0.4 μm,最小沟道长度 Lc,min≥1.2 μm.

5 高压nMOSFET的其他特性

在进行高压器件设计时,还要考虑源漏之间的穿通击穿问题.为了最优化高压器件性能,穿通击穿电压必须远大于雪崩击穿电压.当高压管的漏端偏压增大时,漏结耗尽区将会扩展到器件的栅极,一旦耗尽区扩大到器件源端时,漏源之间直接穿通,便会出现穿通电流.

一般耗尽区宽度可表示为

式中,εo为真空介电常数(8.85 ×10-14F/cm);εs为硅的介电常数(11.8);q为电子电荷(1.6×10-19C);NA为衬底杂质浓度;ND为n阱浓度.由式(3)可知,器件的穿通电压依赖于衬底和n阱漂移区的杂质浓度,若设定漏端承载偏压为22 V,沟道长度Lc=1.2 μm时,衬底的杂质浓度应大于1×1016cm-3,n阱的注入浓度应在1017~1018之间.

对沟长Lc=1.0 μm的高压nMOSFET进行实验,当VGS=0时,漏电流Id随着漏端电压的上升而增加,但当 Lc≥1.2 μm 时,源漏电流仅在到达雪崩击穿电压时才会出现快速增长的现象.

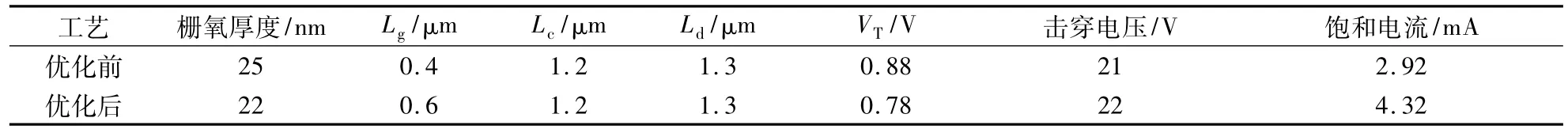

表1将高压nMOSFET结构和工艺优化前后的测试结果进行了对比.由表1可见,改进后的高压nMOSFET漏极饱和电流明显增大,工作速度得到提升,满足了反熔丝FPGA工作频率的要求.

表1 高压nMOSFET优化前后结构参数和测试结果

6 结语

本文详细描述了采用中国电子科技集团第五十八所晶圆ONO反熔丝工艺生产的高压nMOSFET的设计流程和器件特性.该高压器件工作速度快,阈值电压为0.78 V,与常压器件兼容,最优参数下雪崩击穿电压达到22 V,远远大于ONO反熔丝13.5 V的编程电压.综上所述,本文设计的高压nMOSFET成功达到基于ONO反熔丝FPGA存储单元选择管的设计要求.

References)

[1]冯彦君,华更新,刘淑芬.航天电子抗辐射研究综述[J].宇航学报,2007,28(5):1071-1080.Feng Yanjun,Hua Gengxin,Liu Shufen.Radiation hardness for space electronics[J].Journal of Astronautics,2007,28(5):1071-1080.(in Chinese)

[2]Brac E,Ferreyra P,Velazco R,et al.Test and qualification of a fault tolerant FPGA based active antenna system for space applications[C]//10th Test Workshop(LATW).Rio de Janeiro,Brazil,2009:4813814.

[3]王刚,李平,李威,等.反熔丝的研究与应用[J].材料导报,2011,25(11):30-33.Wang Gang,Li Ping,Li Wei,et al.Research and application of antifuse[J].Materials Review,2011,25(11):30-33.(in Chinese)

[4]Greene J,Hamdy E,Beal S,et al.Antifuse field programmable gate arrays[J].Proceeding of IEEE,1993,81(7):1042-1056.

[5]Chiang S,Wang R,Chen J,et al.Oxide-nitride-oxide antifuse reliability[C]//28th Annual Proceedings of Reliability PhysicsSymposium.New Orleans, LA,USA,1990:186-192.

[6]刘奎伟,韩郑生,钱鹤,等.兼容标准CMOS工艺的高压器件设计与模拟[J].半导体学报,2003,24(7):758-762.Liu Kuiwei,Han Zhengsheng,Qian He,et al.Design and simulation of high-voltage CMOS device compatible with standard CMOS Technologies[J].Chinese Journal of Semiconductors,2003,24(7):758-762.(in Chinese)

[7]Zhao Wenbin,Li Leilei,Yu Zongguang.High-voltage MOSFETs in a 0.5μm CMOS process[J].Chinese Journal of Semiconductors,2008,29(7):1268-1273.

[8]王晓慧,杜寰韩,郑生,等.具有加长LDD结构的高压CMOS器件[J].功能材料与器件学报,2007,13(3):275-278.Wang Xiaohui,Du Huanhan,Zheng Sheng.High voltage CMOS devices with lengthened LDD structures[J].Journal of Functional Materials and Devices,2007,13(3):275-278.(in Chinese)

[9]Liu Siyang,Qian Qinsong,Sun Weifeng.Analysis of hot-carrier degradation in N-LDMOS transistor with step gate oxide[J].Journal of Southeast University:English Edition,2010,26(1):17-20.

[10]Chandhi S K.VLSI fabrication principles[M].New York:John Wiley & Sons,Inc.,1994:717.