一种面向任务优化的多核心星务管理系统设计

兰盛昌,王 松,徐国栋

(1.哈尔滨工业大学 卫星技术研究所,150001 哈尔滨,lansc1015@gmail.com;2.中国空间技术研究院,100964 北京)

随着空间任务的深入,小卫星对控制精度要求越来越高,要求控制周期越来越短;然而由于小卫星在轨运行时,需要处理的数据多、任务复杂,加之中断的频繁发生,使得缩短传统单处理器系统控制周期受到较大限制,性能难以大幅度提高[1-2].

为了解决上述问题,科学界进行了大量的工作:一方面可以通过系统功能分解,利用硬件模块的增加来提升系统的性能,在微处理器、微电子设计理论的支撑下,以SoC 设计为基础,信息处理为核心开展研究[3];一方面在软件优化上着手.不过这两种方法中,前者势必带来整个卫星体积、质量的增加,这对小卫星的设计增加了风险和难度.而后者的优化空间是有限的,很大程度上难以实现优化的目标.

随着超大规模集成电路设计技术的不断发展,多核计算机技术对小卫星星载电子系统的性能提升提供了新的思路.商用领域中,以Intel 的Core 和以ARM 公司的ARM11 为代表的多核处理器在单个芯片中集成了多个处理器核,在不增加硬件开销和系统频率的前提下极大提升了计算机的处理能力[4-6].因此,利用这种多核心处理器技术,可以快速灵活地在基于SRAM 工艺的FPGA 内部构建出任务所需要的处理器单元,合理地实现对软硬件的划分.一方面加强硬件资源的管理,另一方面同时利用嵌入式操作系统实现小卫星任务调度和功能计算,能够更好地提高微小卫星在星务管理、姿轨控计算等方面的能力.

本文基于多核心处理器技术对星务管理系统设计展开研究.首先,对微小卫星星务管理系统进行了功能需求分析,实现FPGA 内部基于软核处理器的多核心系统构造,并移植以uC/OS-II 为代表的嵌入式操作系统完成资源分配和任务管理;然后,针对多核心处理器与嵌入式操作系统的特殊性,从软硬件联合设计的角度出发,对星务管理系统任务的传统划分进行优化;最后与现有的星上成熟产品进行对比.

1 星务管理系统任务需求分析

作为小卫星的核心,星务管理系统负责星上数据处理、任务调度、通信及控制等功能,同时通过测控系统连接地面站,解析遥控指令,组帧遥测信息,还要负责进行姿态、轨道测量与控制,实现卫星自主故障诊断与处理,进行飞行任务及资源管理.具体要求如下:

1)制导、导航与控制功能.考虑到空间复杂动力学条件,小卫星制导、导航与控制系统要求星务管理系统具备较高的快速性和实时性.

2)在轨管理功能.星务管理系统计算机具有较强的功能,可通过总线对星上设备等进行控制和管理.控制电源分系统为整星供配电,采集姿态轨道控制部件的参数并进行姿态轨道控制,控制载荷工作,并通过数传分系统下传数据等.

3)信息交互任务.需要采用先进的总线技术作为星务计算机与下位机信息交互的载体,要求具有良好的实时性,能够满足制导、导航与控制对响应时间的要求以及统一对时精度的要求,并且可以保证数据的可靠传输,构成小卫星内高效可靠的通信网络.

4)时间管理任务.为满足任务管理和制导、导航和控制要求,要求星务管理系统可产生具有较高精度的飞行器时间参考,并可向有关分系统分配时间信息和定时信号,为分系统提供事件的时间标记,并具有星上时间集中校正和均匀校正能力,以保证星地时钟的同步.

5)小卫星故障处理.在小卫星出现系统故障的情况下,能够对故障部件和系统进行诊断和隔离,以维持飞行器的基本功能,保证个别部件出现问题的情况下不影响其他系统功能.

6)测控管理.能够采集处理遥测参数,组帧、存储并传输到地面测控站;同时接收地面遥控指令,解释处理、分发或直接执行;接收处理延时指令.

2 星务管理系统硬件设计

基于以上的功能要求,采用最新的可重构技术对星务管理系统的硬件进行设计.具体结构如图1所示,主要包括FPGA 处理器单元、FPGA 配置存储器单元、通用微处理器管理单元以及外部接口.

FPGA 是星务管理系统设计中的核心器件,采用SRAM 工艺的FPGA,并利用软核处理器,能够实现等同于ASIC 器件具备的功能,这里选用赛灵思公司推出的Virtex II 代产品XQR2V3000型芯片.以FPGA 作为设计载体,主要是考虑到FPGA 的可重构特性,能够保证设计者根据系统需求进行有选择性的设计,这样也为多核技术的应用提供了可能[7-9].令人遗憾的是上述成果只停留在早期的可重构计算机设计上,缺乏工程实现性,并没有考虑空间适应性的影响.

根据配置时间与可靠性方面的考虑,选用赛灵思公司专用的PROM 型专用配置芯片方案.采用XQR17V16 作为FPGA 所需的配置文件的存储器.这里可以通过外部的通用微处理器管理单元对XQR17V16 的工作状态进行选择与控制.也可以考虑在此基础之上利用多片PROM 型专用配置芯片完成不同配置文件的选取,从而当系统需要重配置时对FPGA 中的处理器结构和功能电路进行更新.在Selected Map 模式下完成整片FPGA的重配置仅需33 ms(配置时钟为33 MHz).通用微处理器管理单元的作用:一方面可以作为看门狗,监视FPGA 的工作状态,提供配置所需的控制信号;另一方面通过预留的UART 接口与FPGA相连形成数据传输,便于系统重配置过程中信息的保存和恢复.

片外具备存储单元与FPGA 中的片内处理系统通过存储器控制器IP 相连,由非易失型存储器EEPROM/FLASH 和易失型存储器SRAM 共同组成.其中EEPROM/FLASH 主要是保存程序代码以及重要数据.而SRAM 是FPGA 片内处理系统中程序运行的主要空间.考虑到大规模存储器容易受到单粒子翻转效应的影响,因此可以增加EDAC/ECC 校验等手段实现数据的保护.

为了更好地应对空间环境的干扰,除了芯片等级选取有所提高外,硬件设计中还提供两级看门狗机制与定期重配置的主动防护措施,其中FPGA 处理器单元定期向看门狗电路进行清狗操作.当FPGA 状态异常时,FPGA 处理器单元的清狗信号一旦无效,一定时间后,看门狗电路会通知通用微处理器单元,由通用微处理器单元出发重配置信号,对FPGA 进行重配置.如果对FPGA 重配置不成功,则FPGA 对外输出的看门狗清狗信号均无效,则供电端的单稳态电路会进行自断电处理.同时在通用微处理器单元的配合下有计划地定期地重配置FPGA 以降低单粒子翻转作用的影响.

3 基于Microblaze 的双核系统设计

FPGA 片内处理系统是星务管理系统功能实现的主要部分.根据任务需求,采用主协双核处理器对常规的星载计算机进行优化.在现有小卫星500 ms 控制周期内,超过100 ms 进行姿态轨道计算,因此将姿态轨道计算放入协处理器中将有效提升系统的计算能力.设计的核心思想就是将原有的单一处理器的功能进行细化,形成负责星务管理的主处理器和负责姿态轨道计算的协处理器,并通过共享存储空间的方式将主协处理器间的信息进行交互.

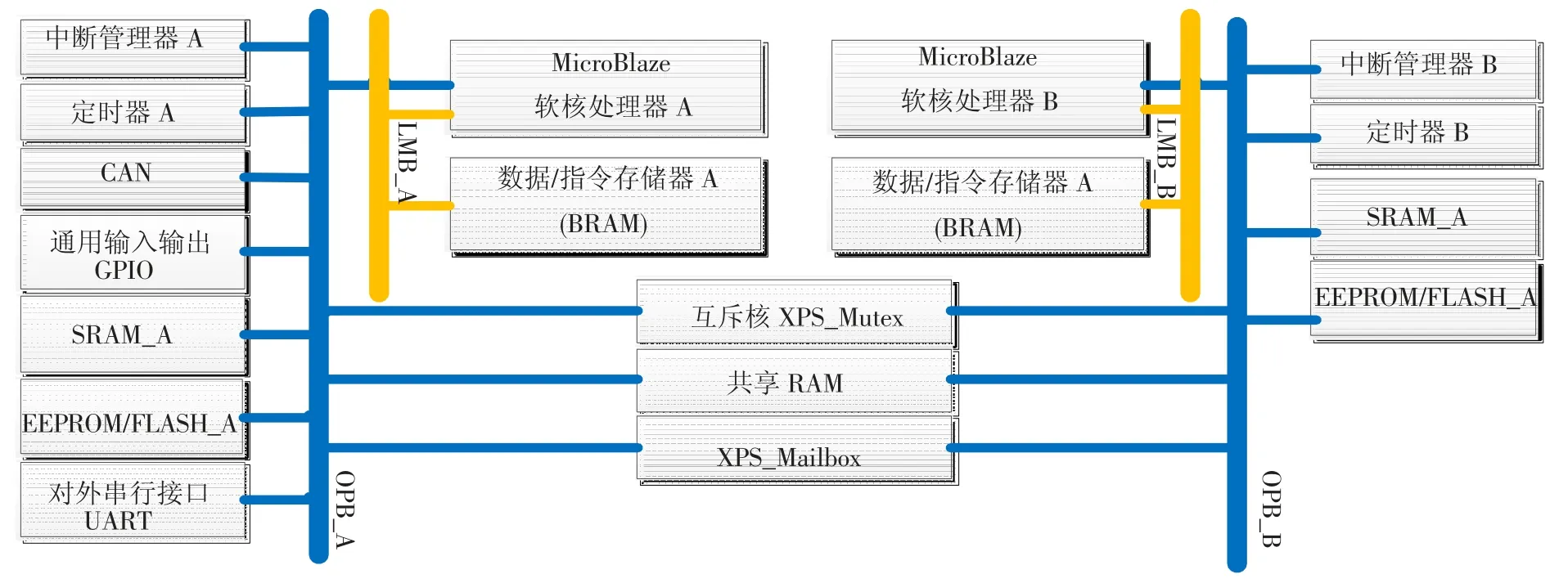

考虑到采用赛灵思FPGA 器件作为星务管理系统设计的可重配置载体,因此对处理器的设计也相应采用Microblaze 作为软核处理器核心.这里以双处理器系统为例,主要包括2 个独立的软核处理器MicroBlaze-A 和MicroBlaze-B,2 个FPGA 片内存储器BRAM,2 个中断管理器xps-intc,共享内部存储器BRAM 及处理器间进行数据交换的xps-mutex 互斥核、XPS-Mailbox 邮箱.除此之外,还可以根据系统功能需要配置相应的对外接口(通用输入输出口GPIO 等)以及各自处理器所需的外部存储器控制器接口,如图2 所示.片内BRAM 作为双核信息交互的媒介,双核处理器间信息的交互均通过对BRAM 上共同存储的空间读写完成.片内处理器与其他IP 之间通过Local Memory Bus 总线和On-Chip Peripheral Bus 总线相连.其中Local Memory Bus 总线用于软核处理器访问片内BRAM,包括指令缓存和数据缓存;OPB总线用于连接软核处理器和外部接口控制器,处理器内核通过此总线完成对外设的访问[10].

图2 双核处理器架构框图

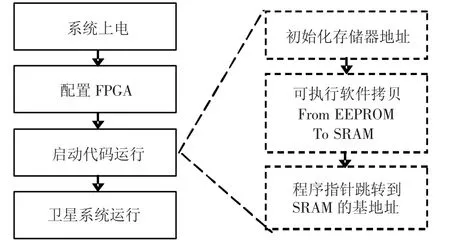

星务管理系统加电后,通用微处理器管理单元最先开始运行,由其完成整个FPGA 处理器单元的配置过程,配置触发信号发出后,所选择的专用配置芯片PROM 中的配置文件按照一定的时序写入FPGA 内可配置区域,从而完成对FPGA双核处理器结构的配置;初始化到内部BRAM 存储器中引导程序自动运行,通过外部存储器接口控制器将EEPROM/Flash 等非易失存储器中的应用程序读出并搬移到外部SRAM 中,完成后,启动程序PC 指针的跳转,将PC 指针指向SRAM 的基地址,开始运行搬转到EEPROM/Flash 的应用程序,如图3 所示.

图3 系统启动流程图

硬件启动过程完成后,小卫星由星务管理系统进行控制.内部的两个处理器单元进行功能划分.通常情况下可以将原有星务管理的功能分配给两个处理器.由MicroBlaze-A 完成信息采集,而由MicroBlaze-B 调用姿态轨道控制算法进行计算,完成卫星姿态轨道的控制.其中,MicroBlaze-A 从对外接口获得小卫星各个系统的遥测信息以及地面上注的遥控信息,同时获得姿态与轨道的实时测量数据.MicroBlaze-A 将姿态与轨道的实时测量数据传送到两处理器间共享BRAM中,并将指向该数据的地址和数据量经XPSMailbox 传递给MicroBlaze-B 来完成,MicroBlaze-B 完成计算后,再次通过这种机制将信息返回给MicroBlaze-A,MicroBlaze-A 通过对外接口输出至姿态轨道控制系统.这种数据共享可以通过XPS-Mailbox 中断方式通知对方,有很好的实时性,能够有效地提高处理器间的处理效率.这种并行处理的能力是提升星务管理系统性能的有效途径之一.

4 星务管理系统设计

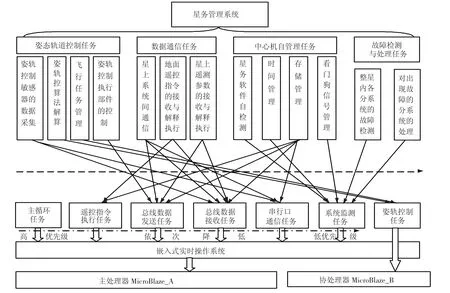

一般来说,卫星由通用卫星平台和有效载荷两部分组成.传统的星务管理系统设计方法将硬件和软件划分为两个独立的部分.这种设计方法只能单一的针对硬件或软件来进行改善,而在有限的设计空间中缺乏足够的高度从系统出发完成对整个系统的性能综合优化.比如传统的星务管理系统划分为姿态轨道控制任务、数据通信任务、计算机自管理任务、故障检测与处理任务(如图4).以上基于功能异同对星务管理系统进行了任务划分,这种划分方法较好地诠释了星务管理系统的功能,但在具体软件程序实现时此划分方法却具有很大的局限性,各分系统任务间的交叉不利于软件程序的模块化设计[11];因此有必要在星务管理系统软件实现时再一次对上述任务进行划分与合并.在多核心处理器的层面,可以将原有的软件任务部分转为硬件化实现.其目的是从星务管理系统软硬件中,获得一个满足系统资源、成本、时间、功耗等方面需要且趋于最优的方案.

图4 星务管理系统任务划分

在多核心处理器设计的层面,星务管理系统软件可以根据硬件设计的实际情况整理出数据流向,分别针对通信接口建立不同的任务,以防止数据间的交叉造成数据错误.比如根据本文3 节给出的硬件设计,作出以下任务划分:系统循环任务、遥控指令执行任务、姿轨控任务、总线数据发送任务、总线数据接收任务、串行接口通信任务、系统监测任务等,同时可以根据系统需求,增加一个空闲任务以消耗CPU 时间.其中特别值得注意的是,姿轨控任务可以分配给其他处理器完成,以降低系统开销,同时也可以利用数字化设计等先进设计方法,完成面向姿轨控算法的IP 设计,通过调用IP 核,进一步提高运算的速度.

系统循环任务是整个星务管理系统中优先级最高的任务,主要负责系统的初始化,初始化完成后,利用自身主时钟计时,周期性产生信号量等信息以调度其他任务的运行.

遥控指令执行任务主要是从遥控信道接口(如总线接口或脉冲编码调制接口)接受遥控信息并执行.

总线发送任务负责总线信息组帧及发送.

总线接收任务利用总线控制器给出的中断信号,触发中断服务程序接受总线数据,之后通过检测帧ID 以及校验和等信息,检验完成总线数据的分类和处理.

实际硬件接口的情况还包括了与姿态测量敏感部件的串行接口,因此将其独立为一个任务,以区别于总线通信相关的任务.此任务既负责其控制姿态测量敏感部件指令的发送,也负责采集来自姿态测量敏感部件的工程参数和遥测参数及后续数据处理.

系统监测任务负责星务管理系统对自身功能进行检测、时间管理以及完成对星务系统本身即其他总线下位机的故障检测与处理.

姿轨控任务负责卫星飞行任务管理和姿态轨道控制算法的解算,其中姿态轨道控制算法的解算是星上计算量最大的部分.主要包括卫星入轨初期的速率阻尼,任务需要时进行的对日捕获和定向姿态控制;对日定向三轴稳定姿态控制;星地数据传输期间以及轨道机动期间的对地定向三轴稳定姿态控制;姿态失控条件下的姿态安全模式控制,以保证卫星的能源供应.

在多核心处理器的使用中,可以由不同处理器来分担上述任务.以本文3 节中所构建的处理器系统为例,可以利用MicroBlaze-A 完成姿轨控制部件的工程参数采集,并传递姿轨控制任务指令,通过处理器间的共享RAM 等方式,由MicroBlaze-B将指令解释执行或存入飞行任务列表,并根据飞行任务调用相对应的姿态轨道控制算法进行解算,并将计算结果返回给MicroBlaze-A,由MicroBlaze-B最终完成姿态轨道控制执行部件指令发送.

5 星载电子系统的测试

5.1 运算性能测试

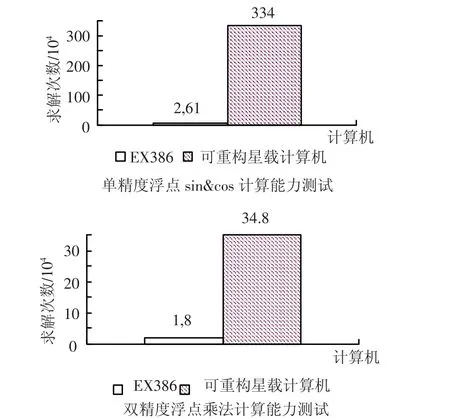

为了更好地完成星务管理系统的运算性能的测试,采用小卫星姿态轨道计算中频繁调用的浮点乘法和三角函数来作为测试项.实验中,选用哈尔滨工业大学试验卫星三号星载计算机使用的EX386 核心处理器的传统星载计算机作为参照对象,以两者计算频率作为评定指标.测试结果如图5 所示,可见相对于传统星载计算机,本文所构造的星务管理系统在在单精度浮点运算以及双精度浮点运算方面都有显著的提高,单精度浮点计算能力提高了近130 倍,双精度浮点计算能力提高了近20 倍,说明本文所构造的星务管理系统具有很强的计算能力.

图5 多核心可重构星务管理系统与EX386 核心处理器星载计算机计算能力对比

5.2 计算精度测试

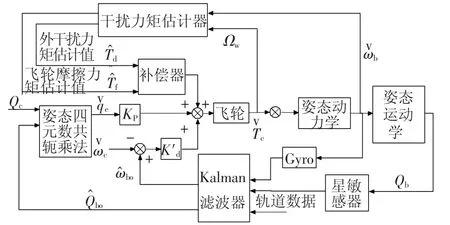

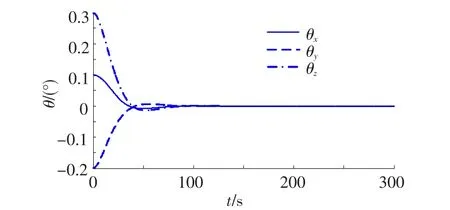

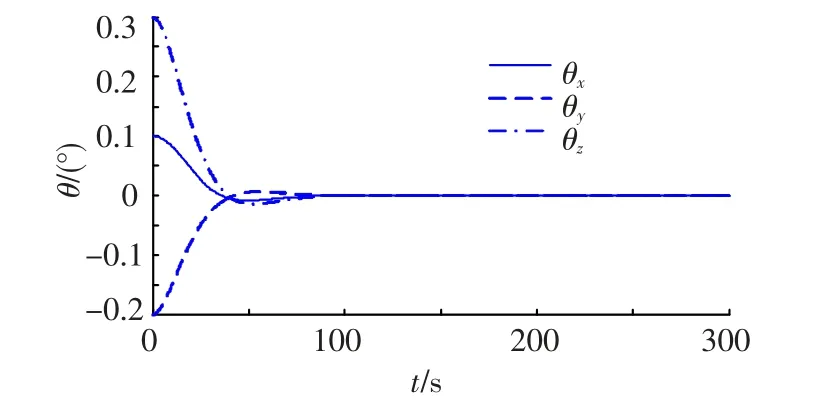

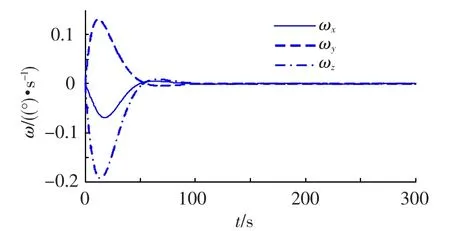

在计算精度测试方面,首先建立仿真环境,由xPC 实时仿真机模拟卫星控制系统中的敏感部件和执行机构,包括反作用飞轮、光纤陀螺、星敏感器等.姿态控制系统采用以姿态四元数为姿态控制参数的PD 控制器加估计补偿器的控制原理,如图6 所示.分别将传统基于EX386 设计的星务管理系统与多核心可重构星务管理系统接入仿真系统,通过外部总线接口采集xPC 计算机提供的动力学仿真数据,并调用姿态控制算法对其进行解算,得到计算结果后,返回给xPC 以模拟对执行部件模拟器进行控制,并输出姿态角和姿态角速度在这一仿真环境中的变化情况.仿真结果如图7 ~10 所示,可见多核处理仿真结果与传统星上计算方法在仿真精度上基本一致,能够在100 s内完成大角度机动,取得很好的控制效果.

图6 对地定向三轴稳定模式控制算法对比仿真模型

图7 对地定向三轴稳定模式小卫星相对轨道坐标系的姿态角(多核处理仿真)

图8 对地定向三轴稳定模式星体相对轨道坐标系的姿态角速度(多核处理仿真)

图9 对地定向三轴稳定模式小卫星相对轨道坐标系的姿态角(传统计算机结果)

图10 对地定向三轴稳定模式星体相对轨道坐标系的姿态角速度(传统计算机结果)

从以上仿真结果可看出,采用多核处理技术构建的星务管理系统在计算速度上要好于现有的传统星载计算机,而在计算精度上达到了现有计算机的性能.多核心技术的采用为未来小卫星星务管理系统的设计奠定基础.

6 结 论

1)本文摒弃传统星务管理系统的设计方法,利用多处理器并行处理的灵活性,构建了多核心处理器系统.

2)引入嵌入式实时操作系统对小卫星的任务进行调度和管理,充分发挥了多核心处理器系统的并行性和操作系统的实时性的优势,使星务管理系统在功能和效率等方面均具有显著的提高.

3)基于该思想设计的原理样机现已投入科研试验中.证明基于多核心设计的可重构星务管理系统是未来微小卫星发展的一条可行之路,也为其他项目的开展奠定了实验基础,为未来卫星编队飞行、星间通信体制等方面研究提供了有力的支持.

[1]徐国栋,赵丹.可重构的卫星/运载复用电子系统设计[J].航空学报,2009,30(7):1298-1304.

[2]KAHRAMAN M O,SWENSON E D,BLACK J T.A constraint based approach for building operationally responsive space satellites[C]//4th Internation Conference on Recent Advances in Space Technologies.Istanbul Turkey:IEEE Computer Socity,2009:506-511.

[3]兰盛昌,孙蕊,邬树楠,等.基于SoC 的“微型核”星载电子系统设计[J].哈尔滨工业大学学报,2007,40(7):1026-1031.

[4]孙兆伟,刘源,徐国栋,等.小卫星/小运载可重构多核计算机设计[J].航空学报,2010,31(4):770-777.

[5]ZAHID S,AYYAZ N.An economical on-board computer for low-earth-orbit satellites[C]//Proceedings of IEEE Students,Conference.Piscatalvay:IEEE Service center,2002:66-75.

[6]ASOKAN V,Designing Multiprocessor SOCs[J].Xcell,2008(2):48-50.

[7]武文权.可重构并行小卫星星载计算机体系结构设计[D].上海:中国科学院研究生院(上海微系统与信息技术研究所),2004:35-36.

[8]任小西,张克环,李仁发,等.基于可重构的星载数据处理系统结构研究[J].世界科技研究与发展,2008,30(2):147-150.

[9]施炜雷,于平,邓超,等.基于UC/OS-Ⅱ的可重构计算机系统的设计[J].微计算机信息,2008,24(10):79-81.

[10]Xilinx.ML40x EDK Processor Reference Design-User Guide for EDK 8.1[M].edition 5.[S.l.]:Xilinx,2006:25-35.

[11]王松.基于FPGA 的多核可重构技术研究[D].哈尔滨:哈尔滨工业大学,2011:45-60.