基于TotalRecall技术ASIC的FPGA原型验证

郭安华,黄世震

(福州大学福建省微电子集成电路重点实验室,福州350002)

目前ASIC设计的规模及复杂度正在呈指数增加,在带来实现高性能芯片系统可能性的同时,也带来了前所未有的芯片验证问题,验证和调试所占的时间可以达到总工期的70%以上[1]。验证的方法有多种可以选择,如软件模拟、硬件加速模拟、硬件仿真及基于FPGA原型设计验证等,这些方法各有利弊。而FPGA原型验证方法一方面可使设计者可以较好的把握硬件设计的物理特性,硬件平台能够重复利用;另一方面基于FPGA的原型验证平台可以比软件仿真速度高出4~6个数量级,填补了仿真环境与实际芯片的巨大差距。因此,FPGA原型验证具有很高的性价比。

本文主要描述运用ToalRecall技术结合FPGA原型的一款鼠标芯片ASIC验证平台的实现过程。

1 验证方法概述

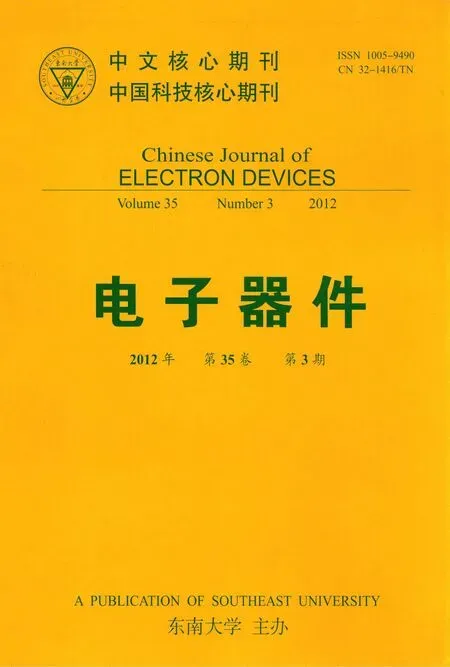

传统的验证方法有软件模拟、硬件加速模拟、硬件仿真及基于FPGA原型验证等[2],软件模拟成本很低但验证花费时间长,而基于FPGA的原型设计验证方法不仅成本低,而且速度很快。硬件加速模拟及仿真的速度比软件模拟速度快很多,但比FPGA验证法慢很多,且其成本要比上述两种方法高很多,所以基于FPGA原型设计验证方法具有最高性价比。但传统基于FPGA原型设计验证的明显缺点是缺乏对内部信号、状态及寄存器内容的可视性。而结合ToalRecall技术的FPGA原型验证方法提供了100%的可视性,还能以实时硬件速度运行。各种验证方法的可视性对比如图1所示。

图1 各种设计验证方法的可视性对比

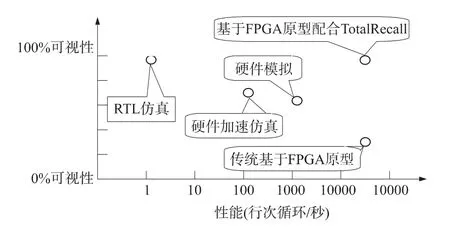

2 ASIC芯片架构

ASIC,即专用集成电路,是指应特定要求和特定电子系统的需要而设计、制造的集成电路。本文所描述的芯片是一款鼠标芯片。图2是设计的鼠标芯片的系统架构框图,它包含 DSP模块,ROM,SRAM,Sensor,LED 驱动,系统控制,USB 接口控制器模块,电压电路,时钟电路,复位电路等。

图2 ASIC框图

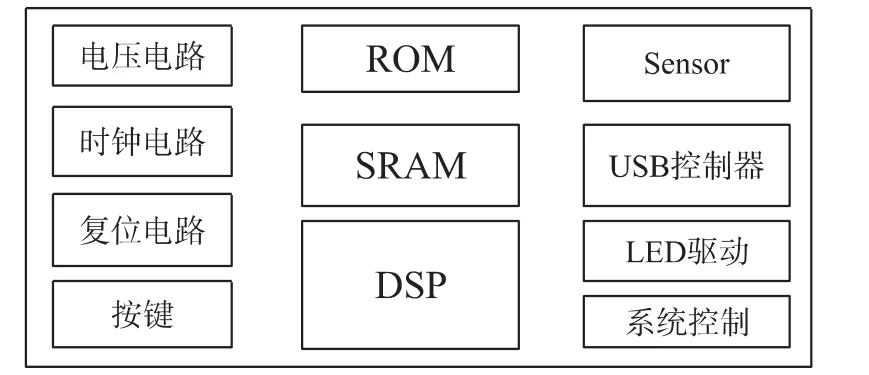

3 结合TotalRecall技术的ASIC设计流程

基于加入TotalRecall技术FPGA原型验证的ASIC设计的基本流程如图3所示[3]。

图3 结合TotalRecall技术FPGA原型的ASIC设计的基本流程

由于FPGA技术的快速发展,FPGA在资源、速度、性能等方面都得到了较大的改善,FPGA在密度、速度方面和ASIC的相似性使得基于FPGA的原型运行速度接近于现实速度,不仅可以大大提高系统的仿真速度,而且还可以让我们尽早地来测试应用软件,从而达到节省整个ASIC开发时间的目的。

4 结合TotalRecall技术FPGA原型的设计实现

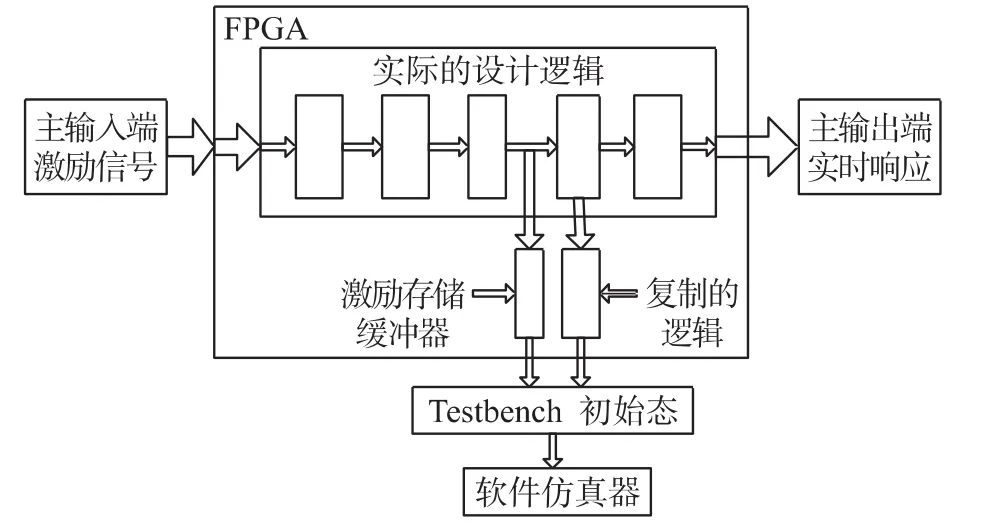

4.1 TotalRecall技术概述

TotalRecall技术结合FPGA原型可以解决传统基于FPGA原型设计验证系统的可视性问题,该验证方法在提供100%可视性的同时,还可保证FPGA以实时硬件速度运行。

TotalRecall技术的原理是在FPGA内部复制逻辑,然后存储该复制逻辑的激励,同时延迟其应用。图4是TotalRecall的原理,主输入端的激励信号直接输入实际逻辑块,输出端的实时响应由此逻辑块产生。同时,原始测试矢量也输入作为缓冲器的存储区。当检测到输出端的错误响应时,复制逻辑及其相应存储缓冲器将暂停。此时,激励存储缓冲器内容及复制逻辑内容状态由FPGA器件的JTAG端口导出,并用于软件仿真器。

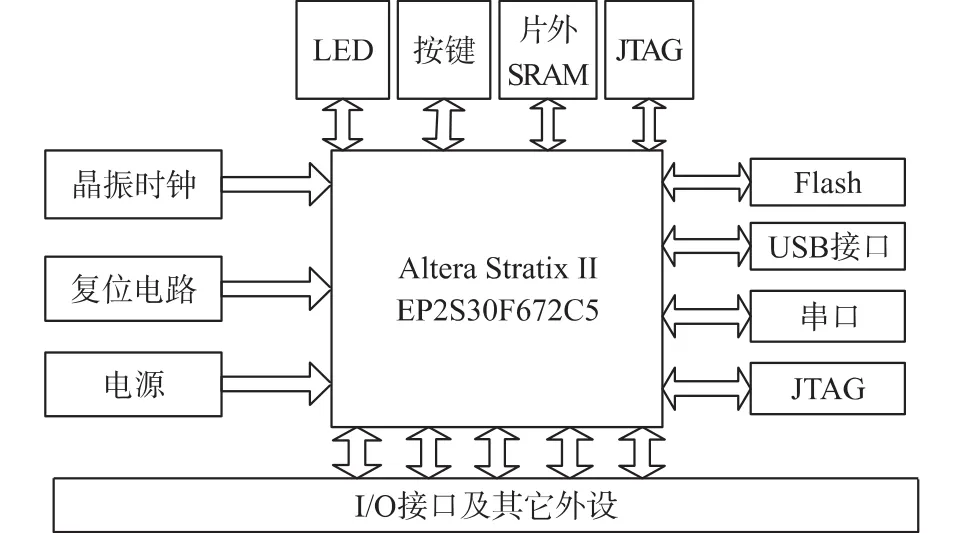

4.2 验证板介绍

如图5所示,FPGA验证板采用了Altera公司的StratixⅡEP2S30F672C5型号的可编程逻辑芯片,包含27 104个查找表的资源[4],完全可以满足项目的需要。验证板上还提供了一般系统的电压,板级的晶振及板级上电复位源,为了方便验证板的使用,验证板上还集成了一些外设及常用的系统接口。此外验证板上还引出了大量FPGA的IO口用于功能扩展。

图5 FPGA验证板

4.3 设计的转换[5]

采用FPGA原型技术验证ASIC设计时,首先需要把ASIC设计转化为FPGA设计。但ASIC是基于标准单元库,FPGA则是基于查找表,ASIC和FPGA物理结构上的不同,决定了ASIC代码需要一定的转换才能移植到FPGA上,但这只是由于物理结构不同而对代码进行的转换,并不改变其功能。需要转换的代码主要有以下几个方面:

(1)时钟单元

ASIC中的时钟从时钟源出发,经若干层时钟缓冲器到达每个寄存器的时钟端,形成所谓的时钟树结构。ASIC时钟树的插入主要由布局布线工具自动完成,利用代工厂的 PLL进行时钟设计。而FPGA中通常配置了一定数量的PLL宏单元,且有针对时钟优化的全局时钟网络,可以保证相同的时钟沿到达芯片内部每个触发器的延迟时间差异是可以忽略的,所以时钟单元是需要转换的。

(2)存储单元

ASIC中的存储单元通常用代工厂所提供的Memory Compiler来定制,通常是不能综合的。而FPGA提供了经过验证并优化的存储单元。所以存储单元必须要进行代码转换的。

(3)增加流水

由于实现结构上的不同,PFGA器件内部的单元延时远大于ASIC的基本门单元延时。

从而在同样设计的情况下,ASIC可以满足时序,而FPGA有可能无法满足。为了验证的需要,对ASIC实现的流水结构在FPGA实现时需要适当增加流水。

(4)同步设计

在FPGA设计中,同步设计是非常重要的,当从ASIC转向FPGA设计时,需要进行同步。在ASIC的设计中,为了减少功耗,使用了门控时钟,但由于设计的异步特性,对于FPGA来说,使用这种门控时钟容易产生毛刺,导致数据不正确。所以在FPGA设计中,使用使能信号的电路来代替门控时钟电路。

4.4 模拟部分的整合

FPGA是现场可编程逻辑器件,只能实现数字电路,模拟电路无法在FPGA中实现。要验证这些模拟IP核,可以选用同样功能的芯片或者这些模拟IP核的样片来代替,与FPGA共同实现它们的功能,其中比较重要的几个模拟IP转换的方案如下所述[6]:

(1)系统电源由FPGA验证板提供的电压源来实现;

(2)系统复位可由FPGA板级上电复位源作为系统复位信号实现;

(3)系统中的Sensor和ADC由样片和相同功能的芯片来实现;

(4)系统中ROM和SRAM可由FPGA内部的RAM及外部的SRAM实现;

(5)系统时钟由振荡器提供,采用FPGA板的晶振作为时钟源。

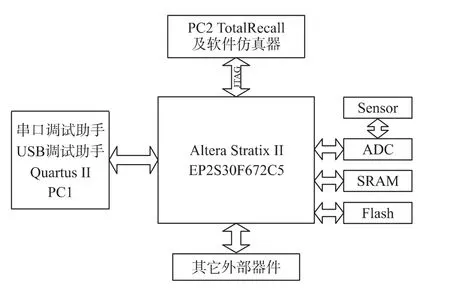

5 结合TotalRecall技术FPGA原型的验证

结合TotalRecall技术FPGA原型验证平台的整体结构如图6所示,此平台主要由PC机、FPGA、Flash、SRAM、Sensor样片、ADC芯片、按键、串口、USB接口及一些其它的外设等组成。在PC1机上安装Altera的FPGA软件 QuartusⅡ,上位机 PC1通过 Altera usb blaster下载线与验证平台上FPGA的JTAG接口相连,这样就实现了上位机上QuartusⅡ软件与验证板上FPGA之间的连接,使用QuartusⅡ软件通过Altera usb blaster下载线把完全编译好的工程下载到验证板上。在PC2上TotalRecall也通过JTAG与FPGA板相连,可为FPGA验证系统提供100%的可视性。

图6 验证平台的整体结构

验证可以分为模块级验证、系统级验证两个层次,在进行设计原型验证时,首先应该保证验证平台各个模块的正确性,对各模块进行验证[7]。下面以验证系统中的USB控制器模块为例,说明结合TotalRecall技术FPGA原型验证平台对设计模块的验证。根据USB2.0协议,USB鼠标接口主要有四个信号线:电源、地、D+及D-,且它具有两种通信方式,一种是主机到设备的通信,另一种是设备到主机的通信。利用USB鼠标接口的D+和D-信号就可以对其进行通信验证。具体验证过程如下:首先,我们在上位机PC1上用VC[8]开发一个USB调试助手,由于FPGA原型验证平台提供了USB接口的外设,所以可以直接利用此外设来接受USB调试助手发送的数据指令,并把这些数据指令传送到USB控制器。同时也可以接受USB控制器模块反应的数据指令,并把它传送到上位机PC1上的USB调试助手上。我们可以把接受到的反应数据指令与期望的值做个比较,看两者是否一致,从而来验证USB接口控制器模块的正确性。当接受的响应数据与期望的值不同时,即发生了故障,可以利用TotalRecall技术复制USB控制器功能块。如图7所示TotalRecall技术应用于设计验证系统中的功能块,TotalRecall技术能够生成局部Testbench,专门用于测试挂起功能块。此时,激励存储缓冲器内容及复制的逻辑内容由FPGA器件的JTAG端口导出,并用于软件仿真器。TotalRecall技术可以定位到故障前数百甚至上千个周期前的状态值,用来对软件仿真器进行初始化设置。这样,USB控制器功能块就能够在实时硬件速度下提供100%的可视性,并且还能在熟悉的软件仿真环境下跟踪故障,从而快速的定位及解决故障,使USB控制器功能块得到完全的验证。

图7 TotalRecall技术应用于系统功能块

6 结束语

基于FPGA原型验证对于ASIC验证是一个非常实用的方法,结合TotalRecall技术的FPGA原型验证方法可以有效解决传统FPGA原型验证可视性差的弊端。该方法不仅能够快速检测、调试并解决深藏的偶发及间发故障,这些故障有时会出现在实时激励的情况下或由软硬件之间复杂的非确定性互动引起,而且还能提供我们在熟悉的软件仿真环境中跟踪故障。从而大大提高了芯片验证的效率,缩短芯片开发的时间。

[1]马凤翔,孙义和.SoC原型验证技术的研究[J].电子技术应用,2005.3

[2]姚远,张晓琳,张展.基于FPGA的可层叠组合式SoC原型系统设计[J].电子技术应用,2009,9

[3]濮津,林孝康.内嵌ARM9E内核系统级芯片的原型验证方法[J].微计算机信息,2005.

[4]王诚,蔡海宁,吴继华.Altera FPFA/CPLD设计(基础篇)[M].人民邮电出版社,2011.

[5]章玮.原型验证过程中的ASIC到FPGA的代码转换[J].今日电子,2006,(7).

[6]杨安生,黄世震.基于ARM SoC的FPGA原型验证[J].电子器件,2011.3

[7]黄丽.百万门级专用集成电路的FPGA验证平台[D].西安:西安电子科技大学,2007.

[8]潘爱明,王国印.Visual C++技术内幕[M].北京:清华大学出版社,1999.