一种采用嵌套斩波技术的Σ-Δ调制器的设计*

胡 斌,徐德辉,熊 斌

(中国科学院上海微系统与信息技术研究所,传感技术联合国家重点实验室,微系统技术国家重点实验室,上海200050)

近年来,IC工艺技术发展的一个重要趋势就是实现智能传感器的集成[1],而大多数传感器有输出信号小,频率低的特点,这就要求高分辨率的读出电路。在微系统的实现过程中,A/D转换器是必不可少的模块,在众多类型的A/D转换器中,过采样Σ-Δ调制器可达到很高的精度和很好地噪声性能,广泛应用于低频高分辨率的场合,特别是音频和传感器电路。

不考虑电路内部噪声的情况下,过采样Σ-Δ调制器可达到很高的精度而不需严格的片上器件匹配[2]。但在实际应用中,如红外传感器读出电路,电路中的低频噪声(1/f噪声、失调等)严重影响甚至掩盖需要检测的微弱信号。目前消除运算放大器低频噪声的技术可归结为两种:自调零技术和斩波技术。自调零技术[3]是对电路中的噪声采样,然后在整体的输入信号中把噪声减去,通过补偿的方式消除噪声。斩波技术[4]是把输入信号调制到高频,然后进行放大,解调后信号回到基带而噪声被搬移到高频,通过调制解调的方式分离噪声。这两种技术都可以降低低频噪声,但都存在缺陷,自调零技术需要大的电容面积,引入了更多的热噪声,而斩波技术因工艺变化和开关的不理想性,在信号带宽内引入残余失调电压。国内外对低频小信号读出电路有较多研究。柴旭朝等人利用斩波技术设计的微电容读出电路[5],等效输入噪声为17 nV/Hz1/2。Christian等人采用基于滤波方式设计的斩波放大器[6],等效输入噪声为15 nV/Hz1/2。Chang Ying-Hwi等人首次将斩波技术应用到Σ-Δ调制器而非单个放大器[7],通过理论和实验的方法证明了斩波稳零Σ-Δ调制器其可行性。Chen Hsin-Liang等人对其进行改进,设计了基于伪随机斩波稳零技术的Σ-Δ调制器[8],相比斩波稳零Σ-Δ调制器,残余失调电压降低10 dB。Liu Shen-Iuan等人提出将嵌套斩波技术应用到Σ-Δ调制器[9],但对嵌套斩波Σ-Δ调制器的应用研究还未见报道。

为满足传感器读出电路的要求,本文针对低频噪声和斩波技术中的残余失调电压进行分析,设计了一款基于嵌套斩波技术的Σ-Δ调制器。

1 噪声来源

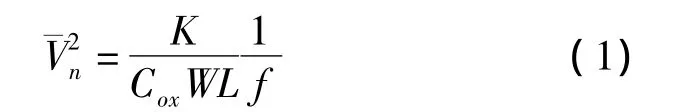

一般而言,MOS晶体管的噪声有两种:热噪声和闪烁噪声(1/f噪声)。热噪声由晶体管沟道内的热扰动引起,属于白噪声,而闪烁噪声与热噪声不同,它的平均功率不容易被预测,近似的由下式给出[10]

式中:K是一个与工艺相关的常量,W、L分别是MOS管的栅极宽和长,Cox是单位面积的栅氧化层电容,f是频率。这些噪声都与MOS管面积、电流大小成反比,在小于“转角频率”fc的频段,1/f噪声是主要噪声来源。除了1/f噪声,放大器的另一个非理想因素是失调。它由器件尺寸、阈值电压和偏置电流的不匹配引起,影响信号的精度。通常,失调被等效成很低频的输入电压,它和闪烁噪声一样,属于有色噪声。

过采样Σ-Δ调制器第1级积分器中的采样电容和运算放大器是主要的噪声源。根据反馈理论,Σ-Δ调制器第1级积分器的噪声没有被整形,严重影响调制器的性能。虽然可通过增大过采样率减小噪声,但1/f噪声与频率成反比,它仍然会大于热噪声。MEMS传感器输出属于低频小信号,失调和1/f噪声会干扰甚至淹没其输出信号。

2 系统设计

2.1 Σ-Δ调制器

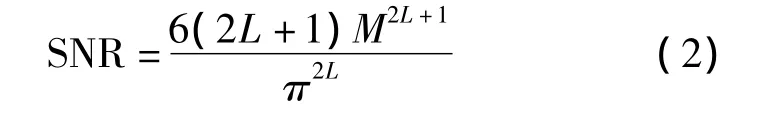

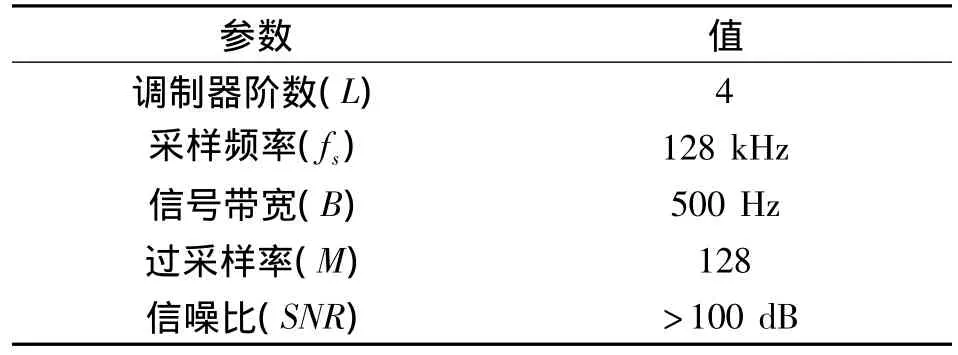

对于传感器应用,综合面积和功耗的考虑,选择单环单比特Σ-Δ调制器。若把Σ-Δ调制器的量化噪声等效为白噪声,在不考虑其他非理想因素的情况下,一位Σ-Δ调制器的信噪比为[11]

式中:L为调制器的阶数,M为过采样率(M=fs/(2B),其中fs为采样频率,B为信号的带宽)。考虑到MEMS红外传感器输出信号小,所以需要高分辨率(SNR>100 dB)的接口电路,根据式(1),可选择过采样率为128(M=128)的四阶(L=4)Σ-Δ调制器,各指标如表1所示。

表1 四阶单环一位Σ-Δ调制器指标

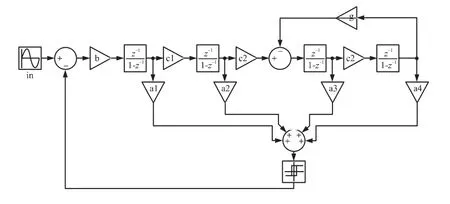

四阶单环一位积分器级联前馈(CIFF)的调制器结构[12]如图1所示,为了得到调制器的最优参数,遵循如下原则:

(1)为提高信噪比和稳定性,将噪声传输函数的零点分别放在直流和信号带宽边缘处(fz)。在仿真中,为使SNR达到最大,fz定为725 Hz,即两个零点被安置在带宽外(B=500 Hz)。

(2)为避免输入信号过大引起的不稳定,根据李氏定律(Lee’s Criterion),NTF(z)的最大值小于1.5。

(3)为保证5 V供电下调制器正常工作,对设计参数进行缩放以保证在任何情况下所有积分器的输出摆幅都在±1 V内。在5 V供电下,±1 V的输出摆幅可达到较高线性度。

图1 四阶单环一位Σ-Δ调制器结构

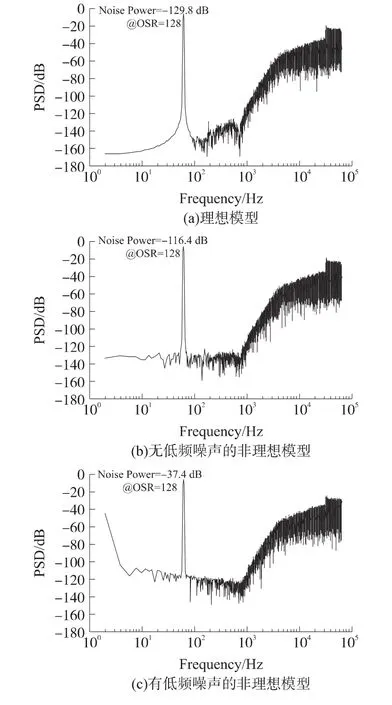

基于以上原则,采用MATLAB/SIMULINK中专用于Σ-Δ调制器仿真的SDtoolbox进行系统参数设计[13],得到最优参数如表2所示。四阶Σ-Δ调制器的最大输入信号为0.7 V~0.8 V,而为避免频谱泄露,输入信号频率选为采样频率的1/2N倍,所以选择0.5 V,62.5 Hz的正弦信号进行仿真。在理想情况下,输入仿真信号,将调制器数字输出信号进行65 536点的FFT变换(加Hanning窗),调制器输出信号的功率谱如图2(a)所示,输出信号在0~100 Hz频带内的噪声功率和为-129 dB。

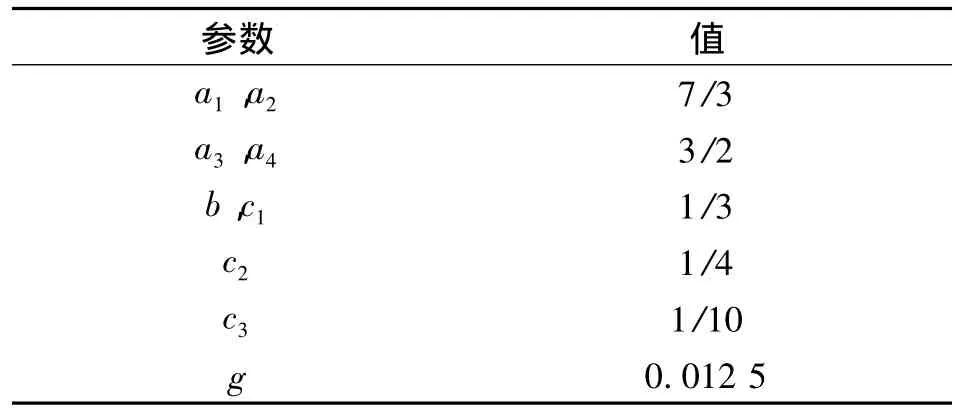

表2 Σ-Δ调制器的设计参数

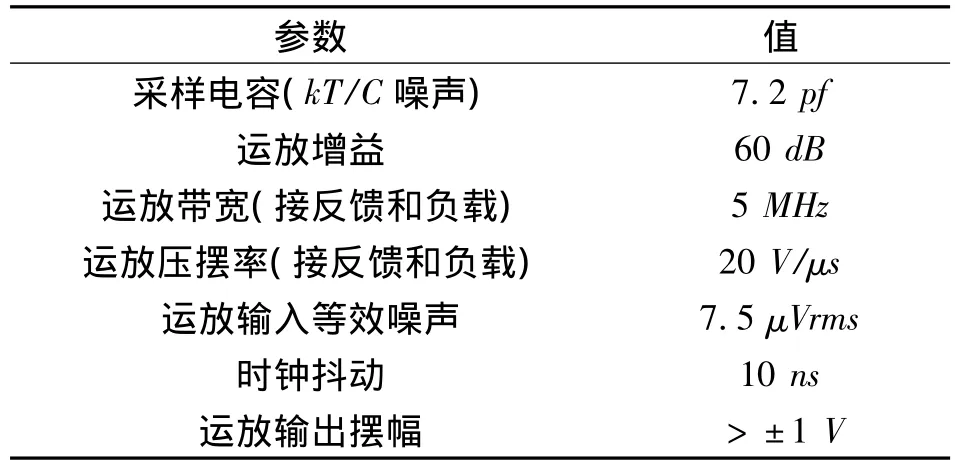

然而量化噪声并不是决定信噪比的唯一参数,热噪声、系统的非线性、运放的非理想性等因素都会影响到调制器的性能,特别是第一级积分器。考虑大部分影响Σ-Δ调制器的非理想因素(表3),用SDtoolbox的非理想模型进行仿真,得到的噪声功率谱密度如图2(b)所示,输出信号在0~100 Hz频带内的噪声功率和为-116.4 dB。

表3 第一级积分器的重要参数

图2 Σ-Δ调制器的功率密度谱

因为传感器输出属于低频信号,所以需考虑低频噪声对系统的影响,从上面分析可知,低频噪声主要有1/f噪声和直流失调。1/f噪声与频率成反比,由式(1)可估算其仿真模型为直流处1 μV,拐角频率(6 kHz)处15 nV的反比例曲线。直流失调用2 mV(典型值为1 mV~10 mV)的恒定值模拟。在系统中加入1/f噪声和直流失调的模型,得到其噪声功率谱密度如图2(c)所示,输出信号在0~100 Hz频带内的噪声功率和达到了-37.4 dB。

2.2 嵌套斩波

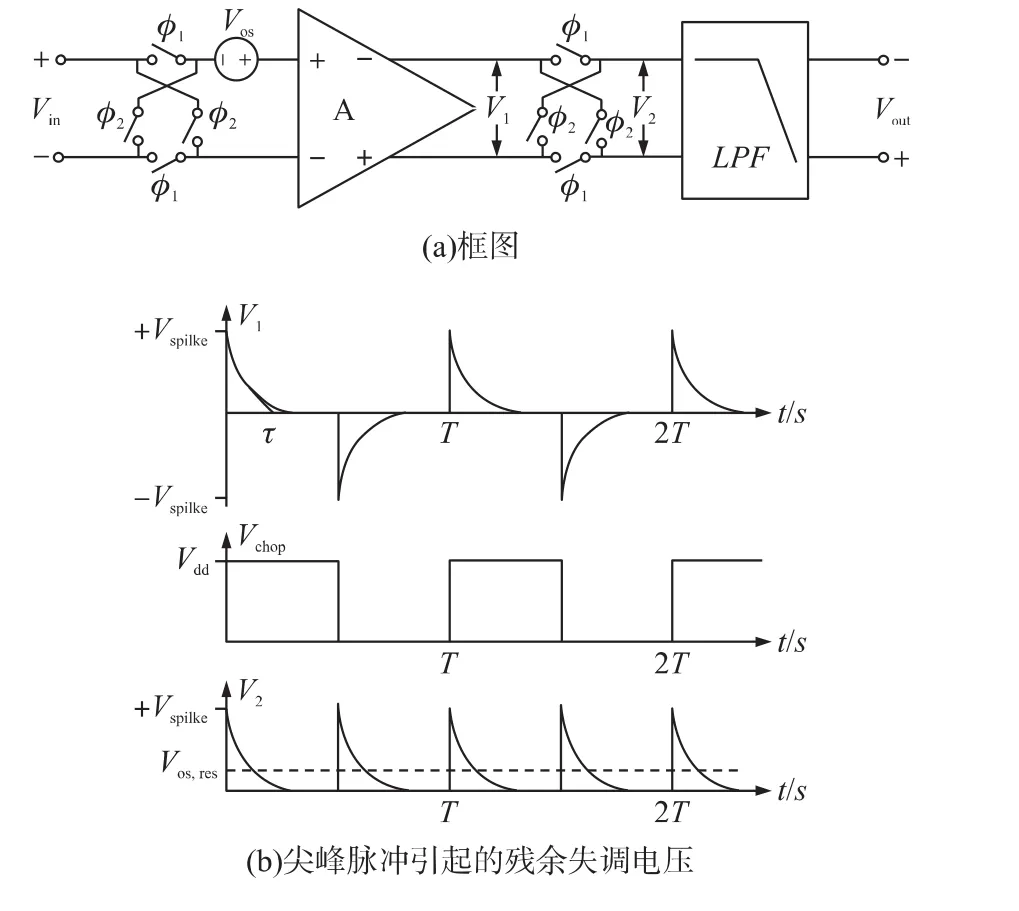

图3(a)是斩波技术的基本框图。输入信号Vin被调制到高频,然后进入放大器放大,这时信号V1中就混入了1/f噪声和直流失调,但均处于低频。解调后的信号V2,有用信号被还原到低频,而低频的噪声信号被调制到高频,最后通过一个低通滤波器得到没有1/f噪声和失调电压影响的放大信号Vout,实现微弱信号的放大[14]。

然而斩波技术因工艺变化和开关的不理想性,在信号带宽内引入残余失调电压。残余失调电压有几十微伏,主要由输入斩波开关的尖峰脉冲Vspike引起。这些尖峰脉冲由时钟馈通效应和开关电荷注入的不匹配产生,解调后,尖峰脉冲引起残余失调电压Vos,res,如图 3(b)所示。残余失调电压 Vos,res与尖峰脉冲Vspike的数量成正比,即与斩波频率成正比,而为了消除1/f噪声,斩波频率必须大于“转角频率”fc。

图3 斩波技术

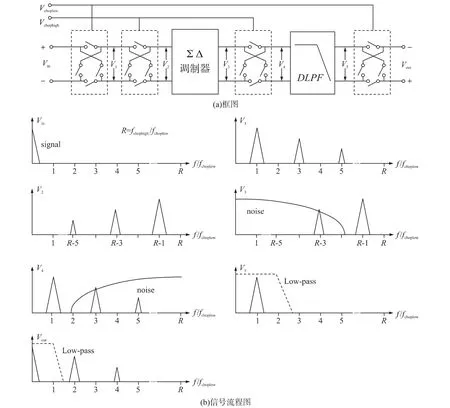

嵌套斩波放大器框图如图4(a)所示,它的基本思想[15]是把传统的斩波放大器等效成一个没有1/f噪声,只有很小失调的放大器。放大器的失调可以通过另一对斩波消除,而没有了1/f噪声的影响,这个斩波频率可以远远低于“转角频率”fc,这就降低了系统的残余失调电压。

高斩波频率fchophigh引入的尖峰脉冲V1被低斩波频率fchoplow调制后,整个尖峰脉冲V2的平均值变为零,理论上来说,残余失调电压被消除,如图4(b)所示。而考虑到低频率斩波也会引入尖峰脉冲,可知嵌套斩波对残余失调电压的抑制比为fchophigh/fchoplow。根据奈奎斯特采样定理可知,输入信号的频率要小于fchoplow/2。

图4 嵌套斩波

2.3 嵌套斩波Σ-Δ调制器

传统的Σ-Δ调制器在低频段存在较大噪声,影响整体结构的低频性能,特别是在传感器接口中的应用。通过上面的分析可知嵌套斩波技术对低频段的噪声有很好的抑制作用,在本设计中,嵌套斩波应用的对象是Σ-Δ调制器而不是单个的运算放大器。

图5(a)是嵌套斩波Σ-Δ调制器原理图,它与嵌套斩波放大器相似,内部斩波实现了对1/f噪声和失调电压的抑制,而外部斩波实现了对残余失调电压的抑制。其工作过程如图5(b)所示,带宽为Bsignal的低频信号 Vin被 fchoplow(fchoplow>2Bsignal)和fchophigh(fchophigh=fs/2)调制后,进入Σ-Δ调制器进行噪声整形,输出数字码流V3,此时系统中的1/f噪声、失调电压和大部分量化噪声均处于低频,与高频的有用信号分离。经过第一次解调后的信号V4回到fchoplow的奇次谐波,因带内噪声不再均匀分布,故在两次解调间加入低通滤波器,滤除带外噪声,最后得到输入信号的数字码流Vout。

图5 嵌套斩波Σ-Δ调制器

在MATLAB/SIMULINK中,对嵌套斩波Σ-Δ进行仿真。传统的 Σ-Δ调制器不再适用于本设计[16],信号经过两次调制后,仍要保证其处于Σ-Δ调制器的带宽内,这就要求Σ-Δ调制器的信号传输函数STF(z)高通且带宽大于外斩波频率fchoplow与信号带宽Bsignal之和(本设计中带宽为500 Hz,见表1)。根据文献[7]可知,Σ-Δ调制器传输函数可以通过z→-z的变换使低通变高通,高通变低通,而不会出现稳定性的问题,这样Σ-Δ调制器的噪声传输函数NTF(z)变成低通,而信号传输函数STF(z)变成高通,实现了高通Σ-Δ调制器的设计要求。高通Σ-Δ调制器由上文中设计的Σ-Δ调制器变换得到,带宽为 500 Hz,即为(fs/2 -500 Hz,fs/2)。为滤除V4的带外噪声,DLPF的截止频率选为500 Hz。

3 结果与讨论

由图2(b)和图2(c)可知,1/f噪声与直流失调影响了Σ-Δ调制器的低频性能,几乎淹没带内有用信号。而本文的重点就是设计一种Σ-Δ调制器,使其性能尽可能地接近图2(b),免疫低频噪声的干扰。文献[7]中提出了一种斩波稳零Σ-Δ调制器,该调制器可以消除1/f噪声和直流失调对低频信号的影响,本文设计的嵌套斩波Σ-Δ调制器目的是消除低频噪声并抑制残余失调电压,进一步提高Σ-Δ调制器的低频性能。

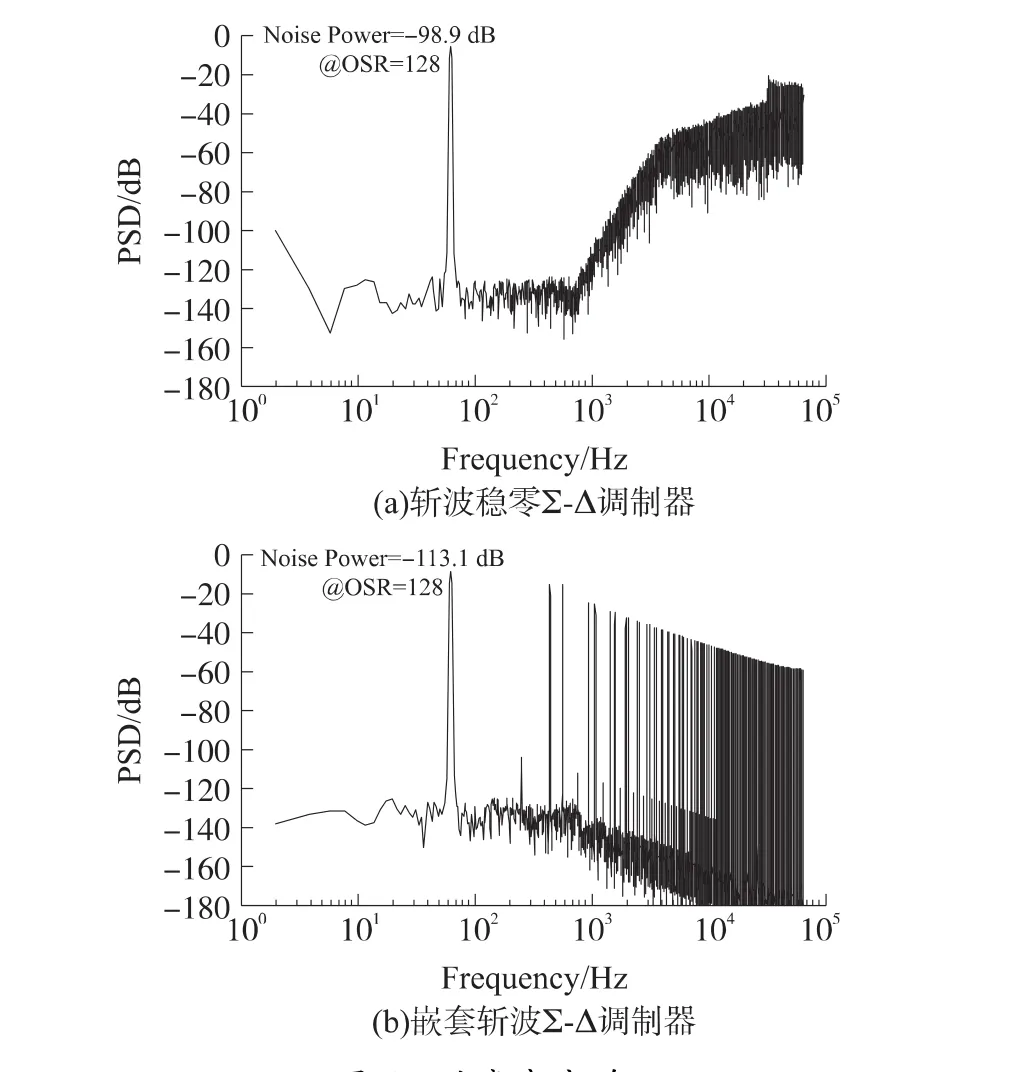

为验证嵌套斩波Σ-Δ调制器对残余失调电压的抑制,加入残余失调电压的等效噪声模型,在开关电容电路中,尖峰脉冲在每次采样的过程中都会对电容进行额外充电,所以可把尖峰脉冲简化为与fchophigh同频,幅值为10 μV的方波,与被调制后的信号相加后进入Σ-Δ调制器,而fchoplow引入的尖峰脉冲数量远远小于fchophigh,忽略不计。为使调制后的信号处于高频,fchophigh=fs/2,而 fchoplow>2Bsignal,此处选为250 Hz。输入0.5 V,62.5 Hz的正弦信号,分别通过斩波稳零Σ-Δ调制器和嵌套斩波Σ-Δ调制器,得到输出的功率谱如图6所示。

图6(a)与图2(c)相比,低频噪声减小,斩波技术抑制了1/f噪声和直流失调的影响,提高了Σ-Δ调制器低频段的信噪比。但斩波稳零Σ-Δ调制器并没有完全消除低频噪声,在图6(a)中的直流附近,仍存在较大噪声,这是由斩波技术引入残余失调电压引起的,它成为限制整个系统信噪比的最主要因素。

图6(b)是本文所设计嵌套斩波Σ-Δ调制器的输出频谱图(高频是第二次解调引入的谐波,可滤掉),在100 Hz内的噪声能量为-113.1 dB。图6(b)与图2(c)相比,直流附近噪声消失,带内噪声能量减小13 dB。由此可知嵌套斩波Σ-Δ调制器不仅消除了1/f噪声和直流失调在低频的影响,而且抑制了斩波技术引入的残余失调电压。图6(b)与图2(b)低频段性能比较接近,几乎完全消除了低频噪声的影响,在100 Hz内最大信噪比为109 dB,可达到17.8 bit的有效位数。

图6 功率密度谱

4 结论

MEMS红外传感器输出电压小(几十微伏)且频率低(<100 Hz),属于微弱信号,传统Σ-Δ调制器低频噪声大,严重影响甚至淹没传感器的输出信号。本文针对接口电路中低频噪声进行分析,设计了一种低噪声低失调Σ-Δ调制器,在理论和计算机仿真上都证明了其不仅可以消除1/f噪声和直流失调的影响,而且抑制了斩波技术引入的残余失调电压。传统的Σ-Δ调制器可以通过z→-z的变换,然后加入两对斩波开关和一个数字低通滤波器,得到嵌套斩波Σ-Δ调制器。

仿真结果表明,该调制器在100 Hz信号带宽内,可以达到109 dB的信噪比,即17.8 bit的有效位数。该嵌套斩波Σ-Δ调制器消除了低频噪声对信号的影响,在低频段有较高的信噪比,满足MEMS红外传感器低频微弱信号检测的要求。虽然该调制器是针对MEMS红外传感器进行设计,但它的应用不局限于此,所有电压大于10 μV(小于0.5 V)且频率低于100 Hz的信号都可通过此调制器进行检测。

[1] Massimo P,Michele D,Federico B,et al.Smart Flow Sensor With On-Chip CMOS Interface Performing Offset and Pressure Effect Copensation[J].IEEE Sensors Journal,2012,12(12):3309 -3317.

[2] 范军,黑勇,陈铖颖.一种采用斩波-稳零技术的低功耗Delta-Sigma调制器的设计[J].微电子学与计算机,2011,28(11):76 -80.

[3] Christian C E,GABOR C T.Circuit Techniques for Reducing the Effects of Op-Amp Imperfections:Autozeroing,Correlated Double Samping,and Chopper Stabilization[J].Proceedings of the IEEE,1996,84(11):1584 -1614.

[4] 姚镭,郝跃国,李铁,等.用于MEMS红外传感器的集成低噪声CMOS接口电路设计[J].传感技术学报,2007,20(10):2203-2206.

[5] 柴旭朝,顾晓峰,戴欢,等.低噪声低功耗微电容读出电路的优化与设计[J].传感技术学报,2010,23(8):1102 -1105.

[6] Christian M,Qiuting H.A Low-Noise CMOS Instrumentation Amplifier for Thermoelectric Infrared Detectors[J].IEEE Journal of Solid-State Circuits,1997,32(7):968 -976.

[7] Ying H C,Chung Y W,Tsai C Y.Chopper-Stabilized Sigma-Delta Modulator[C]//Processings IEEE International Symposium on Circuits and Systems,1993,2:1286 -1289.

[8] Chen H L,Chen P S,Chiang J S.A Low-Offset Low-Noise Sigma-Delta Modulator With Pseudorandom Chopper-Stabilization Technique[J].IEEE Transactions on Circuits and Systems,2009,56(12):2533-2543.

[9] Liu S H,Kuo C H.Nested Chopper Delta-Sigma Modulator[P].U-nited States Patent,US 6639532 B1.2003 -10 -28.

[10]拉扎维.模拟 CMOS集成电路设计[M].陈贵灿,程军,张瑞智,等译.西安:西安交通大学出版社,2008:175-178.

[11] Steven R N,Richard S,Gabor C T.Delta-Sigma Data Converters:Theory,Design and Simulation[M].New York:IEEE Press,1997:44-74.

[12] Simona B,Fabrizio F,Piero M,et al.A Fourth-Order Single-Bit Switched-Capacitor Σ - Δ Modulator for Distributed Sensor Applications[J].IEEE Transactions on Instrumentation and Measurement,2004,53(2):266 - 270.

[13] Piero M,Simona B,Fabrizio F,et al.Behavioral Modeling of Switched-Capacitor Sigma-Delta Modulators[J].IEEE Transactions Circuits and Systems,2003,50(3):352 -364.

[14] Christian C E,Eric A V,Franconis K.A CMOS Chopper Amplifier[J].IEEE Journal of Solid-State Circuits,1987,22(3):335-342.

[15] Anton B,Kevin T,Johan H,et al.A CMOS Nested-Chopper Instrumentation Amplifier with 100-nV Offset[J].IEEE Journal of Solid-State Circuits,2000,35(12):1877 -1883.

[16] Yin S Z,Siu k T,Chi t K,et al.A Chopper-Stabilized High-Pass Delta-Sigma Modulator with Reduced Chopper Charge Injection[J].Microelectronics Journal,2011,42:733 -739.