一种大屏显示技术在嵌入式系统船用雷达中的应用

阎旭田丹

(电子科技大学 成都 611731)

1 引言

嵌入式系统广泛用于船用雷达的显示控制系统,目前船用雷达的显示控制系统主要为基于ARM的嵌入式处理系统,通过人机交互界面对船用雷达的各个硬件模块进行控制,通过大尺寸的显示屏显示雷达图像。

嵌入式系统应用于船用雷达领域主要有如下的技术特点:实时性好,能够较好的满足船用雷达系统在特定工作情况下的实时要求,完成雷达不同功能切换;专用性强,嵌入式系统面向于船舶电子导航设备,因此硬件和软件都是专门针对船用雷达系统;可裁剪性好,嵌入式系统提供外部扩展的硬件模块和优化的软件系统,便于维护和升级;可靠性高,嵌入式系统能够在恶劣的环境下对雷达软硬件设备的稳定控制。

2 船用雷达显示机制分析

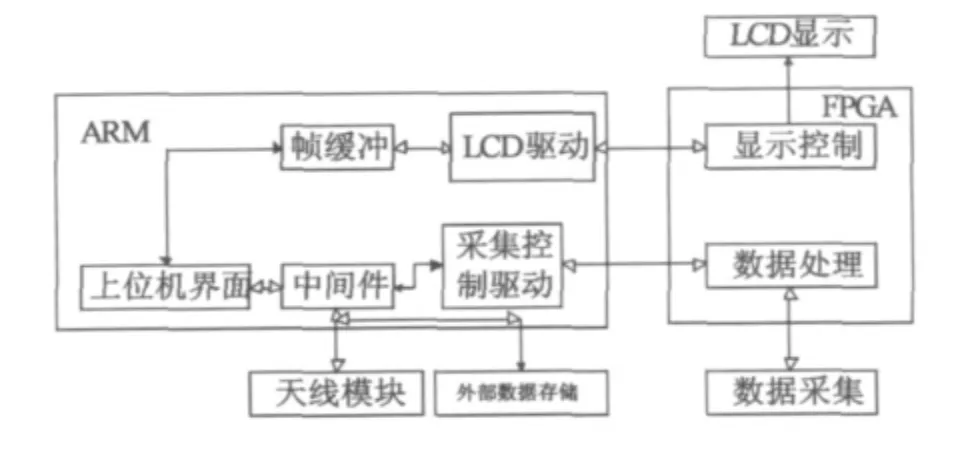

目前有两种船用雷达显示架构,一种是基于ARM加DSP的双核处理器架构,该系统主要将雷达的控制和图像显示放在ARM核的SOC中,通过SOC中自带的LCD控制器实现图像的显示,由DSP实现雷达数据的处理,处理好的数据通过通讯接口传入ARM进行显示,如图1所示,该架构的优点是使用双核架构的处理器,将数据处理和数据显示分离开来,充分发挥ARM和DSP的优势,最大限度提高系统效率,不足在于由于目前ARM核运行频率不高,使得系统总线上显示数据量不能太大,总线上的数据传输限制了LCD上数据显示大小,只能满足较小屏幕的显示需求。但考虑到现代船舶电子显示屏的需求,较大的屏幕能大大提高船用雷达的显示可靠性,因此大屏幕数据显示是船用雷达显示系统发展的需要。

图1双核处理架构

另一种是基于Intel处理器的工控机模块,整合了船用雷达各个模块,更像是一个高性能的PC机,该系统的优点是能够迅速的处理雷达数据并显示在大屏幕上,不足是由于工控机软硬件结构复杂,开发难度大,设备成本高和体积大等。

3 一种支持大屏幕的显示的设计

本设计由两部分组成:嵌入式ARM模块部分负责显示功能的驱动层操作,底层硬件的显示操作由FPGA完成,即将原来基于ARM的嵌入式处理器中的LCD控制器分离出,放在FPGA模块部分进行硬件层的显示操作。建立ARM与FPGA之间的异步数据传输机制,并通过该机制将嵌入式ARM部分关于雷达显示人机操作界面的数据图像发送到FPGA进行显示,并创建双核模块间的控制寄存器,实现ARM显示功能对FPGA硬件层的控制操作,使雷达图像在屏幕上扫描显示。FPGA就负责LCD控制器的底层数据调度显示,由于FPGA特有的高速并行数据处理的技术特点,使得能够进行大量的图像数据显示,因此能够支持雷达扫描图像的大屏幕显示,并减少嵌入式ARM处理器的运行负载,提高显控系统的运行效率,同时,FPGA也可以取代DSP完成雷达数据的数字信号处理。方案实现原理如图2所示。

图2 大屏显示方案

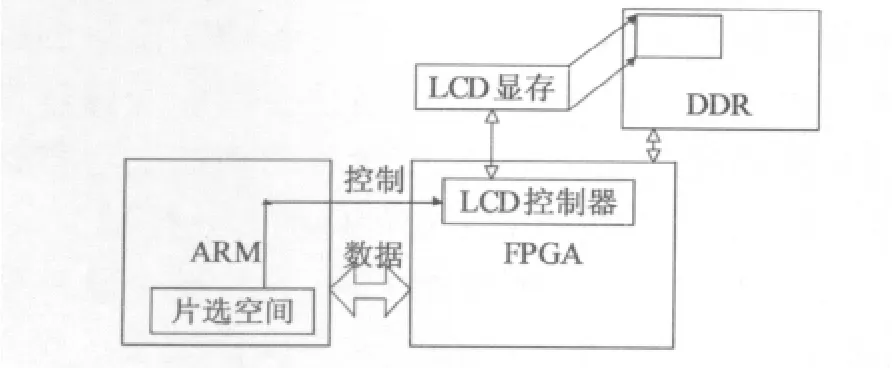

根据对图像显示机制的分析和讨论,本文提出了一种支持大屏幕船用雷达数字成像的显示系统解决方案,这一系统的整体数据传输机制原理如图3所示。

图3 数据传输机制

显示图像的数据通过 LCD驱动传送到外部的显存中,ARM系统中的图像数据空间映射到外部显存空间,由 FPGA硬件完成显示数据的显示刷新。实现显示图像的慢速数据交互,并进行高速数据的显示刷新,完成大屏幕雷达图像的高速显示。

4 软件驱动架构分析

整个船用雷达的软件整体框图如图4所示。

图4 软件整体框架

数据流分为2路:显示的雷达回波数据由人机交互界面开始,经过ARM显示系统的帧缓冲设备,通过LCD驱动层的数据传输,发送至底层硬件部分,进行图像的刷新显示;上位机对雷达各功能模块的控制指令由人际界面发出,经过雷达控制中间件软件进行控制调度,然后由采集控制驱动相应底层雷达硬件操作,完成上位机对底层硬件的有效控制。

根据整个雷达数据流的方向,设计整个软件架构,确定驱动层分为LCD模块和中间件模块。建立上位机和底层之间的高速、可靠的显示与控制通信机制,完成大屏显示。

4.1 LCD驱动模块设计

船用雷达LCD驱动模块主要负责上层嵌入式操作系统的统一应用层显示机制与底层FPGA显示硬件的数据通信连接,使得嵌入式船用雷达显示系统的上层应用程序的图像通过驱动层在底层硬件完成图像显示。整个模块包括雷达图像数据的高速传输、对LCD控制器功能寄存器的设定,以及对上层图像应用程序的接口设计。

LCD模块包括帧缓冲驱动的设计和LCD-FPGA驱动的设计。

帧缓冲作为linux系统为显示设备提供的一个软件接口,它的作用就是将传统的显示缓冲区抽象,屏蔽图像底层硬件差异,允许上层应用程序在一定的图形模式下直接对显示缓冲区进行读写操作,帧缓冲设备属于标准的字符型设备驱动。设备驱动结构如图5所示。

图5 帧缓冲驱动程序架构

LCD-FPGA驱动设计:在本设计中,显示部分的LCD控制器的设计集成在FPGA内部,通过ARM系统的系统总线实现与FPGA关于显存部分的数据通信,由FPGA外部的DDR分配一块显示缓冲区,将这片显存空间地址映射到ARM的片选空间,同时帧缓冲设备就可以对外部这片显存空间进行读写数据访问,实现上层应用空间对显示屏幕的用户直接操作,其原理见图6。

图6 LCD-FPGA显存分配

LCD-FPGA驱动的基本流程:

a.驱动加载采用平台驱动设备加载。

b.把FPGA的数据传输的地址做mmap映射,使用共享内存的方式,直接将FPGA显存的空间映射到用户空间,用户空间可以直接访问FPGA的显存空间,实现fb的内存映射功能。

c.驱动将从平台设备获取的LCD设备信息进行上层fb的参数设置,使得应用层能够使用。

d.注册framebuffer帧缓冲设备,该过程将前面设置的硬件接口参数,统一创建到对应的帧缓冲设备中,并自动创建fb设备节点。

e.驱动卸载包括注销平台设备、注销framebuffer帧缓冲设备,停止LCD显示,以及对FPGA显存的取消映射。

4.2 用户空间测试

将LCD-FPGA的驱动加载成功以后,操作/dev/fb0的帧缓冲设备文件,简单测试帧缓冲设备的用户空间的访问。测试的形式主要是写图片,由于底层硬件设置的分辨率为1024×768,像素位数是16位,所以文件的大小应与实际的硬件显存访问的空间大小相同,帧缓冲设备才能进行正确的数据读写,在显示屏幕上完整显示图片。具体的操作流程如图7所示。

图7 操作流程

a.打开帧缓冲设备文件,即打开/dev/fb0的设备文件;

b.通过ioctl()操作获得底层驱动的固定屏幕参数和可变屏幕参数,比如屏幕分辩率(1024×768),像素位数(16bit),计算硬件支持的最大屏幕缓冲区的大小。

c.将从底层获取的与硬件匹配的屏幕缓冲区的实际物理空间映射到用户空间,使应用层可以对这片空间直接进行数据读写。

d.在底层屏幕的物理空间映射成的用户空间可以直接进行图片数据的写入,将1024×768分辨率、16位像素的图片写入显示缓冲区,完成帧缓冲 设备的应用空间测试。测试结果如图8所示。

图8 雷达界面

5 结论

本设计以嵌入式架构为前提,通过优化ARM和FPGA的通信方式,使得性能较低的ARM芯片也能驱动大屏幕的显示,有效降低了船用雷达系统成本,通过低成本的嵌入式系统设计方案取代了高昂的工控机方案,本设计具有通用性,不仅仅局限于船用雷达,可适用于普遍大屏驱动的场合。

[1]杜春雷.ARM体系结构与编程[M].北京:清华大学出版社,2003,2.

[2]张润泽,船舶导航雷达,第一册,第二册.人民交通出版社,1987,6.

[3]雷琴,耿晨歌,陈耀武,汪乐宇.基于嵌入式的船载雷达系统软件设计.船舶,2003,(3).

[4]宋宝华,Linux设备驱动开发详解,人民邮电出版社,2008,2.

[5]Samsung Electronics.32-bit CMOS Microcontroller User's Manual.Revision 1.

[6]B.Cantrell,J.Degraaf,F.Willwerth.Development of a digital array radar(DAR)[J].IEEE Aerospace and electronics systems magazine,2002,17(3):22 -27.