一种COM EXPRESS模块处理器的设计与实现

张 博

(中国电子科技集团公司第五十四研究所,河北石家庄050081)

0 引言

处理器模块化是处理器的发展趋势,在处理器模块化的众多设计方法中,COM EXPRESS模块化处理器设计是模块化设计的一种新思路,具有灵活多样、性能稳定、兼容性好、功耗低和尺寸小的特点[1]。COM EXPRESS模块化处理器的应用领域非常广泛,如计算平台、通信、工业控制、医疗、交通和环保等领域。为了能够设计具有协处理器功能的处理器,并使其模块化,本文以AD LINK公司生产的COM EPRESS模块NANOX-ML-1024/4G为处理器的核心器件,以FPGA+单片机作为协处理器,利用COM EPRESS自主设计的灵活性,完成具有协处理功能的模块化处理器的设计与实现,验证 COM EXPRESS模块化处理器设计的可行性。

1 COM EXPRESS接口处理器设计方案

基于COME接口CPU模块的处理器由4部分组成:COME接口CPU模块部分、协处理部分(包括FPGA和单片机)、时钟分路和管理部分、电源和电源管理部分。[2]

处理器的设计原理框图如图1所示。

1.1 COM EXPRESS接口处理器硬件设计

根据处理器的要求,充分考虑芯片的处理能力、体积、功耗、集成度、成本以及开发环境因素,设计的处理器核心器件选择NANOX-ML-1024/4G,该器件为AD LINK公司生产的COM EPRESS模块,其性能如下:

·CPU型号:ATOM系列;

·主频:1.66 GHz;

·芯片组:INTEL485;

·内存:DDR2 1 GB;

·板上硬盘:4 GB;

·支持PCIe:2路1x;

·功耗:25 W。

COM EXPRESS模块NANOX-ML-1024/4G有丰富的外部接口,可以满足各种设计的需要。

1.2 COM EXPRESS接口处理器软件设计

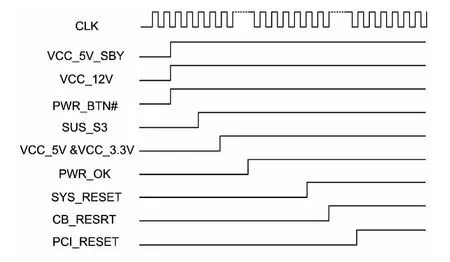

NANOX-ML-1024/4G复位启动关键信号的加电时序非常重要,直接关系到处理器设计的成败,时序错误会导致COM EXPRESS模块NANOX-ML-1024/4G不启动,使整个处理器不能正常工作[3]。关键信号的时序图如图2所示。

图2 处理器加电时序

为了监控关键信号的状态,将关键信号连接到FPGA中,通过对关键信号的控制监视,来观察处理器模块加电时信号状态的正确性,从而保证处理器能够正常工作。

为了满足该时序,通过FPGA编写程序控制信号的延时,保证信号的时序满足主板复位初始化启动时的关键信号的时序,进行正常启动。

处理器中COM EPRESS模块与FPGA之间通过PCIe总线互相连接,使用FPGA芯片的硬核程序编写FPGA芯片端的PCIe总线程序模块,完成COM EPRESS模块与FPGA之间的数据交换,形成FPGA对处理器的协处理结构。

2 设计中需要解决的问题

嵌入式处理器模块化对体积和功耗的要求比较严格,在有限的板卡空间内集成满足要求的硬件设计并能够将功耗设计到最小是处理器设计的难点。

本文中设计的处理器板卡尺寸为标准VPX接口的6U板卡(230 mm×260 mm),在板卡上结成了一个85 mm×120 mm的COM EPRESS模块和一个85 mm×130 mm的硬盘模块,要求在通用的处理器功能的基础上,使用PCIe总线作为纽带集成FPGA芯片进行协处理,设计成新型的处理器。高集成度和高速总线的信号完整性的矛盾与统一,是处理器设计需要解决的问题。

板卡的电源供给方式为AT模式,但是AT模式的电源功耗功耗比ATX模式大[4]。在板卡的电源供给方式不变的条件下,降低功耗也是处理器设计需要解决的问题。

3 关键技术

3.1 高集成度的高速总线PCB设计

PCB板设计过程中,尤其是高集成度、走线部分面积小、高速信号集中分布的板卡中,高速信号完整性的约束及后仿真是保证设计成功的重要因素[5]。在高速PCB板电磁兼容设计中,相近传输线上的信号之间由于电磁场的相互耦合而发生串扰,邻近信号线之间容易发生串扰,散热性差。

本设计中PCIe总线硬件部分是整板频率最高的地方,数据信号数据传输率(2.5 GHz)。以PCIe总线的设计来说明整板高速PCB的设计方法。

PCIe总线拓扑结构设计、布局布线设计都是影响PCIe总线接口性能的关键。处理器中PCIe总线控制器和FPGA之间的端接方式如图3所示。

图3 PCIe总线和FPGA之间的端接方式

该设计遵从了业界标准的SSTL25电平标准和SSTL25 Class I端接方式[6]。使用源端端接(Rs)消除高速信号的振铃问题,终端端接(Ct)用来解决反射现象,从原理设计上保证了PCIe总线高速信传输过程中的信号完整性。

去除信号本身的振铃和反射,信号线的特性阻抗也是影响信号质量的主要因素,因此,PCIe总线布线端信号线的线宽和PCB的叠层也是PCIe总线设计的关键。通过后仿真完成信号走线的阻抗设计,使用Cadence软件对PCIe总线建模仿真的结果图如图4所示。

图4 PCIe总线建模仿真的结果

由图4可以看出,信号接收端在第1个波形并未进入稳定状态(与稳定状态有约100 mV的压差),在第2个波形才进入稳定状态,并且信号驱动端有明显的过冲现象。从电压幅值可以看出,数据信号线有一定抗噪声能力,而此时的驱动端的过冲也在可以接受的范围之内。通过调整走线的线宽和PCB板的叠层并观察仿真结果,最终获得最终最佳的走线和叠层设计。当数据信号线的特性阻抗为75 Ω时,可以达到最好的仿真信号质量[7]。该仿真结论也验证了业界PCIe总线板级布线设计指南中对数据信号特性阻抗要求为75 Ω的结论。

3.2 模拟ATX电源模式降低功耗

供给给处理器的电源模式分为AT模式和ATX模式,其中 AT模式之提供给电源12 V,5 V,弱3.3 V,电源的供给不受主板控制,电源开关打开后直接供电,并且持续进行供电。ATX模式则是除了供给电源12 V、5 V、3.3 V 外,还提供一 STANDBY 5 V。通过处理器对电源的控制完成对电源供给开关的控制,当ATX模式的开关发送给处理器一个POWER_ON信号,开始预提供电压输出,处理器通过检测预提供的电压,根据本身复位初始化的完成反馈给电源模块PS_ON信号,ATX模式电源正常输出后,给处理器提供一个POWER_OK信号,处理器由电源检测进行正常工作电源模式。

处理器可以在ATX模式下进入休眠模式,电源12 V和5 V等电压只提供微弱得电流[8],处理器的功耗降低到最低,通过对 ATX模式的弱3.3 V、STANDBY 5 V的电流的控制,可以从网口、USB口和鼠标键盘口等使处理器从休眠模式中恢复。

使用AT模式电源,不能对处理器的加电时序进行有效控制,导致处理器电源一直处于正常工作状态,处理器不能进入休眠模式,所以功耗会一直比较大。为了解决这个问题,根据ATX模式的工作模式。

4 性能测试

处理器加电后系统正常启动,外围接口正常工作,处理器中PCIe总线的传输速率通过编写应用程序测试,处理器将N字节数据通过PCIe总线DMA方式I/O方式传输给FPGA芯片,并在开始发送数据的同时计录时间T1,FPGA芯片完成数据的接收后返回给处理器传输完成的标志和接收的数据,处理器收到完成标志后计录时间T2,回读从FPGA芯片传输来的数据,校验数据,保证传输的正确性。PCIe总线传输速率=N/(T2-T1),可以计算出实际总线的传输速率[9]。

使用P=UI测试功耗,通过改变处理器工作的模式分别测试处理器正常工作和休眠时两种模式,测试供给电压端的功耗。

其性能测试如下所示:

·CPU型号:ATOM系列;

·主频:1.66 GHz;

·内存:DDR2 1 GB;

·板上硬盘:4 GB;

·硬盘:500 GB;

·支持PCIe1x:2.5 Gb/s;

·PCIe总线传输速率:DMA方式1.94 Gb/s;I/O方式0.5 Gb/s;

·功耗:正常工作25.5 W;休眠模式15.3 W;

·USB口:4路2.0标准;

·显示器:2路LVDS接口,显示正常;

·网口:1 000 Mb/s,正常工作;

·FPGA芯片与COM EPRESS模块通信:正常通信;

·鼠标键盘:正常工作。

5 性能测试结果分析

COM EXPRESS模块处理器能够正常启动、正常驱动显示电路、驱动外围接口、正常启动操作系统、完成通用处理器的功能,并能够通过PCIe总线与FPGA进行通信,完成协处理器的功能,满足处理器的要求。使用标准的COM EXPRESS接口通过PCIe总线扩展了FPGA协处理器的功能,能够灵活的设计集成处理器与其他功能模块,形成新功能的处理器。

解决了高速总线与集成度的问题,通过PCIe总线的传输速率验证了PCB设计的正确性。根据PCIe的总线8b/10b转换效率,1x 2.5 Gb/s PCIe总线实际传输的理论值为 2.5 Gb/s×0.8=2.0 Gb/s。由于处理器系统架构带来的非实时性影响[10],PCIe总线速率与理论速率相近。通过PCB硬件高速总线设计方法和后仿真的方法成功的解决了高速总线与集成度的问题,实现了硬件的集成,保证了数据的传输质量[11]。

根据测试结果证明,设计解决了处理器AT电源模式功耗大的问题,正常工作模式和休眠模式的功耗相差10 W,处理器在非频繁工作时节约大量的功率开销。

6 结束语

基于ADLINK公司的COM EXPRESS模块NANOX-ML-1024/4G为硬件核心,使用FPGA芯片完成了COM EXPRESS模块化处理器的实现,解决了具有协处理功能的处理器的需求。由于COM EPRESS接口的标准化,该处理器在通用性、可升级型上具有非常大的优势。同时也验证了COM EXPRESS模块化处理器在设计上灵活自主的设计理念,将处理器的设计从单一化向多元模块化发展,能够适应不同层次对处理器功能的不同需求,为设计具有新功能的处理器提供了优良的解决途径。

[1] FERREIRA J C,SILVA M L.Generation of Hardware Modules for Run-time Reconfigurable Hybrid CPU/FPGA Systems[J].Computers & Digital Techniques,IET,2007(9):461-471.

[2] CHANGB.探索 ETXexpress以兼容 COMexpress[J].世界电子元器件,2006(11)85-85.

[3] 广州致远电子股份有限公司.嵌入式计算机模块(COM Express)设计[J].电子产品世界,2012,(11):15.

[4] EDN.可扩展多核嵌入式处理器优势凸现[J].电子设计技术,2007(5):18-18.

[5] 丛秋波.可扩展处理平台为嵌入式系统提供卓越性能[J].电子设计技术,2010(7):16 -17.

[6] 程保炜,刘文珂.嵌入式系统及其开发应用概述[J].长江大学学报(自然科学版),2004(4):77-80.

[7] 姚锡忠.嵌入式系统及其发展趋势的分析与研究[J].科技信息,2009(31):36-40.

[8] 沈 兰.浅论嵌入式系统及其发展[J].科技资讯,2008(22):247-248.

[9] 刘春晓,王 黎.抑制PCB对直流电源噪声干扰的滤波器设计[J].无线电工程,2011,41(4):59 -61.

[10]钱建波,于正永.基于嵌入式技术的自助系统研发[J].无线电工程,2011,41(11):7 -9.

[11]文 豪.CRN中一种优化的数据传输方案[J].无线电通信技术,2012,38(5):43-46.