基于DDS技术的线性调频脉冲信号的产生

王冉,金繁

(北方工业大学 信息工程学院,北京 100041)

频率合成技术就是把一个或者多个高稳定度、高准确度的参考频率,经过各种信号处理技术,生成具有同等稳定度和准确度的各种离散频率。参考频率可由晶体振荡器产生,合成的离散频率与参考频率有严格的比例关系,并具有同等的稳定度和准确度。频率合成技术是实现高性能频率源的重要手段。频率源的性能是影响雷达、电子对抗、仪器仪表等系统性能的关键问题[1]。

传统的频率合成技术如直接模拟频率合成技术因采用了大量的分频、混频、倍频和滤波等模拟元件,使合成器的体积大、易产生杂散分量、元件的非线性影响难以抑制。再如基于锁相环(PLL)的频率合成技术,由于PLL有惰性,频率分辨率和频率转换时间相互矛盾 (难以兼顾);频率转换时间较长;压控振荡器引起的噪音也较大。随着数字电路和数字信号处理技术的发展,近年来DDS(直接数字频率合成)技术由于其是全数字化结构,易于集成、功耗低、体积小、重量轻、可靠性高、易于程控、使用灵活,性价比很高,故广为采用[2]。

本文提出了一种基于 FPGA的 DDS实现[3]方法,基于ROM查找表,对相位控制字的处理来进行各种频率信号的发生,最后产生了一种4路线性调频脉冲信号,经过仿真和对合成后的数据用matlab分析[4]得出,虽然DDS技术的输出带宽有限,但是经过多路处理也能够有效提升输出信号带宽。

1 DDS(直接数字频率合成)技术的基本工作原理

1.1 DDS的基本构造

如图1所示,完整的DDS可分为内部器件和外部器件两部分,其中内部器件由相位累加器和正余弦查找表构成,为了输出模拟波形,还需加入外围器件,包括DAC(数模转换器)和低通滤波器。为了抑制DDS的输出杂散,还可以使用DDS+PLL的频率合成方法。

图1 DDS基本结构Fig.1 DDS basic structure

1.2 DDS的基本工作过程

如图1,DDS的基本工作过程为:a)根据所要输出的频率来确定频率控制字;b)对频率控制字进行循环累加;c)将相位寄存器锁存相位信息与相位控制字(初始相位)相加;d)截断相位信息的高位做ROM的寻址地址;e)从ROM输出的数据经过DAC形成模拟量波形;f)DAC输出的阶梯形波形,经过低通滤波,成为模拟波形。

参考频率源(fc)一般是高稳定的晶体振荡器,用于DDS中各部件的同步工作,因此DDS输出的合成信号频率稳定度与晶体振荡器是相同的。在标准频率参考源的控制下,频率控制字K可决定相应的相位增量,相位累加器则以步长M进行线性累加,相位累加器积满时就会产生一次溢出,从而完成一个周期性动作,这个动作周期即是DDS合成信号的一个周期。通常N位相位累加器的最小值为0,最大值为2N-1,故最后输出信号的频率为Hz,频率分辨率的大小为Δf=fc/2N。实际运用中,根据实际需要所计算出的M很难为整数,因此不可避免地会存在频率误差。如将计算出来的K的小数部分舍去,那么最终输出信号的频率误差不超过频率分辨率Δf;如果将M的小数部分四舍五入,则频率误差不会超过0.5Δf。其中采用了32位相位累加器,以及10位ROM查找表。

DDS技术可以理解为数字信号处理中信号综合的硬件实现问题,即给定信号幅度、频率、相位参数,产生所需要的信号波形,也可以认为是给定输入时钟和频率控制字K,输出一一对应的正弦信号。由于DDS采用了不同于传统频率合成方法的全数字结构,所以它具有直接模拟频率合成和间接频率合成方法所不具备的一些优点。

输出的频率的计算公式[5]如下:

其中,fout为输出频率,fc为采样时钟,N为相位累加器位宽,M为频率控制字。

假设正余弦查找表的深度为1 024,采样时钟为100 MHz,则输出一个完整的ROM表正余弦信号的频率就为Hz=97 656.25 Hz=97.656 25 KHz,由采样定理可知理论输出的最大频率为50 MHz,由此可见DDS的带宽是受到采样率的影响的。由于正余弦查找表相位截断时会影响下一周期信号的初始相位,所以DDS的杂散不是很好,用DDS+PLL的合成方法,就能解决这一问题。PLL锁相环可以将采样时钟倍频到很高的程度,而且波形相位问题也能解决。

2 DDS的实现

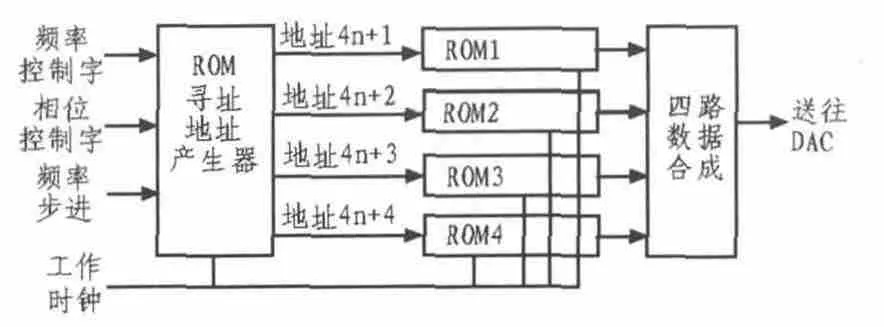

在FPGA上实现了图1中所说的内部器件,由于采样率为1 GHz,在FPGA中不能跑到那么高的频率,所以采用了4路同步采样的策略来降低工作时钟,最后将四路信号再合成一路完整的信号输出。如图2所示。

图2中,频率控制字可有式(1)反推求的 M(频率控制字);相位控制字由相位偏移量公式[6]:

图2 四路同步寻址DDS原理框图Fig.2 Block diagram of four simultaneous addressing DDS

反推求得,这里相位控制字控制寻址的初始相位,我们一般设置为0,需要进行相位调制时再对其进行处理;频率步进是用来产生频率逐渐变化的信号波形的,如线性调频信号,步进频信号,频率上的三角波及锯齿波信号等等一些有用波形信号,其推导公式如下:

频率步进字

其中,带宽为在有效脉冲之间的频带宽度,时宽为有效脉冲持续时间,为采样频率(注意,这里的采样频率并不是指工作时钟,而是指ADC采样并下变频后得频率,为四路时钟之和)。

3 线性调频脉冲信号的产生及仿真结果

线性调频信号是通过非线性相位调制或线性频率调制获得大时宽带宽积的典型例子。通常把线性调频信号称为Chirp信号,它是研究最早而且应用最广泛的一种脉冲压缩信号。多用于雷达发射信号中,可以达到增大信号带宽,也就是增大信号信息携带量,更有利于防止敌方窃取信号信息用来干扰雷达,雷达脉冲有效宽度,也就是信号时宽是影响雷达分辨率的主要因素,带宽和时宽是相互矛盾的,所以只有根据不同雷达的用途,权衡利弊来确定时宽带宽积,以达到预期的效果[7]。

根据以上分析,运用设计的四路DDS产生了线性调频脉冲信号,设计中的参数如下:相位控制字Poffset=0,即初始相位为0,也就是每个脉冲有效信号来时,寻址地址为ROM查找表的第一个地址;由于采样率定为1 GHz,所以带宽需小于500 MHz才能满足采样定律,但是一般情况下带宽需小于采样率的40%,所以为了简便起见,设定带宽为100 MHz,由此可知首先在脉冲来时输出的频率为50 MHz,由线性调频信号的特性可知,其频率由大变为0再变大。由于实验中为了方便起见,设定时宽为500个工作时钟,即2 000 ns,由此可以推导出频率步进值,下图即为上述参数所确定的四路经正余弦查找表得到的波形的其中一路。

其他三路正交信号与图3中信号类似,将四路信号合并成一路IQ正交信号,然后将其中I路信号存入文件中待Matlab仿真使用。以下是Matlab仿真[8]的一个脉冲有效时间的波形,时域特性如图4所示,频域特性如图5所示。

图3 第一路IQ正交线性调频信号Fig.3 First road IQ orthogonal linear FM signal

图5 单脉冲信号频域特性Fig.5 Single pulse signal frequency-domain characteristic

4 结束语

随着电子科学与技术的发展,数字电路发展越来越快,许多以前只能靠模拟器件完成的工作,如今都可以放在可编程逻辑器件中实现,这一发展大大提高了电路的灵活性和可控性,也使得电路的规模一再扩大又不至于影响器件大小,由以上分析可知,在FPGA中实现DDS不仅电路简单,可控性高[9],而且灵活多变易于修改,基于Verilog硬件编程语言的程序具有良好的可读性和可移植性,在QUARTUS II或ISE集成开发环境下,各种基于小模块合成的复杂逻辑应运而生,采用了基于ROM查找表的方法实现DDS信号发生,并在matlab中将所得信号作时频域分析,验证了其功能的可靠性,可更好的理解DDS的基本原理,也可直接使用上述两种开发软件所提供的DDS IP CORE来进行设计。

[1]吴顺君,梅晓春.雷达信号处理和数据处理技术[M].北京:电子工业出版社,2008.

[2]张顺兴.数字电路与系统设计[M].南京:东南大学出版社,2004.

[3]施国勇.数字信号处理FPGA电路设计[M].北京:高等教育出版社,2010.

[4]Ingle U K,Proakis J G.数字信号处理(MATLAB版)[M].西安:西安交通大学出版社,2008.

[5]DDS算法百度百科 [EB/OL].http://baike.baidu.com/view/1554444.htm

[6]张先志.基于DDS技术的线性调频信号的生成[J].现代电子技术,2008,15(1):30-31,35.ZHANG Xian-zhi.Generation of chirp signal based on DDS technology[J].Modern Electronics Technique,2008,15 (1):30-31,35.

[7]胡可欣,胡爱明.线性调频信号特征分析[J].空间电子技术,2007,1(1):56-59.HU Ke-xin,HU Ai-ming.LFM signal analysis[J].Space Electronic Technology,2007,1(1):56-59.

[8]刘美丽.MATLAB语言及应用[M].北京:国防工业出版社,2012.

[9]赵志伟,陈学有,潘琼.采用特征值法和Prony法相结合的PSS自适应控制[J].陕西电力,2012(6):49-52,62.ZHAO Zhi-wei,CHEN Xue-you,PAN Qiong.Adaptive control of pss based on eigen value analysis and Prony analysis[J].Shaanxi Electric Power,2012(6):49-52,62.