基于SOPC的电网参数监测装置的设计

周国栋,陈 迅,曹珍珍

(江苏科技大学 电子信息学院,江苏 镇江 212003)

随着用户用电量需求的不断增加,与各种大容量非线性负载的投入使用,使得电力系统的谐波污染越来越严重[1]。传统电网监测装置大多采用单片机,或基于数字信号处理器(DSP)及ARM处理器实现[2],这些系统开发周期长,系统升级困难,而采用MicroBlaze软处理器的SOPC技术弥补了上述不足。

文中设计了基于Xilinx公司FPGA的SOPC电网参数监测装置。该装置将FPGA硬件逻辑具有的快速并行执行能力和MicroBlaze软处理器的灵活性相结合,前者保证了数据处理的实时性,后者则实现了前者不易实现的功能。该监测装置可实时监测三相电网电压电流有效值、各次谐波含有率、有功功率、无功功率和功率因数等电网参数。

1 SOPC及MicroBlaze简介

SOPC(System on a Programmable Chip),即可编程片上系统[3]。它是一种特殊的嵌入式系统,将CPU、存储器、I/O口等系统设计所需要的功能模块集成至一片FPGA芯片上,构成可编程的片上系统,完成传统嵌入式系统所能完成的任务。SOPC设计灵活,具备软、硬件系统均可在线编程的特性,因而系统升级容易。还可根据实际功能需求进行功能模块的裁剪。它占用面积小,可腾出更多面积给电路板上的其它外围电路使用。

MicroBlaze嵌入式软核是一个被Xilinx公司优化过的可以嵌入在FPGA中的RISC处理器软核[4]。它采用传统的单处理器方法进行的基础设计,配合Spartan-3E系列FPGA在80MHz的时钟频率下,性能达到 68 Dhrystone MIPS(DMIPS),运行速度快的同时占用资源少,可配置性强[5]。用户可以从PPC405,PPC440和MicroBlaze这 3种内核处理器中选择一款合适的处理器。PPC405和PPC440是内嵌在Xilinx高端FPGA中的硬核处理器,工作频率更高,性能更佳,灵活性稍差;MicroBlaze是软核处理器,一般用于低成本的FPGA上,较之前者工作频率较低,性能稍差,但灵活性很强。除此之外,用户还可以从多个已经归类的外设IP核和用户自定义IP核中进行选择 (IP核指具有知识产权的集成电路设计模块),以构成可裁剪的SOPC系统。

2 监测装置总体设计

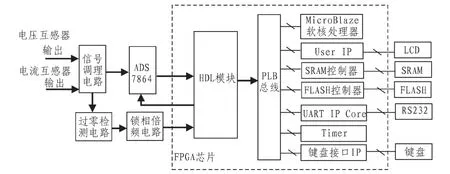

监测装置主要由信号调理电路、过零检测电路、锁相倍频电路、模数转换(A/D)电路、FFT运算单元、CPU处理单元、LCD显示、键盘等模块构成。实现对三相电压电流有效值、有功功率、无功功率、功率因数和各次谐波含有率等参数的测量与本地显示及数据传送。

三相电压三相电流六路信号,经电压互感器、电流互感器变换,经信号调理电路(转换、滤波、电平值提升)处理后,提供给模数转换芯片ADS7864进行采样和转换。在信号调理电路中经滤波后的信号,提供给过零检测电路,输出的方波经锁相倍频电路,输出的信号作为ADS7864开始工作的触发信号。

谐波参数的计算采用傅立叶变换算法 (FFT)实现,该FFT算法由Xilinx公司成熟的FFT IP核完成。该FFT IP核由 ISE(Xilinx软件集成开发环境)工具 Core Generator,根据计算精度需求和芯片逻辑资源,综合判断后配置生成。在50 MHz的时钟频率下,完成一次512点的FFT运算只需要65.7μs,可实时在线计算六路电网信号的谐波。

FFT处理后的数据存入输出双口RAM,当六路信号的FFT计算完毕存入输出双口RAM后,产生一个外部中断,通知MicroBlaze软处理器来取走数据,做一些简单的数据算术处理。最后将处理结果送给本地LCD显示,或通过RS-232传给上位机做进一步的数据分析与处理。监测装置原理图如图1所示。

图1 监测装置总体结构框图Fig.1 Overall structure diagram of monitoring device

3 硬件电路设计

3.1 信号预处理电路

AD转换芯片只可接受其可接受量程范围内的信号,因而在信号采样前须对输入信号做必要的预处理,主要包括信号隔离转换电路,滤波电路,电平值提升电路。信号隔离转换电路完成强电转换成弱电的过程,滤波电路滤除电网高次谐波,以免造成后期信号处理时出现频谱混叠,而电平提升电路,将电平值提升至ADS7864可接受的电平值。另外,电网频率在50 Hz上下波动,为了使AD芯片能在均匀时间间隔内对输入信号进行采样,须进行频率跟踪,以免频谱泄露。经过滤波电路后输出的电压信号,通过过零检测电路和锁相倍频电路实现频率跟踪技术,实时准确地采样和转换输入信号。

3.2 A/D转换模块

A/D芯片采用德州仪器TI公司的ADS7864,它内含两个12位,2μs的逐次比较型模数转换器,6个全差分采样保持放大器[6]。ADS7864具有6个模拟输入通道,被分为3组(A,B和 C),每个 A/D 转换器对应 3 个输入 A0、B0、C0和 A1、B1、C1,能同时进行采样和转换。将三相电压分别接至A0、B0和C0,三相电流分别接至A1、B1和C1。每组输入对应一个控制信号nHOLDA,nHOLDB和nHOLDC,将这3个控制信号接到一个控制信号nHOLDX上,可以允许6个通道同时采样。通过拉低控制信号nHOLDX至少15 ns,转换开始。转换过程中,输出信号nBUSY将会出现3个负脉冲,分别表示每组数据转换完成。6个通道的转换结果分别保存在6个输出寄存器上。拉低读取信号nRD和片选信号nCS来读取寄存器并行输出总线上的数据。输出值由16 bits组成,最高位为’1’表示数据有效,接着3 bits用来标示6个通道,低12 bits为转换值。输出寄存器数据读取模式有3种:单通道读取,循环读取和FIFO模式,通过控制信号线A0,A1,A2实现。本设计采用循环读取模式,第一个负脉冲nRD到来时读取A0寄存器值,第二个负脉冲nRD到来时读取A1寄存器值,以此类推,循环读取 B0、B1、C0和 C1寄存器值。

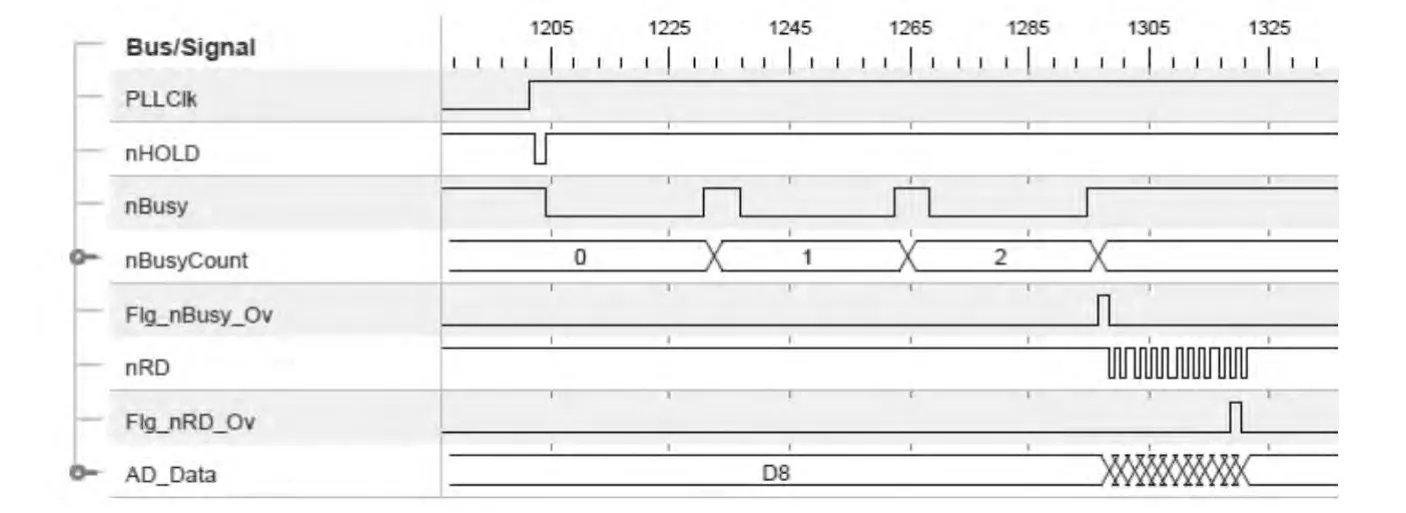

根据ADS7864 datasheet上的工作时序图,编写状态机控制。该状态机控制器用HDL硬件描述语言综合实现。图2为通过ISE片内逻辑分析仪工具ChipScope捕捉到的该控制器的实际工作波形。控制过程如下,在系统复位reset信号下,状态机进入初始化状态,设置读取模式等参数,然后无条件进入IDLE状态等待转换。当FPGA内的边沿检测模块检测到锁相倍频电路的输出信号PLLCLK的上升沿时,产生一个负脉冲送给nHOLDX,转换开始,进入转换状态。nBUSY信号出现第一个负脉冲表示第一组通道A0和A1转换完成,第二个负脉冲表示第二组通道B0和B1转换完成,第三个负脉冲表示第三组通道C0和C1转换完成。对nBUSY负脉冲计数,达到3时Flag_nBUSY_Ov产生一个脉冲表示所有通道转换完成。接着状态机进入读取状态,由于事先将byte信号接至高电平,为字节读取模式,因此6个通道的转换值需要读取12次。在12个nRD负脉冲作用下,AD_Data出现了12个字节数据,依次构成6个通道的高低位部分。当Flag_nRDv由0变为1时读取完成,回到IDLE状态,等待触发信号PLLCLK上升沿的到来。

图2 ADS7864采样控制器的实际波形Fig.2 Actual waveform of ADS7864 sampling controller

3.3 FPGA电路

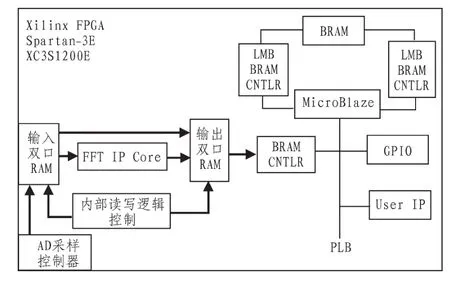

谐波参数通过FFT算法计算,该算法使用Xilinx逻辑IP核FFT IPCore实现,该IP核是经过成功验证的高性能低功耗的集成设计模块,能高效进行离散傅里叶变换[7]。FFTIPCore的I/O数据流采用基-2 Burst I/O结构,设置点数为512点,数据格式为定点,数据输出顺序为自然顺序。如图3所示,为FFT IPCore例化模块方框图。

图3 FFT IPCoreFig.3 FFT IPCore

如图4所示,A/D控制器控制外部ADS7864采样转换数据,将转换值读取至输入双口RAM。内部读写逻辑控制模块通过控制FFT读取输入双口RAM中的数据计算谐波,当FFT计算完毕,内部读写逻辑控制模块将FFT计算结果存入输出双口RAM。另外,ADS7864采样的三相电流电压原始值通过一个数据通道存入输出双口RAM,以供后续计算电流电压有效值、有功功率、无功功率和功率因数等。MicroBlaze嵌入式系统总线PLB上挂有Bram控制器 (BRAM CNTLR),BRAM CNTLR的一端与PLB总线连接,另一端与输出双口RAM连接。当输出双口RAM中的数据准备好后,以中断方式通知MicroBlaze处理器取数据,MicroBlaze通过操纵BRAM CNTLR的地址指针来读取输出双口RAM中的数据,然后进行一些算术运算,求三相电流电压有效值、各次谐波含有率、有功功率和无功功率等参数,最后将求得的结果送给本地LCD显示或通过RS232总线送给上位机进行进一步数据分析与计算。

3.4 键盘和显示单元

图4 FPGA电路图Fig.4 Circuit of FPGA

键盘、显示单元负责人机对话。MicroBlaze处理器将处理后的数据送给LCD,实时显示参数信息。LCD型号采用LCD1602,该LCD只需7根信号线进行控制,这7根控制信号线分别为读写控制信号RW,数据/指令识别信号RS,使能信号E,4位数据总线DB0-DB3。在Xilinx的XPS嵌入式开发平台上通过CIP(Create or Import Peripheral)工具设计用户自定义LCD IP核,在该IP核参数配置选项中勾选一个8位的软件寄存器,低四位对应4位数据总线,高四位对应控制线。由于用户自定义IP核不是Xilinx公司提供的现成IP核,所以需要自己编写相应的驱动程序供应用程序调用[8]。例如,编写LCD初始化函数,清屏函数,文本设置函数等。根据LCD1602读写时序,由MicroBlaze控制寄存器进行数据显示。通过键盘按键操作来切换屏幕显示不同相电力参数值。

4 监测装置软件设计

软件部分包括FPGA HDL程序和MicroBlaze嵌入式C程序。HDL程序在Xilinx集成开发环境ISE中完成,使用Verilog HDL硬件描述语言编写代码,并编写相关测试代码进行功能验证[9-10]。Verilog HDL硬件模块由以下几部分构成:A/D采样控制器模块、FFT IPCore模块、输入双口RAM与输出双口RAM模块和内部逻辑读写控制模块,这些硬件模块在系统时钟节拍的驱动下按照逻辑时序有序运行。首先A/D控制器将ADS7864转换后的数据送入输入双口RAM,通过内部读写控制逻辑将输入双口RAM中的数据送给FFT运算,处理的结果以中断的方式通知MicroBlaze处理器读取。

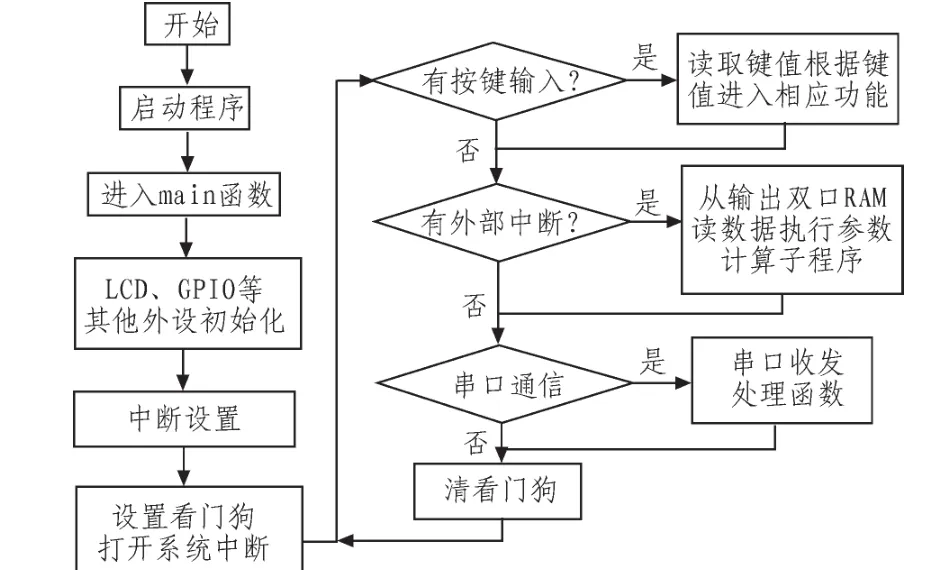

MicroBlaze从输出双口RAM获得数据后,用C语言编写代码计算三相电压有效值、电流有效值、各次谐波含有率、有功和无功功率等参数。MicroBlaze软件设计采用模块化设计方法,由初始化模块、数据计算模块、通信显示模块等构成。采用模块化设计提高了程序可读性,并且利于今后扩展和维护。Xilinx嵌入式软件开发环境SDK具有完整的软件开发流程,既有标准的C/C++编程界面也有丰富的调试界面。既可以选择 XMD(Xilinx MicroBlaze Debugger)命名行调试,也可以选择GND(GNU Debugger)代码界面调试(设置中断点、单步和连续运行等)。选择GND方式调试时,XMD扮演中间媒介角色,一端连接GND,另一端通过JTAG电缆连接挂在MicroBlaze系统总线上的MDM(MicroBlaze Debugger Module)模块,实时在线调试系统。参数计算结果既可以送给本地LCD显示,也可以通过RS232传给上位机做进一步数据分析与计算。MicroBlaze软件程序流程图如图5所示。

图5 MicroBlaze软件程序流程图Fig.5 Flow chart of MicroBlaze software program

5 结 论

MicroBlaze是一个功能强大,应用灵活的嵌入式软处理器,特别是其强大的用户自定义IP核功能,极大地方便了系统设计。基于嵌入式软处理器的SOPC开发方法,将拥有广阔的应用前景。本文采用FPGA逻辑设计与MicroBlaze软处理器相结合的方法设计了电网参数监测装置,基于该装置,可以实时在线监测三相电网电压、电流、谐波、有功功率、无功功率等参数。

[1]德拉罗萨.电力系统与谐波分析[M].赵琰,孙秋野,等译.北京:机械工业出版社,2009.

[2]沈伟,谢拴勤.基于DSP的电能质量监测系统设计[J].计算机测量与控制,2008,16(9):1240-1242,1261.SHEN Wei,XIE Shuan-qin.Design of power quality monitor system based on DSP[J].Computer Measurement&Control,2008,16(9):1240-1242,1261.

[3]杨强浩.基于EDK的FPGA嵌入式系统开发[M].北京:机械工业出版社,2008.

[4]Xilinx.MicroBlae Processor Reference Guide[EB/OL].(2012).[2013].http://www.xilinx.com.

[5]Xilinx.Spartan-3E FPGA Family Data Sheet.[EB/OL].(2012).[2013].http://www.xilinx.com.

[6]TI.ADS7864数据手册.[EB/OL]. (2005)[2013].http://www.ti.com.cn/product/cn/ads7864.

[7]赵永新,夏荣,罗卫湘,等.基于高性能FPGA的快速并行FFT及其在谐波监测上的应用[J].制造业自动化,2008,30(8):82-83.ZHAO Yong-xin,XIA Rong,LUO Wei-xiang,et al.The highspeed collateral FFT of high-powered FPGA and its application on harmonic waves monitor[J].Manufacturing Automation,2008,30(8):82-83.

[8]Xilinx.Device Driver Programmer Guide[EB/OL].(2012).[2013].http://www.xilinx.com.

[9]王钿,卓兴旺.基于Verilog HDL的数字系统应用设计[M].北京:国防工业出版社,2007.

[10]吴继华,王诚.设计与验证 Verilog HDL[M].北京:人民邮电出版社,2006.