双口RAM在航天伺服系统中的应用

于 戈,胡翔宇,曾凡铨,冯 伟

(1.上海航天控制技术研究所,上海 201109; 2.上海市伺服系统工程技术研究中心,上海 201109)

0 引言

在运载火箭系统中,发动机喷管采用伺服机构驱动其摇摆,近年来,大功率航天电动伺服机构技术在国内外得到了深入研究,电动伺服系统的综合性能已逐步超越了液压伺服系统,得到了越来越多的应用[1]。在电动伺服系统中通常采用电机作为能量转换元件,永磁同步电机因具有高功率密度、高效率和高可靠性等优点得到了广泛应用。然而,作为一个强耦合、多变量的非线性系统,永磁同步电机在控制过程中必须执行复杂的解耦控制算法。

伺服控制器作为驱动单元的核心,要求具备很高的硬实时性和充分的可靠性。伺服控制过程通常需要反馈信号采集、伺服控制算法计算和通信等功能,整个任务的控制周期决定了伺服系统的采样率,而高速的采样率能明显提升系统的动、静态性能。另一方面,随着控制算法的复杂化和通信的高速化,考虑到军用元器件使用的局限性,通常单中央处理器(Central Processing Unit, CPU)难以满足功能需求。

在航天伺服系统中通常具有单台控制器驱动多路伺服机构的特点,这给伺服控制计算单元提出了更高的要求。当前在伺服控制系统中,基于CPU+FPGA的架构已经成为热门方案[2],在CPU和现场可编程门阵列(Field-Programmable Gate Array, FPGA)间多采用双口随机存取存储器(Random Access Memory, RAM)进行数据传输实现数据的缓存和共享,高速可靠的数据传输成为系统的关键单点。现有防止双口RAM访问冲突的方式各种各样,有基于旗语逻辑的令牌仲裁方式[3-5]、中断等待方式[6-7]、优先级抢占方式[8-9]、循环缓冲方式[10-14]等。其中令牌仲裁方式和优先级抢占方式类似,设计了双口RAM数据访问的优先级机制,经握手后确定访问顺序,优先级低者需进行等待或再次请求,一方面增加了握手等待时间,一方面需要进行等待,占用了CPU利用率。中断等待方式占用了CPU的高优先级中断资源;循环缓冲方式机制复杂,建立缓冲机制的开销往往占用较长的CPU时间,适用于大量数据传输的系统中。

综上可知,双口RAM的防冲突机制都是为了不在同一时刻占用同侧总线和同一存储空间。本文直接从最根本的访问时间出发,基于DSP+FPGA架构,在FPGA内部实现了一个双口RAM,提出了一种分时访问机制,减少了等待握手环节和CPU使用率,缩短了伺服控制周期,框架设计简单清晰,保证了数字信号处理器(Digital Signal Processor, DSP)和FPGA间数据高速无差错的传输。

1 系统设计与需求分析

1.1 伺服系统方案设计

本文中伺服系统的架构如图1所示,主要由DSP、FPGA和双口RAM组成,各个模块的主要功能如下:DSP作为主处理器,主要实现读取双口RAM中的数据执行伺服控制算法计算,并将遥测数据写入双口RAM中,同时在每次中断执行开始时刻发出同步信号给FPGA;FPGA作为协处理器,主要实现反馈数据的采样和通信指令的解析,同时将伺服控制用的数据写入双口RAM,并从双口RAM中读取遥测和自检数据并上传;双口RAM作为数据缓存的桥梁,实现DSP和FPGA之间的数据双向传输。

图1 伺服系统架构图Fig.1 Servo system frame

基于双口RAM的数据传输分为上行数据传输和下行数据传输,上行数据传输指DSP将需要进行遥测的数据写入双口RAM的A端,FPGA从双口RAM的B端读取遥测数据;下行数据传输指FPGA将控制算法需要的反馈数据和指令信息写入双口RAM的B端,DSP从双口RAM的A端读取控制算法需要的数据。其中,下行传输的数据包括反馈采样数据和通信指令数据,反馈采样数据分别来自ADC模块和RDC模块,通信指令数据包括两路1553B总线通信的指令消息。上行和下行传输数据地址分配分别如表1和表2所示。在航天伺服系统中,指令和反馈数据对整个航天器的运行至关重要,数据传输不允许出现错误,遥测数据表明了当前系统状态,数据出错会影响系统运行状态的判断。

表1 上行传输数据地址分配

表2 下行传输数据地址分配

1.2 双口RAM中数据传输的关键问题分析

在硬件双口RAM器件中具有2套独立的访问控制总线,该2套总线共享数据存储空间,当两侧的总线在同一时刻对同一数据存储空间进行写数据,或一方总线对数据空间写、另一方总线对该空间读时,该地址空间访问数据产生竞争,此数据空间的数据会出现乱码,应当避免这种情况的发生[15]。为了保证通信的可靠性,当2套总线同时访问双口RAM的同一地址空间时需要进行握手等待,这种握手机制会增加访问双口RAM的时间,当数据传输量较少的情况下,握手机制将占用总访问时间的一半以上,且握手机制会占用额外的中断或者是查询时间,增加CPU负担。特别是在伺服系统中,伺服控制算法的运算周期决定了其最终性能,因此要最大程度地减少数据传输时间和降低CPU任务负担。

由表2可以看出,本系统中由FPGA传输至DSP的下行传输数据来自多个FPGA的功能模块,这些数据需要按照规定的地址编码放入下行传输数据空间内。当多个模块对双口RAM单侧进行访问时,同样需要设计合理的仲裁逻辑避免同时占用总线。类似于双口RAM双侧访问机制,设计合理的总线访问机制有助于简化程序架构,提高FPGA对内部双口RAM的写入和读取时间,提高采样率和通信速率。

2 双口RAM设计实现

2.1 框架与接口设计

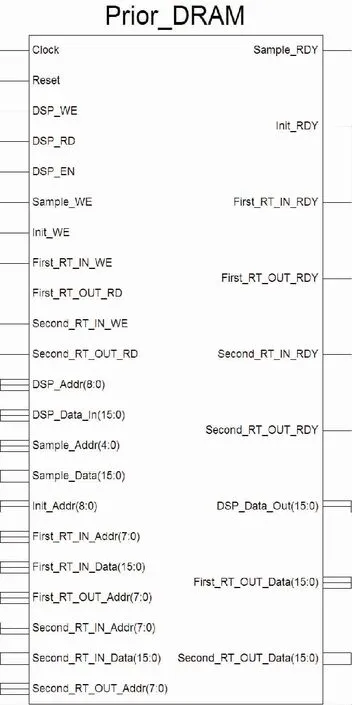

按模块化设计方法,本系统将双口RAM设计为2个模块,顶层模块为Prior_DRAM,例化的子模块为Dual_Port_Memory,顶层模块完成双口RAM与其访问功能模块的接口设计。如图2所示,各个模块对FPGA侧总线的访问均具备独立的数据地址总线和控制信号。图2中,左侧信号位输入信号,右侧信号位输出信号。

图2 顶层模块接口图Fig.2 Top level module interface diagram

子模块负责上行和下行传输数据的存储,接口如图3所示,具备2套独立的数据地址总线和控制信号,其中A端通过顶层模块映射后与DSP相连,B端通过顶层模块映射后与FPGA相连。

图3 子模块接口图Fig.3 Sub-module interface diagram

2.2 存储设计

为了保证上下行传输过程中数据读写速度最快,数据存储子模块内部不设优先级访问顺序,保证在一个时钟沿实现数据的输入和输出。为了进一步提高数据空间存储的可靠性,设计了上下行传输分段存储防差错机制,单侧读取和写入数据时访问的空间为独立的存储地址,实现代码如下:

reg[15∶0]Down_RAM[127∶0];

reg[15∶0]Up_RAM[63∶0];

//下行数据传输:

always@(posedge Clock) begin

if(A_Port_RD&&A_Port_EN) begin

A_Port_Data_Out<=Down_RAM[A_Port_Addr[6∶0]];

//A Port Reading

end

end

if(B_Port_WE) begin

Down_RAM[B_Port_Addr[6∶0]]<=B_Port_Data_In;

//B Port Writing

end

end

//上行数据传输:

always@(posedge Clock) begin

if(A_Port_WE&&A_Port_EN) begin

Up_RAM[A_Port_Addr[5∶0]]<=A_Port_Data_In;

//A Port Writing

end

if(B_Port_RD) begin

B_Port_Data_Out<=Up_RAM[B_Port_Addr[5∶0]];

//B Port Reading

end

end

由上可以看出,双口RAM存储设计未对双口RAM数据共享空间进行初始化,需要在顶层模块设计初始化功能,将双口RAM存储空间初始化为0。

2.3 同步分时防冲突设计

伺服系统通常以固定周期进行反馈数据采样和给定指令的读取、执行控制算法并进行输出,因此,本系统中双口RAM数据需要在此周期内完成传输,且尽量减少数据传输占用CPU的处理时间。在本伺服系统中,控制周期为50μs,其中将双口RAM数据传输的过程划分为6个事件进行设计,如表3所示。

表3 双口RAM数据传输事件

得益于FPGA的硬件可编程逻辑特性,双口RAM的B端口访问按照固定逻辑时序进行,6个事件分布在控制周期的固定时刻,在定时周期开始的零时刻,DSP输出一个下降沿作为同步信号给到FPGA,FPGA将当前时刻作为零时刻。双方按照表3中的时刻对双口RAM进行访问。在零时刻DSP启动事件①任务,事件①任务完成后执行事件②任务,由于DSP处理的任务为顺序执行,因此A端口不会产生读写冲突,且设计任务用时少于20μs。在25μs时刻开始,FPGA启动后续任务③④⑤⑥,采用顺序结构保证B端口读写任务不会产生读写冲突,且设计任务用时少于20μs。

在保证时序余量的前提下将任务按时间段进行了分割,双口RAM的A端口和B端口读写被分布到定时周期的上、下2个半区,避免了在同一时刻对双口RAM的同一地址空间进行读写。

3 功能仿真与测试

FPGA内部双口RAM采用VerilogHDL完成设计编码,在ISE下设计了仿真激励文件,使用ModelSim进行了功能仿真,仿真时序如图4和图5所示。

图4 双口RAM A端口读写时序逻辑Fig.4 A-port sequential logic in dual port RAM

图5 双口RAM B端口读写时序逻辑Fig.5 B-port sequential logic in dual port RAM

由图4可以看出,双口RAM A端口数据读写最快不超过4μs;由图5可以看出,双口RAM B端口数据读写时间总占用不超过15μs。由于B端口数据写入是由FPGA内部多个功能模块完成,在进行总线切换时会增加数据读写时间,因此比A端口访问时间更长。

为了验证双口RAM在数据传输中的可靠性,采用1553B总线进行了测试。使用PC机作为BC端,伺服系统为RT端,设计测试用例如下:

1)BC发送指令消息至RT;

2)FPGA将此消息解析为控制指令并写入双口RAM B端;

3)DSP从双口RAM A端读取控制指令并将其第3个数据逐地址加1,形成遥测数据写入双口RAM A端;

4)FPGA将遥测数据传输至BC;

5)改变指令消息数据,重复步骤1)~5)。

图6 测试过程与数据Fig.6 Test procedures and data

测试过程与数据如图6所示,经过上百万次测试和数据对比分析,结果显示双口RAM数据传输误码率为0,上下行数据传输稳定可靠。

4 结论

本文针对双口RAM数据传输防差错问题,设计了一种同步分时访问机制。仿真分析与实验结果表明:

1)同步分时机制在小数据量传输过程中运行稳定且具有更快的访问速度,占用更少的CPU资源和利用率;

2)本文所提的同步分时机制适用于双口RAM两侧CPU具有硬件同步机制的实时系统中,且需要CPU运行时序稳定可靠;

3)本文中FPGA访问双口RAM时仍可设计分时机制,增加总线切换开关,减少总线占用时间。