基于Xilinx V5的DDR2数据解析功能实现

唐岚

(北方工业大学 北京100144)

迅速而准确地监测雷达信号的方法对雷达的系统模拟[1]以及信号处理来说具有非常重要的意义。随着雷达的广泛应用,其性能也在快速提高,对发送信号控制的要求也越来越严格。雷达是利用无线电技术进行侦察和测距的设备。它可以发现目标,并可决定其存在的距离及方向。雷达将无线电波送出,然后经远距离目标物的反射,而将此能量送回雷达的记发机。记发机与目标物间的距离,可由无线电波传雷达的目标物,再由目标物回到雷达所需的时间计算出。精确地计算出雷达-目标物-雷达之间的无线电波传输时间就成为最为关键的步骤。本文就旨在通过脉冲波形来控制发射信号[2],每来一个脉冲发送一次雷达信号,同时在雷达信号的发射过程中,对信号连续发射的时间进行精准的控制;发射时间也不是固定不变,可根据具体情况进行更改,此时对数据文件在FPGA中通过DDR做必要的处理已成为一种通行的方法。

1 系统模型

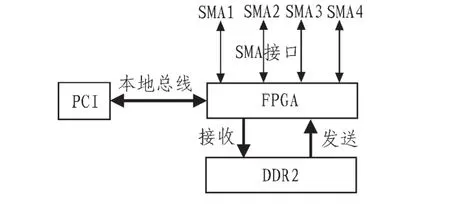

文中所设计的系统是在已有电路板卡 (包括PCI桥芯片,FPGA芯片,DDR芯片组等)的基础上,根据指定的数据文件发送出脉冲波形,其结构框架如图1所示。

图1 系统总体结构图Fig.1 Structure diagram of the power control unit tessst syste

本系统FPGA芯片采用的是Xilinx V5系列下的一款芯片。该芯片除了具有最先进的高性能逻辑架构外,还包含多种硬?IP?系统级模块,包括强大的36 Kb Block RAM/FIFO、第二代25×18DSP Slice、带有内置数控阻抗的SelectIO技术、ChipSync源同步接口模块、系统监视器功能、带有集成DCM(数字时钟管理器)和锁相环(PLL)时钟发生器的增强型时钟管理模块、SPI和并行FLASH接口以及高级配置选项。符合PCIExpress基础规范 (PCIExpress Base Specification)1.1,每模块支持 1倍、2倍、4倍或 8倍通道宽度。

系统PCI管理芯片具有32位、66 MHz的PCI总线和局部总线,突发传输速率能达到264 MB/s,本地总线支持复用/非复用的32位地址/数据。有6种可编程FIFO,以实现零等待突发传输和异步操作。支持主模式、从模式、DMA传输方式。含有1个PCI仲裁器,2个独立的DMA通道,对3.3 V和5 V的I/O信号电平容错。PCI桥芯片主要实现系统与PCI总线的连接,主机可以通过PCI总线实现对板上所有资源的访问。本系统的PCI桥芯片作为PCI总线主设备,以DMA方式与主机内存交换数据[3]。

DDR2[4]采用了在时钟的上升/下降延同时进行数据传输的基本方式,DDR2内存拥有两倍于DDR内存预读取能力(即:4bit数据读预取)。DDR2内存每个时钟能够以4倍外部总线的速度读/写数据,并且能够以内部控制总线4倍的速度运行。本系统采用了两组DDR2芯片,最大可容纳256 M的数据容量。

SMA接口有两种形式,标准的SMA是一端 “外螺纹+孔”,另一端“内螺纹+针”;反极性 RP-SMA是一端“外螺纹+针”,另一端为“内螺纹+孔”。本系统采用的标准形式,SMA接口具有双向双向传输数据的功能,即既可以接受数据也可以发送数据。

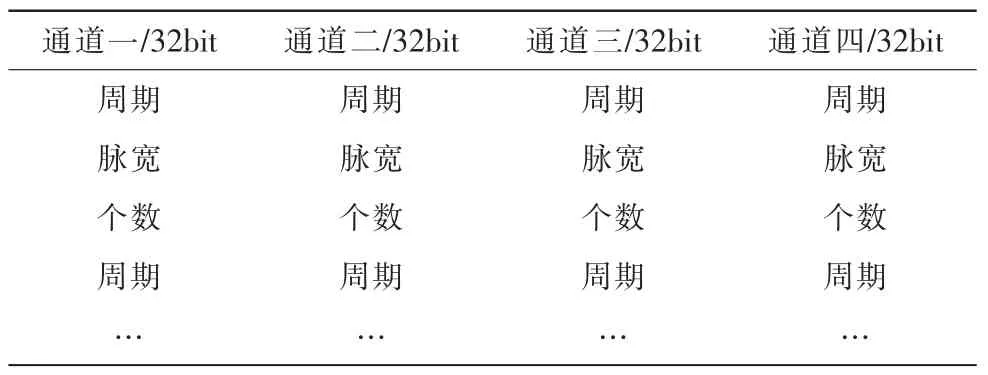

在该系统中,需要应用Matlab生成所需要的数据文件(.bin),其数据文件内容格式具体要求为:包含4个通道,每个通道的数据位宽为32位,含有脉冲周期、脉冲宽度、脉冲个数等信息,并且文件中的数据可改动,如表1所示。将数据文件经由上位机通过PCI桥芯片发送至FPGA,FPGA接收该数据并将其缓存在FIFO中,然后转存至DDR2中并进行地址解析,将DDR2接收到的数据做处理使其产生脉冲波形,此时如果收到一个发送脉冲波形的命令时,DDR2就将产生的脉冲波形发送出去,并通过SMA接口与用户端相连接,同时要求各个通道的脉冲波形相互独立,互不影响。

表1 数据文件格式Tab.1 The form of data file

2 系统程序控制设计

本系统采用板卡上自带的50 MHz晶振时钟[5],通过PLL将其倍频至100 MHz而作为生成脉冲波形的工作时钟。为在Chipscope上抓图观测方便,可将据文件(.bin)的前3个通道的参数改小,图2为数据文件的部分截图,其中0-3竖列共32bit为第一通道的参数,4-7竖列为第二通道的参数,8-b竖列为第三个通道的参数,c-f竖列为第四个通道的参数。地址0h为第一、二、三、四通道的脉冲周期,地址1h为第一、二、三、四通道的脉冲宽度,地址2h为第一、二、三、四通道的脉冲个数,地址3h再为第一、二、三、四通道的脉冲周期...如此循环依次为脉冲周期、脉冲宽度和脉冲个数。

图2 数据文件Fig.2 Data file

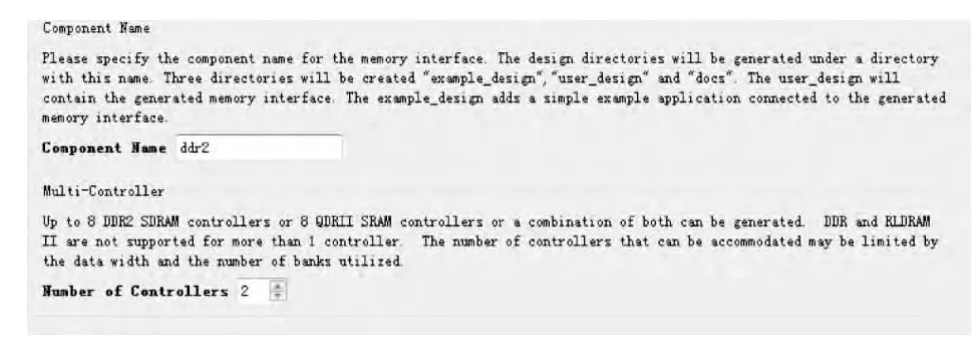

将图2所示的数据文件通过PCI桥芯片下发至FPGA,提供给底层模块使用。同时定义FPGA的复位寄存器和DDR2的工作寄存器,实现软件复位,完成DDR2的读写控制设置。两组DDR2控制子模块是调用的Xilinx的MIG IP核。配置如图3,由于含有两组DDR2,所以其中的Number of Controllers应选择2。

图3 Xilinx的MIG IP核Fig.3 MIG IP cell of Xilinx

在完成DDR2的管脚定义后,需要参考DDR2的工作控制参考资料以实现DDR2的用户定义,完成相关部分的程序代码设计,其中app_af_cmd=3'h0时,DDR实现写的指令,app_af_cmd=3'h1时,DDR2实现读的指令。DDR2用到的时钟是固定的200M时钟,此时同样需要用到晶振50 MHz时钟通过PLL倍频至200 MHz,以实现传输数据的有序控制,而不会产生时序上的混乱。

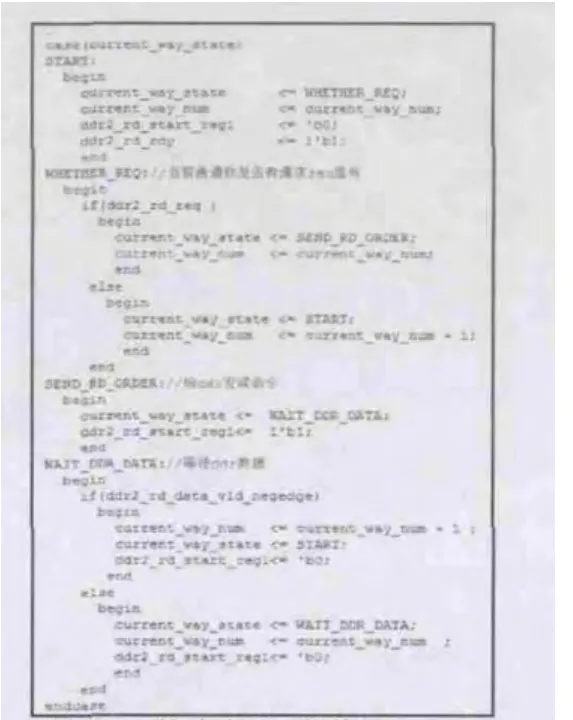

为了能够实现4个通道数据传输的互不干扰,可以在程序代码设计中使用状态机进行控制,部分程序代码如图4所示,相对应的数据传输操作状态转移如图5所示。同时只有正确接收到3个数据(脉冲周期、脉冲宽度、脉冲个数)时,脉冲才能正常的传输,所以需要用到两个寄存器,第1个寄存器作为缓冲器用来接收数据,当缓冲器接收完3个数据时,将其3个数据同时发送至第2个寄存器,以控制输出的脉冲波形。每接收到一个数据对其地址加1,以反过来读取下一个地址的数据。

3 系统验证结果与分析

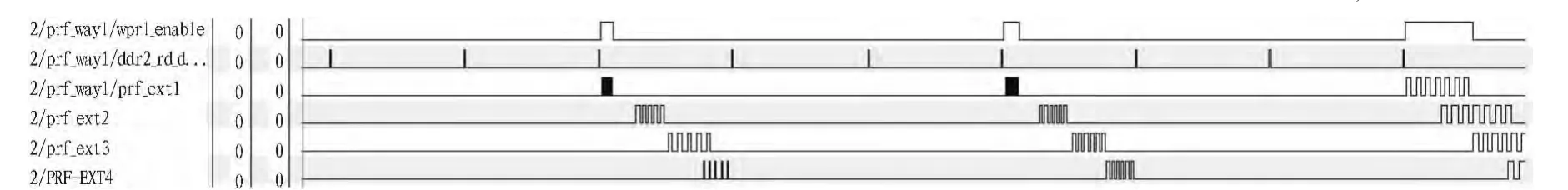

在系统验证的过程中,一旦系统接收到发送脉冲波形的命令后,就将数据文件解析成的脉冲波形通过DDR2发送,运用Xilinx自带的Chipscope对发送出的脉冲波形进行监测[6],结果如图6所示。

图4 状态机程序代码Fig.4 The code of statemachine

图5 数据传输操作状态转移图Fig.5 Data transport state

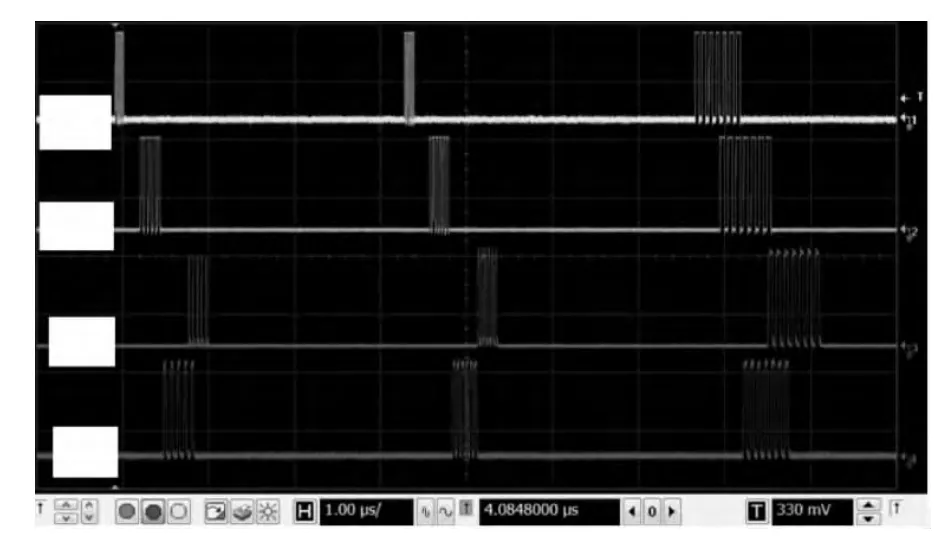

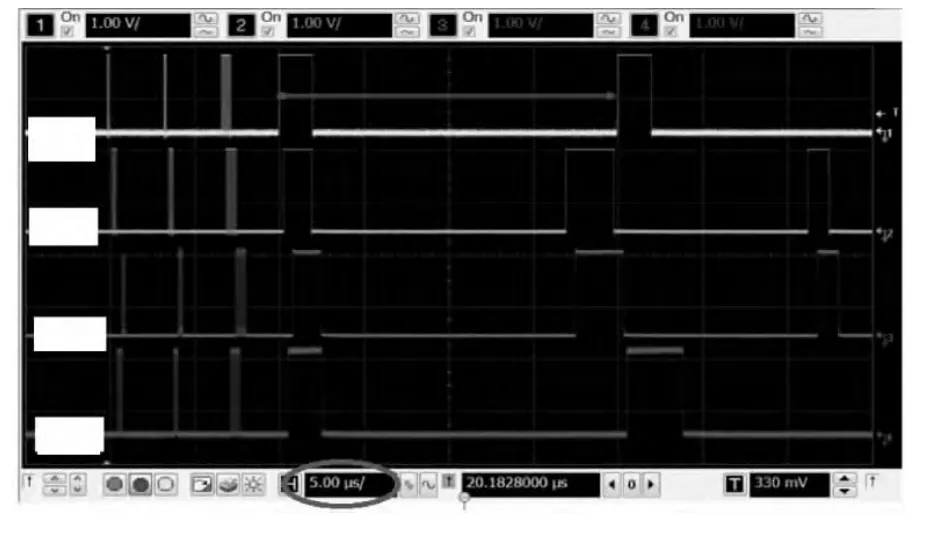

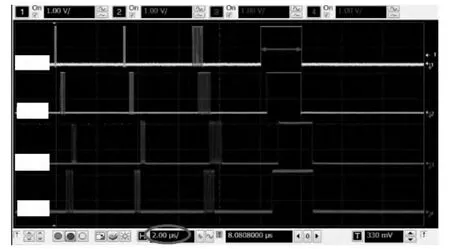

从图6中可以看出4个通道的前3个脉冲个数分别为5,6,7,和图2参数文件中数据的一致。通过SMA接口将波形连接到示波器上进行观测,示波器上对应的1,2,3,4分别为第一、二、三、四通道的波形图,观测到的波形如图7所示,和Chipscope上抓取的数据保持一致。为了进一步的验证结果的正确性与否,我们以通道一为例,对其进行解释,通过示波器引出波形,进一步验证脉冲波形的周期和脉宽。以参数文件的00000090h:07D0h=2000d为例计算周期,2 000/100 M=20μs.如图8所示。以000000A0h:C8h=200d为例计算脉宽,200/100M=2μs。如图9所示。

图6 脉冲波形监测图Fig.6 Pulsewavesmonitor

图7 示波器上观测的脉冲波形结果Fig.7 Rsultwaves in oscilloscope

图8 周期为20μsFig.8 Cyclewith 20μs

观测图形可看出通道1的周期为图中箭头部分的距离,为 5 μs×4=20 μs,结果正确。

图9 脉宽为2μsFig.9 Pulse width with 2μs

观测图形可看出通道1的脉宽为图中箭头部分的距离,为 2μs,结果正确。

4 结论

文中设计并完成了一种基于Xilinx V5的DDR2的数据解析功能的实现,了解了CPCI总线与FPGA之间的通信协议过程,同时根据外部数据文件实现了对输出的脉冲波形进行控制,检测到的信号波形也准确无误,有效的控制了发射时间,在雷达应用领域中具有一定的参考价值。

[1]张麟兮,许家栋,李萍,等.雷达接收系统仿真[J].计算机仿真,2007,24(5):298-301.ZHANG Lin-xi,XU Jia-dong,LIPing,et al.Radar receiver system simulation[J].Computer simulation,2007,24(5):298-301.

[2]李正周,郑徽,雷晓龙,等.基于DSP的脉冲雷达基带信号发生器设计[J].通信工程,2011,31(4):240-242.LI Zheng-zhou,ZHENG Hui,LEI Xiao-long,et al.DSP-based pulse radar baseband signal generator design[J].Communications Engineering,2011,31(4):240-242.

[3]刘嘉元,干汉成,白雪,等.SRA目标回波基带信号产生模块设计[J].电子技术,2008,30(1):90-92.LIU Jia-yuan,GAN Han-cheng,BAIXue,et al.SRA goal back waves baseband signal generation module design[J].Electronic Technology,2008,30(1):90-92.

[4]任丽香,龙 腾.一种通用雷达信号模拟器的设计与实现[J].现代雷达,1998,20(6):52-58.REN Li-xiang,LONG Teng.A common radar signal simulator design and implementation [J].Modern radar,1998,20(6):52-58.

[5]Howard Johnson, Martin Graham.高速数字设计[M].北京:电子工业出版社,2005.

[6]卢剑奇.雷达回波信号建模与仿真研究[D].河南:中国人民解放军信息工程大学,2006.