基于AMBA总线的IIC协议IP核设计与验证

王建雄,肖 明,余 龙

(1.江苏科技大学计算机学院,镇江212003;2.东莞市泰斗微电子有限公司,东莞523808)

基于AMBA总线的IIC协议IP核设计与验证

王建雄1,肖 明2,余 龙1

(1.江苏科技大学计算机学院,镇江212003;2.东莞市泰斗微电子有限公司,东莞523808)

介绍了一种基于AMBA总线verilog HDL实现的IIC主机模式的IP核设计。该模块能够在标准和快速模式下运行,能够灵活配置为十位地址寻址或七位地址寻址模式。详细说明了该IP核的架构,各部分设计及状态转换过程。最后该模块通过了系统验证,并在xilinx FPGA上转化为硬件电路实现了所有功能。

AMBA总线;Verilog HDL语言;IIC协议;IP核

1 引 言

现如今,电子类产品向着小型化、智能化、低功耗、低成本、高可靠性的方向发展。IIC仅有两根线就实现了器件之间的双工通信,它有着接口简单、可扩展性好、功耗低等特点,已经被广泛应用于各类数字系统中。而片上系统(System on Chip,SoC)已逐渐成为超大规模集成电路的发展趋势,由于系统与外部电路的通信是通过外围接口实现的,因此设计一个稳定可靠的外围通信接口的IP就变得非常重要。正是在此形势下设计了基于AMBA总线的IIC协议IP核,并通过系统仿真和FPGA上以硬件方式实现和验证了设计的正确性和可靠性。

2 IIC协议简介

IIC(Inter IC)总线是Philips公司于1992年推出的用于芯片间连接的双向串口总线协议。它已经被广泛应用于视/音频领域、IC卡行业、家用电器、通讯设备及各类电子产品中,在智能仪器、仪表和工业测控领域也得到了广泛应用。

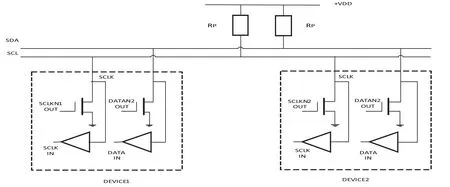

其电气连接如图1所示。

该协议使用一根数据线SDA和一根时钟线SCL进行通信。时钟由主机产生从机接收,主机在SCL低电平时发送数据到SDA上,从机在SCL为高电平时采样SDA。在时钟信号为高电平期间,数据线上的数据必须保持稳定,只有在时钟线上的信号为低电平期间,数据线上信号才允许变化。

SDA上的数据格式分为起始条件、结束条件、重复起始条件、响应位和数据位。总线上每一个从器件都有一个唯一的标识地址。主机以一个起始条件加上从机地址寻址相应从机。当一次寻址失败时,主机可以发送重复起始条件后继续发送目标地址寻址从机。从机接收到自己的地址或者接收完一个字节的数据时必须将SDA拉低以给主机一个应答信号。主机接收完一个字节的从机数据时也必须给出应答信号。当传输完成时,由主机发送结束条件完成本次传输。一次完整的传输,其SDA和SCL上的电平如图2所示。

图1 SCL和SDA的电气连接方式图

图2 一次完整的传输过程

在一次传输中,主机可以选择七位或者十位寻址模式进行寻址,也可以选择重复起始条件重新开始一次传输。当从机或主机处于忙状态时可以选择将SDA信号线拉低使IIC主机或从机处于等待状态。

3 IIC协议IP核设计

该IP核实现了IIC协议的主机功能,可以灵活配置为标准和快速模式,支持7位和10位寻址模式,支持主、从机等待功能和重复起始条件寻址模式。

3.1 系统结构图

系统结构如图3所示。由图3可以看出,其结构可以分为控制部分和数据通道部分及时钟部分。控制部分分为控制单位、仲裁单元、中断寄存器和控制寄存器,由于控制寄存器仅仅起到存储控制命令的作用,故在此将其划分为控制部分。数据通道部分分为FIFO、地址寄存器、移位寄存器、状态寄存器。时钟部分分为时钟单元和波特率寄存器。

3.2 各部分设计

3.2.1 控制部分设计

控制部分主要通过判断控制寄存器、状态寄存器的值和仲裁单元的状态完成对数据通道部分的控制。控制部分的核心实现为状态机,通过判断各个条件实现状态机的跳转,从而产生相应控制信号控制数据通道部分中数据流的流动。控制部分控制地址寄存器中地址的装载,移位寄存器中数据的移出,状态寄存器的读取和FIFO的读写控制。

图3 系统结构图

3.2.2 数据通道部分设计

数据通道部分主要实现数据的暂存和转换。其中FIFO实现数据缓存,它能协调高速APB协议和低速IIC协议之间的通信。移位寄存器能实现数据的串并转换。地址寄存器能实现地址的存储和发送。状态寄存器主要存储IIC工作时的各状态,用于控制部分状态机的跳转和传送给CPU调试使用。

3.2.3 时钟部分设计

时钟模块工作时,首先需要配置波特率寄存器。通过波特率寄存器中的值计算出SCL分频出的时钟频率,其计算公式如下,DIV值由波特率寄存器中的值确定。

时钟单元产生SCL时钟并且采样SCL线上信号。当SCL时钟线被从机拉低时主机需要启动等待功能。

3.3 IP核的状态机设计

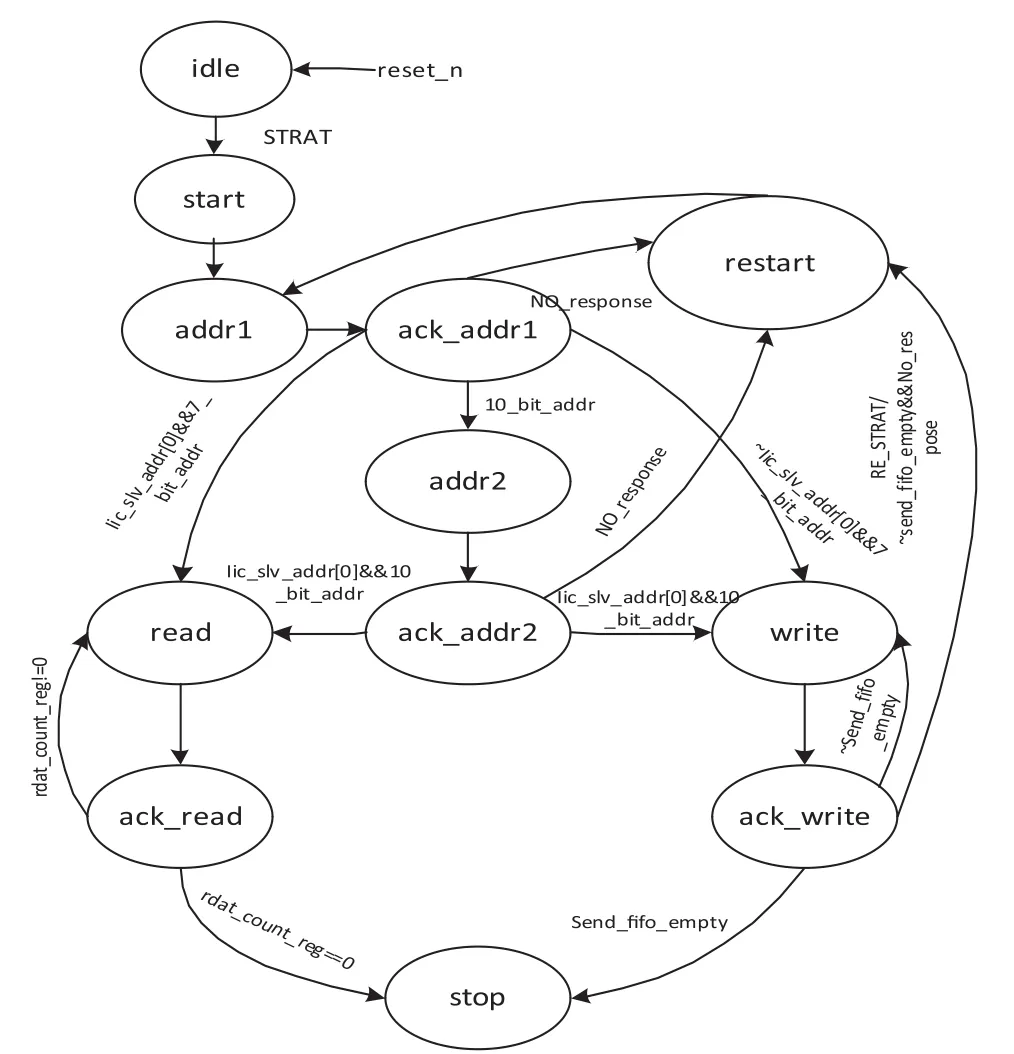

该IP核的逻辑状态转换如图4所示,各个状态的详细说明如下。

图4 逻辑状态转换图

Idle状态:当IIC没有得到运行指令或程序被复位时,程序就处于idle状态。在这个状态时SDA和SCL对外输出高电平。

start状态:当控制寄存器的START位被置位时,程序由idle状态跳转到start状态。程序位于该状态时SCL输出高电平,同时SDA产生一个由高到低的跳转。

addr1状态:在该状态时会将地址寄存器中的七位地址或者十位地址的高位地址发送给从机,并且采样SDA信号线判断主机是否丢失仲裁。当地址均发送完并且没有丢失仲裁时程序跳转到ack_addr1状态中。

ack_addr1状态:程序在该状态时会检查是否有从机应答信号。如果SDA被拉低则表明从机接收地址正确。若从机地址为7位,则程序根据最低的位进行相应跳转;若从机地址为10位,则程序跳转到addr2状态。如果SDA未被拉低,表明从机接收第一个字节有误,程序跳到restart状态。

addr2状态:当从机地址是10位地址时,程序把10位地址的低八位发送出去并自动跳转到ack_addr2状态。

ack_addr2状态:程序检查SDA是否被拉低,若被拉低则根据跳转,否则程序跳回restart状态。

restart状态:当控制寄存器的RESTRART位被置位或者发送FIFO非空而从机无应答或者程序处于ack_addr无应答时,程序都会跳转到该状态。程序处于此状态时会向从机发送一个重复起始条件并自动跳转到addr1状态。

read状态:主机在每个SCL的上升沿采样SDA,并将采样值存在移位寄存器中,当完成一个byte的接收时将移位寄存器中的值存入FIFO,并且程序跳到ack_read状态。

ack_read状态:当完成一个byte的接收并且主机还要继续接收数据时,主机需要发送一个响应给从机并且跳入read状态,否则程序跳转到stop状态。

write状态:主机将FIFO中的数据以byte为单位发给从机,发送完后自动跳转到ack_write状态。

ack_write状态:当FIFO非空,并且检测到从机的应答时程序跳回write状态,当FIFO为空时程序跳转到stop状态。

stop状态:SCL为低电平并且SDA从低电平翻转到高电平,完成一个结束状态的传输。

4 IP验证

4.1 验证平台介绍

验证该模块,需要搭建一个testbench平台,该平台由激励模块、APB主机模型、DUT、输出响应模型、监视器、比较器等组成,各模块介绍如下。

激励模块:激励模块的主要功能是提供给测试平台各种case以使IP运行于不同的状态。在验证该模块中使用的测试用例如表1所示。

表1 验证测试用例表

APB主机模型:APB主机模型主要模拟APB的总线时序,使激励数据能按APB的协议要求传输给被测设计。

DUT(Design Under Test):即被测的IP设计。

输出响应模型:其主要功能是对被测设计输出的数据按照协议做出应答,在该设计中选择的输出响应模型有IIC从机模型和EEPROM。

监视器:监视器监视输入和输出协议中的位传输,以及起始、结束、复位等条件的正确性。如果检测到数据与期望数据不一致,那么测试平台就给出错误报告信息。

比较器:比较器的主要功能是检测输入和输出各数据,并比较其是否正确。如果发送数据和测试数据不正确,那么测试平台将生成测试错误报告。

4.2 测试用例介绍

以上测试用例主要测试了该IP模块在正常和异常情况下对发送的命令是否能做出正确响应和处理。在使用测试用例对DUT进行测试的时候要根据设计的功能点全面考虑需要测试的功能,并加入一些极端情况下的测试激励。

4.3 验证结果

当验证完成后,该设计在synopsis公司的VCS上进行覆盖率统计。其覆盖率统计如图5所示。

图5 IP的验证统计覆盖率

上图中各覆盖率没有达到100%的原因分析如下:

(1)由于case语句中各条件已完备,导致default分支不能被覆盖到,所以行覆盖率没有达到100%。

(2)由于设计中增加的一些保护性代码,在一般验证中难以满足该情景,故导致条件覆盖率不能到达100%。

(3)由于该设计中某些位的值按功能不会变化,故翻转覆盖率不能实现100%的覆盖。

(4)FIFO模块的读写使能不能同时有效。

5 仿真与实现

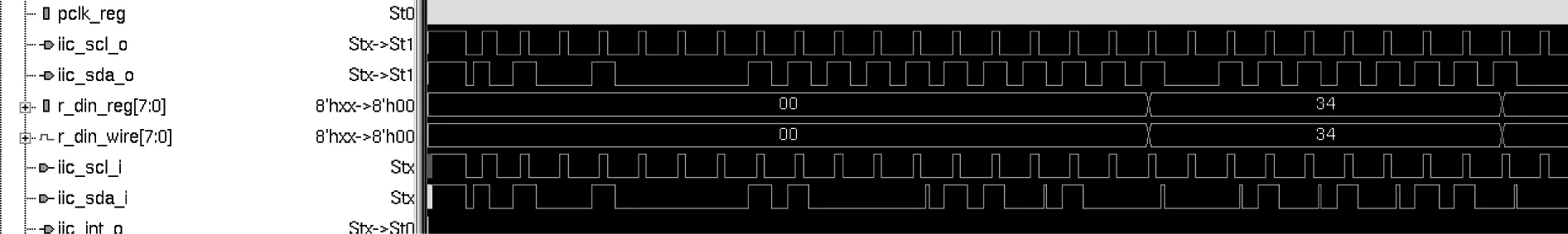

该设计通过测试平台的验证后并在VCS上进行了仿真,其仿真结果完全满足预期设计,如图6所示。

图6 IIC仿真波形图

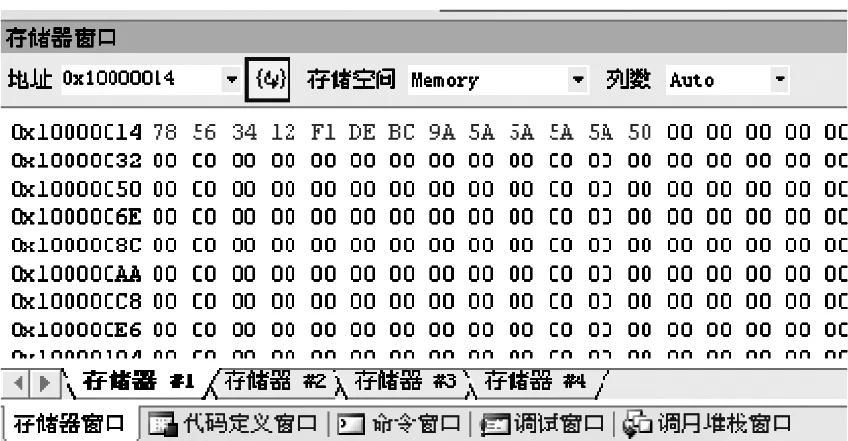

然后该设计在XILINX公司的ISE软件上进行了编译、映射和综合生成最终的bit文件下载到FPGA板上。下载好了的FPGA与单片机模拟的IIC从机进行通信,FPGA写单片机数据12345678 9ABCDEF1 5A5A5A5A 00000005,其结果如图7所示。单片机接收FPGA的数据,用示波器观察其波形如图8所示。

6 结束语

基于IP的SOC模块化设计能让产品以更快的速度推向市场,而且一个精心设计并经过多次验证过的IP其可靠性和资源利用率都会很高。该设计采用可重用的Verilog HDL代码编码风格,并最终通过Xilinx FPGA验证。经验证其性能完全满足预期要求,其实现不依赖具体的FPGA和AISC工艺。

图7 IIC从机接收到数据图

图8 示波器观察波形图

[1]wayne wolf著,现代VLSI设计:基于IP核的设计(第4版)[M].李东生等译,北京:电子工业出版社,2011-07.

[2]ciletti,M.D著.Verilog HDL高级数字设计[M].张雅倚等译,北京:电子工业出版社,2005-01.

[3]ARM Limited.AMBA Specification Rev2.0[S].1999.05.

[4]Philips semiconductors.THE I2C-BUSSPECIFICATION VERSION 2.1[S].2000.01.

[5]俞伟,徐宁仪,罗飞,等.IIC总线控制器IP核设计[J].世界科技研究与发展,2005(1):18-21.

[6]王前,屋淑泉,刘喜英.基于FPGA的IIC总线接口实现方法[J].微电子技术,2002(2):22-24.

[7]田耘,徐文波,著.Xilinx FPGA开发实用教程[M].北京:清华大学出版社,2008-11.

Design and Verification of IP Core of IIC Protocol Based on AMBA Bus

WANG Jian-xiong1,XIAO Ming2,YU Long1

(1.School of Computer Science,Jiangsu University of Science and Technology,Zhenjiang 212003,China;2.Techtotop Micro-electronics Company of Dongguan City,Dongguan 523808,China)

This article describes an IP core design of IIC master,base on AMBA bus,which implements by verilog HDL.The module can runs in standard mode and quick mode,and it can be flexibly configured to be ten bit or seven bit addressing mode.This article describes the structure of IP core,and its design and status conversion process.Finally,the module has passed the system-level verification and all functions have been implemented in Xilinx FPGA hardware.

AMBA Bus;Verilog HDL;IIC protocol;IP core

10.3969/j.issn.1002-2279.2014.01.002

TN492

:B

:1002-2279(2014)01-0004-05

王建雄(1988-),男,四川巴中人,硕士研究生,主研方向:数字集成电路设计。

2013-09-30