DOE技术在低电压CMOS晶体管中的质量控制*

张 霞,袁陈晨,郑 祺,徐士美,童庆强

(1.上海工程技术大学材料工程学院,上海 201620;2.上海贝岭股份有限公司,上海 200233;3.上海华力微电子有限公司,上海 201203)

DOE技术在低电压CMOS晶体管中的质量控制*

张 霞1*,袁陈晨1,郑 祺1,徐士美2,童庆强3

(1.上海工程技术大学材料工程学院,上海 201620;2.上海贝岭股份有限公司,上海 200233;3.上海华力微电子有限公司,上海 201203)

CMOS晶体管;阈值电压;DOE;注入剂量

互补型金属-氧化物-半导体晶体管CMOS(Complementary Metal-Oxide-Semiconductor)的生产是一个复杂精细的工艺过程,包含SiO2薄膜的淀积及光刻、刻蚀、注入等各种工序的互相协作。因复杂而精细的工艺,和多环节决定因素,靠传统的工艺台帐和工艺试验的形式来实现电学参数阈值电压Vt的调控非常困难[1-2]。改变阈值电压Vt的工艺参数有多种多样,比如内在的氧化层电荷、功函数差、沟道里的载流子剂量[3],外在的衬底偏压、平带电压等等[4]。

在教科书[4]中,我们可以看到MOS晶体管的阈值电压Vt的经典公式为:

其中,Vt是阈值电压,VFB是平带电压,ΨB是衬底的费米能级,q是电荷量,εs是总的介电常数,NA是掺杂浓度,VBS是反向衬底-源极电压,Co是氧化层的电容常数。依据物理学家推导的经典公式,公式左边Vt是MOS晶体管的性能体现,公式右边NA是由实际工艺决定,其他所有参数由材料特性来决定。因此,沟道里的注入载流子剂量NA尤为重要,通过芯片制造中的注入载流子剂量NA、进行有效调控低阈值电压Vt更吸引人们探索研究。

本文采用DOE(DesignofExperiment)试验方法进行了工艺流片的分卡操作,针对工艺流程中的Vt区注入Dvt、N场注入DNF、TEMP注入DP这3种注入剂量,对低压NMOS和低压PMOS的阈值电压Vt进行调节优化,得到阈值电压(Vtn、Vtp)和各注入剂量(Dvt、DNF、DP)之间的关系。该数据结果对于阈值电压Vt的设计和工艺参数的选取具有重要指导意义。

1 实验过程

1.1 实验工艺流程

CMOS晶体管的完整工艺流程由以下部分组成,分别为:

硅片检测→光刻零层→光刻有源区(光刻有源区、刻蚀场区、N阱注入)→光刻P阱(光刻P阱、P阱注入、场氧化、3层腐蚀、预栅氧化、Vt区注入)→光刻N场(光刻N场、N场注入、腐蚀预栅氧、栅氧化1、多晶1淀积、多晶1掺杂)→光刻TEMP→注入TEMP及去胶→光刻多晶一→光刻PLDD→光刻N+区→光刻P+区→光刻接触孔→光刻金属1→光刻VIA1→光刻金属2→光刻钝化层。

本论文中CMOS的主要工艺调节步骤为Vt区注入、N场注入、注入TEMP这3步注入过程,分别隶属于光刻P阱、光刻N场、和光刻TEMP。以上3步的注入离子分别为BF2、B、BF2,对应的离子束能量分别60keV、70keV和60keV。调节离子束的注入剂量(单位:ion/cm2),可控制离子束的掺杂浓度,是优化MOS管阈值电压Vt的重要工艺。

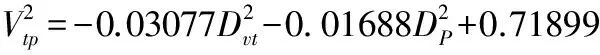

1.2 DOE正交分卡

根据CMOS的工作原理和工艺经验,影响阈值电压Vtn和Vtp的3个因子分别为:Vt区注入、N场注入、注入TEMP的注入剂量。在CMOS阈值电压设计时,人们往往希望通过一个注入剂量的改变,就能同时达到低压NMOS和PMOS,但是注入剂量对于Vtn和Vtp的影响趋势截然不同,甚至可能是相逆的。为了考查Vt区注入、N场注入、注入TEMP这3个注入剂量对于Vtn和Vtp的各自影响或者逆向作用,本文采用了正交分卡DOE方法,具体的工艺参数和相对应的注入剂量如表1所示。

表1 CMOS管的DOE正交分卡及注入剂量参数

本文中,CMOS晶体管的栅氧层厚度为100nm左右,衬底浓度为1×1010个/cm2,阱浓度为1×1010个/cm2,在未改变注入参数时的常规情况下NMOS的开启电压Vtn为0.77 V,PMOS的开启电压Vtp为0.93 V。在表中,1号样品代表进行Vt区注入剂量Dvt=2.8×1012ion/cm2,N场注入剂量DNF=2.5×1012ion/cm2,注入TEMP的注入剂量DP=0,其余2至18号样品依次类推。

1.3 CMOS管阈值电压Vtn和Vtp测试

样品经过3次注入以及最后的光刻钝化层后,即可进行工艺控制监控PCM(Process Control Monitor)测试,PCM的常见参数有开启电压、击穿电压、导通电流、单管漏电流、方块电阻、接触电阻、条形电阻、电容及电容击穿等等。

本次重点考察的是低压NMOS和低压PMOS管的阈值电压,具体测试方法为:在漏上加0.1 V固定电压(P管时加-0.1 V),源和衬底接地。在栅上扫描电压,N管时扫描正电压0~3 V,P管时扫描负电压-3 V~0。扫描栅上电压时,由最大跨导法得到阈值电压Vtn和Vtp。试验过程中,其中有4个样品发生碎片。其余样品经过测试,Vtn和Vtp都在1V以下,符合低压CMOS的使用需求,具体测试值如表2所示。

表2 CMOS管的注入参数,阈值电压Vtn和Vtp,以及通过公式拟合的Vtn predicted和Vtp predicted

2 数据分析与讨论

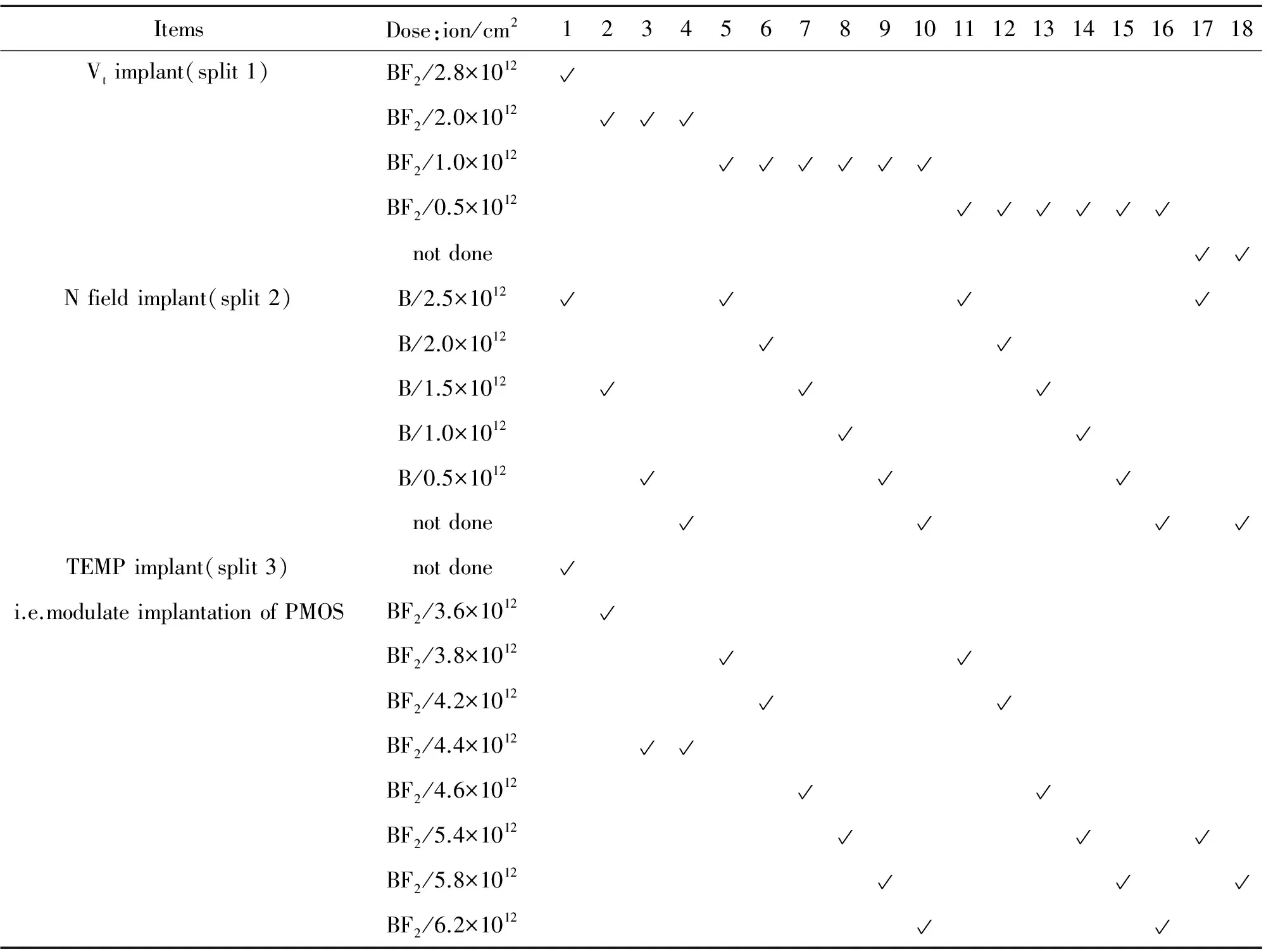

2.1 Vt区注入剂量Dvt、N场注入剂量DNF与NMOS管阈值电压Vtn

2.1.1Vt区注入剂量Dvt保持不变,N场注入剂量DNF变化时

从表2中的18个样品对比可以看出,2~4样品中,Dvt保持注入剂量为2.00×1012ion/cm2不变时,随着N场注入剂量DNF从1.5×1012ion/cm2降低到5×1011ion/cm2,并降低到0时(图1中正方形的点和线),NMOS管阈值电压Vtn由0.6 V降低到0.45 V,也就是说Dvt不变,随着N场注入剂量DNF降低,NMOS管阈值电压Vtn也降低。类似地,保持Dvt不变,5~10样品(图中圆形的点和线、Dvt=1.00×1012ion/cm2)验证了相同的规律,11~16样品(图中正三角形的点和线、Dvt=0.5×1012ion/cm2)、17~18样品(图中倒三角形的点和线、Dvt=0)也同样遵循Vtn随DNF下降而下降的规律。总之,图中的4个系列的点线显示一致的结论:如果注入剂量Dvt不变,随着N场注入剂量DNF降低,NMOS管阈值电压Vtn也降低。

图1 NMOS管阈值电压Vtn与不同N场注入剂量DNF的变化关系(当Vt区注入剂量Dvt不变时)

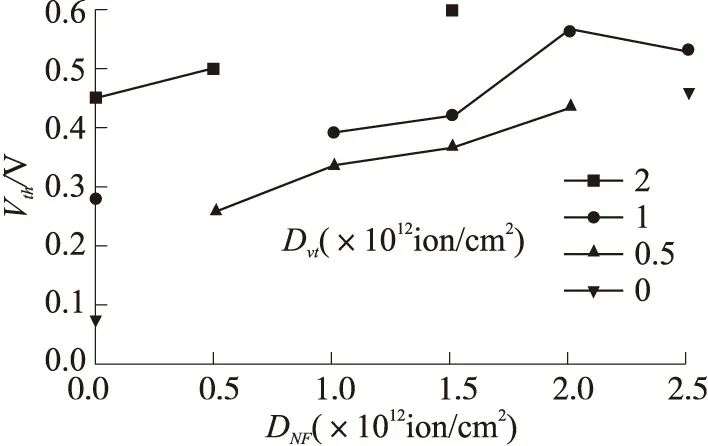

2.1.2 Vt区注入剂量Dvt变化,N场注入剂量DNF保持不变时

接下来讨论N场注入剂量DNF不变,注入剂量Dvt变化对于阈值电压Vtn的变化影响趋势。分析表2可知,样品1、5、11、17是一组N场注入剂量DNF=2.5×1012ion/cm2,样品6、12对应于DNF=2.0×1012ion/cm2,样品2、7、13对应于DNF=1.5×1012F,样品8、14对应于DNF=1.0×1012ion/cm2,样品3、9、15对应于DNF=5×1011ion/cm2,样品4、10、16、18对应于DNF=0,以上6个系列遵循Vtn随Dvt下降而下降的规律,其影响曲线如图2所示。

图2 NMOS管阈值电压Vtn与不同Vt区注入剂量Dvt的变化关系(当N场注入剂量DNF不变时)

2.1.3 Vt区注入剂量Dvt、N场注入剂量DNF与NMOS管阈值电压Vtn的关系式

综合以上两张图和相关的数表可知,NMOS管阈值电压Vtn,随着N场注入剂量DNF降低而降低,随Vt区注入剂量Dvt下降而下降。如果将Vt区注入剂量Dvt当作x坐标,将N场注入剂量DNF当作y坐标,以xy平面内的值作为z坐标,可以得到如图3所示的梯度图,关于z值随颜色的变化如图3所示。

图3 NMOS管阈值电压Vtn与Vt区注入剂量Dvt、N场注入剂量DNF的关系图(其中,x轴是Dvt,y轴是DNF,z轴代表平面上的彩色等高线图,线的梯度值代表Vtn。)

从图3中z值随x、y的变化分布图可以看出,z与x、y满足z=ax+by+c的关系式。将z、x、y都赋予物理意义后,经公式拟合后,可知NMOS管阈值电压Vtn与Vt区注入剂量Dvt、N场注入剂量DNF满足以下关系式

Vtn=0.15791Dvt+0.12320DNF+0.11433

如果将实际工艺参数Vt区注入剂量Dvt、N场注入剂量DNF代入此式中,可以得到NMOS管阈值电压Vtn的预测值Vtn predicted,也就是拟合出来的计算值Vtn拟合,如表2列举所示,表中同时有实际测试值。将Vtn与Vtn predicted数据以图表示,从图4中两条线可以看出,Vtn实际测试值与Vtn predicted比较吻合。

图4 NMOS管实际阈值电压Vtn与公式拟合出的Vtn predicted的对比图

在实际电参数测试中,NMOS管的击穿电压BVds基本维持在10.3V左右,可以保证NMOS在较好状态下工作。

2.2 Vt区注入剂量Dvt、注入TEMP的注入剂量DP与PMOS管阈值电压Vtp

2.2.1 Vt区注入剂量Dvt保持不变、注入TEMP的注入剂量DP变化时

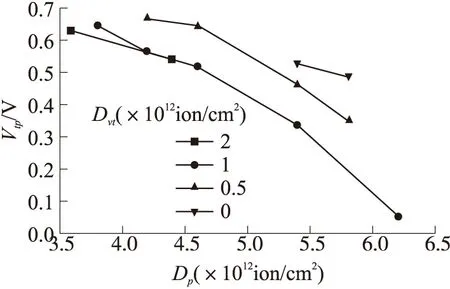

从表2中的18个样品对比可以看出,2~4样品中,Dvt保持注入剂量为2.00×1012ion/cm2不变时,随着TEMP注入剂量Dp从3.6×1012ion/cm2提高到4.4×1012ion/cm2(图5中正方形的点和线),PMOS管阈值电压Vtp由0.63V降低到0.54V,也就是说Dvt不变,随着TEMP注入剂量Dp提高,PMOS管阈值电压Vtp会降低。类似地,保持Dvt不变,5~10样品(图中圆形的点和线、Dvt=1.00×1012ion/cm2)验证了相同的规律,11~16样品(图中正三角形的点和线、Dvt=0.5×1012ion/cm2)、17~18样品(图中倒三角形的点和线、Dvt=0)也同样遵循Vtn随DP上升而下降的规律。图5中的4个系列点线显示一致的结论:如果注入剂量Dvt不变,随着TEMP注入剂量Dp增加,PMOS管阈值电压Vtp会降低,与文献报道一致[3,5]。

图5 PMOS管阈值电压Vtp与不同TEMP注入剂量Dp的变化关系(当Vt区注入剂量Dvt不变时)

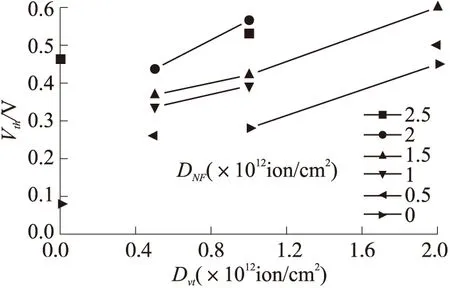

2.2.2 Vt区注入剂量Dvt变化、注入TEMP的注入剂量DP保持不变时

分析表2可知,注入TEMP的注入剂量DP从3.6×1012ion/cm2到6.2×1012ion/cm2,一共有6个系列。在每个系列中,保持TEMP的注入剂量不变,从表2中和图6的影响曲线可以清晰看出,随着Vt区注入剂量Dvt在0、0.5、1、2×1012ion/cm2这4档变化时,PMOS管的阈值电压Vtp遵循随Dvt增加而下降的规律。

图6 PMOS管阈值电压Vtp与不同Vt区注入剂量Dvt的变化关系(当TEMP注入剂量DP不变时)

2.2.3 Vt区注入剂量Dvt变化、注入TEMP的注入剂量DP与PMOS管阈值电压Vtp的关系式

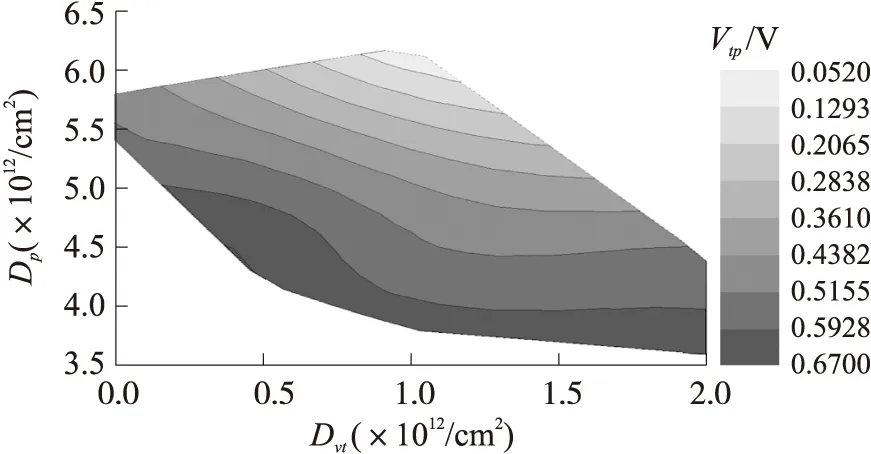

综合以上分析可知,PMOS管阈值电压Vtp,随着TEMP注入剂量DP增加而降低,随Vt区注入剂量Dvt增加而降低。同样,将Vt区注入剂量Dvt当作x坐标,将TEMP的剂量DP当作y坐标,以xy坐标第1象限的平面值作为z坐标,可以得到如图7所示的梯度图,z值的渐近变化如图右边所示。

图7 PMOS管阈值电压Vtp与Vt区注入剂量Dvt、TEMP注入剂量DP的关系图(其中,x轴是Dvt,y轴是DP,z轴代表平面上的彩色,彩色值代表Vtp。)

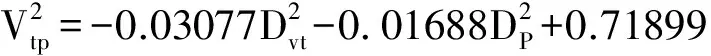

从图7中z值随x、y的变化分布图可以看出,z与x、y近似满足椭圆关系式。经Origin公式拟合后,可知PMOS管阈值电压Vtp与Vt区注入剂量Dvt、TEMP注入剂量DP满足以下关系式

如果将实际工艺参数Vt区注入剂量Dvt、注入TEMP的剂量DP代入此式中,可以得到PMOS管阈值电压Vtp的预测值Vtp predicted,也就是拟合出来的计算值Vtp拟合,如表2列举所示。将Vtp与Vtp predicted以图表示,从图8中可看出,除了10号样品因注入TEMP的剂量DP为0导致数据偏差大,其余Vtp实际测试值与Vtp predicted比较吻合。经测试得到,PMOS管的击穿电压BVds在12V左右,证明晶体管经过阈值电压的常规值0.93V调控至0.0535V~0.63V后,仍能具有较高的击穿电压值。

图8 PMOS管实际阈值电压Vtp与公式拟合出的Vtp predicted的对比图

3 结论

采用DOE试验方法对工艺流片进行分卡操作,对低压CMOS的阈值电压Vtn、Vtp进行调节优化,得到了阈值电压(Vtn、Vtp)和各注入剂量(Vt区注入、N场注入、注入TEMP)之间的关系。主要结论如下:

(1)实验样品的Vtn和Vtp都在1V以下,符合低压CMOS的使用需求。

(2)NMOS管阈值电压Vtn,随着注入剂量Dvt下降而下降,随着N场注入剂量DNF下降也降低。Vtn与Dvt、DNF满足以下关系式Vtn=0.15791Dvt+0.12320DNF+0.11433。

综上所述,将工艺参数Dvt、DNF、DP对CMOS阈值电压Vtn、Vtp的影响关系,用科学规律和公式联系起来,挖掘半导体物理经典公式中Vt的工艺影响因素,对于直接指导工艺参数Dvt、DNF、DP具有重要作用[6-8],同时工艺反馈于阈值电压Vtn和Vtp,揭示了阈值电压Vtn、Vtp的内在规律,对于CMOS的设计具有借鉴意义。

[1]王文君. 采用SPC技术控制半导体器件的工艺质量[J]. 微电子器件与技术,2010,47(8):518-521.

[2]王廷青. 封装工艺中SPC控制限计算方法的优化[J]. 电子与封装,2009,9(4):8-12.

[3]蔡俊,傅义珠. 总剂量辐射对硅双极和MOS器件性能的影响[J]. 固体电子学研究与进展,2010,30(2):559-563.

[4]施敏. 半导体器件物理与工艺[M]. 2版. 苏州:苏州大学出版社,2002:188-191.

[5]Zhang Guohe,Shao Zhibiao,Zhou Kai. Threshold Voltage Model for a Fully Depleted SOI-MOSFET with a Non-Uniform Profile[J]. Chinese Journal of Semiconductors,2007,28(6):842-847.

[6]Pandey P,Pal B B,Jit S. A New 2-D Model for the Potential Distribution and Threshold Voltage of Fully Depleted Short-Channel Si-SOI MESFETs[J]. IEEE Trans Electron Devices,2004,51(2):246-254.

[7]刁冬梅,杨银堂,朱樟明. MOS晶体管的阈值电压不匹配特性[J]. 电子科技,2007,212(5):1-4.

[8]刘新宇,孙海峰,刘洪民,等. 全耗尽CMOS/SOI工艺[J]. 半导体学报,2003,24(1):104-108.

张霞(1980-),女,汉族,籍贯湖北省,博士,讲师,2007年博士毕业于中国科学院上海硅酸盐研究所,曾就职于上海贝岭股份有限公司,2008年加入上海工程技术大学,主要研究方向半导体光电薄膜与器件,zhangxia@sues.edu.cn。

TheQualityControlofDOETechnologyinLowThresholdVoltageCMOSTransistor*

ZHANGXia1*,YUANChenchen1,ZHENGQi1,XUShimei2,TONGQingqiang3

(1.Department of Material Engineering,Shanghai University of Engineering Science,Shanghai 201620,China;2.Shanghai Belling Limited Corporation,Shanghai 200233,China;3.Shanghai Huali Microelectronics Corporation,Shanghai 201203,China)

CMOS transistor;threshold voltage;DOE;implant doses

项目来源:上海高校一流学科(培育)基金项目(YLJX12-2);国家自然科学基金青年科学基金项目(61404082)

2013-11-28修改日期:2014-01-12

TN386.1

:A

:1005-9490(2014)06-1043-06

10.3969/j.issn.1005-9490.2014.06.007