高速PCB同步开关噪声仿真抑制分析

余青旺,张赤斌*,王广平

(1.东南大学机械工程学院,南京 210096;2.中航工业航空动力控制系统研究所,江苏 无锡 214063)

高速PCB同步开关噪声仿真抑制分析

余青旺1,张赤斌1*,王广平2

(1.东南大学机械工程学院,南京 210096;2.中航工业航空动力控制系统研究所,江苏 无锡 214063)

摘要:从电源完整性(PI)的角度分析了抑制同步开关噪声(SSN)的有效途径——降低芯片供电电源的输入阻抗。使用目标阻抗法,并对给定最大去耦电容容值种类的条件下,使用频域对数法进行电源地分配网络(PDN)的优化。以XX电子控制器的PCB板为例,使用Ansoft SIwave及Ansoft Designer仿真软件,对复杂高速PCB板PDN进行优化设计,并通过时域观察优化前后SSN的抑制情况。仿真结果表明:通过优化PDN能够有效降低SSN。

关键词:电源完整性;同步开关噪声;目标阻抗;Ansoft SIwave;Ansoft Designer

电源完整性PI(Power Integrity)是指系统工作下电源波形的质量。在复杂的高速PCB中,有多个高速芯片,同步翻转的输入/输出IO口也越来越多,并会产生瞬间变化的大电流,这个电流在经过电源供电网络时由于阻抗的存在产生交流压降,并会通过电源网络干扰其他器件,即为同步开关噪声SSN(Simultaneous Switching Noise)[1]。一方面高速器件性能不断提高,工作频率越来越高,产生的谐波噪声也越来越高;另一方面功耗变大且供电电压变小,电压噪声容限变小,电源完整性也变越发突出[2]。

本文以XX电子控制器PCB板为例,运用频域目标阻抗法对PCB板3.3 V电源分配网络进行PI设计,并提出在给定电容容值种类前提下使用对数坐标法对电源分配网络PDN(Power Distribution Network)进行优化,并从时域的角度观察优化前后同步开关噪声抑效果。

1 同步开关噪声分析及解决方法

1.1SSN噪声分析

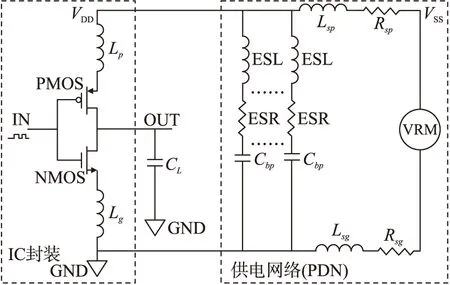

用图1的简化模型来分析CMOS电路的SSN。当输入端电平在高低切换时,PMOS/NMOS管会同时导通,产生尖峰电流,在经过封装电源引脚电感和电源平面电感时(假设等效直流电阻很小,只考虑交流感抗),其加在芯片上的电源电压下降为:

(1)

若有N个驱动器同时切换则芯片引脚产生的压降为N倍ΔV。

图1 单个IO口SSN电路模型

若产生的瞬态电流在经过封装地引脚电感和地平面电感,则会在芯片地和系统地之间直接产生地弹噪声Vgb:

Vgb=[Lg(di/dt)+Lsg(di/dt)]

(2)

通过理论分析知SSN会直接导致供电电压下降及静态线噪声[3]。如果SSN产生的压降超过了电压容限,就会产生电源完整性问题,还会通过PDN干扰其他器件,并可能引发电磁辐射干扰EMI(Electro-magnetic Interference)问题,并导致产品不能通过国家电磁兼容EMC(Electro Magnetic Compatibility)测试标准。从SSN产生原因和传播路径知减小SSN的主要途径有:改善信号的质量,即信号完整性SI(Signal Integrity);减小芯片封装寄生电感;降低PDN输入阻抗。从电源完整性的角度来解决工程上遇到的SSN过大的途径则是降低PDN阻抗。

1.2电源网络的组成及优化方案

由图1得知,PDN主要由电源调节模块VRM(Voltage Regulator Module)、电源地平面对、去耦电容等组成[4]。它们分别在不同的频段内为工作的器件提供电流。VRM及储能电容组成的供电系统在0到1 MHz频率范围内保持电源网络的低阻抗;芯片的去耦电容包括钽电容和中高频陶瓷电容在1 MHz到几百MHz范围内为工作的器件提供低阻抗;电源地平面对能够在100 MHz以上为工作器件提供低阻抗回流路径。在实际工程中,则主要在PCB电源地平面对之间添加一系列不同容值的电容及在工作器件的电源地引脚上添加高频陶瓷电容[5]。

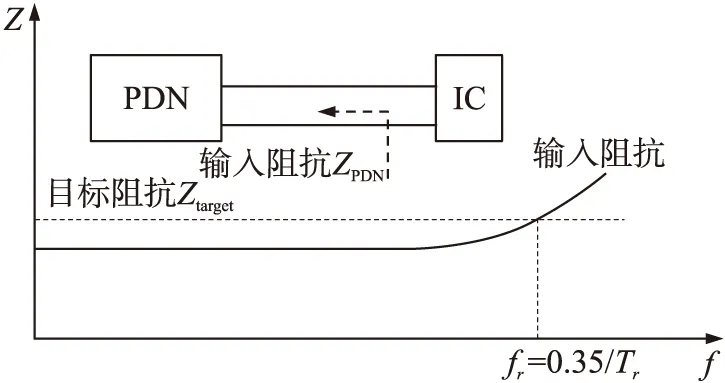

图2 频域目标阻抗法PDN设计

从工作器件电源引脚向系统电源网络看去,即为IC的输入阻抗,如图2。通过降低工作器件的输入阻抗,来减小SSN对系统电源和其他器件的影响。由此我们可以定义频域目标阻抗,即根据系统要求,确定最大电压波动范围,并根据芯片的功耗来得到最大平均电流,则目标阻抗可根据公式:

(3)

只要输入阻抗在一定频率范围内低于目标阻抗,即达到设计要求。但实际工作器件并不止一个电源引脚,如DSP往往有很多个电源地引脚,单个电源引脚只能反映芯片工作时的本地特性,并不能反映芯片工作时的全局特性,因此在仿真时将工作器件的所有电源和地引脚分别并在一起,相当于只有一对电源地引脚,观察它的输入阻抗。此方法能更精确的表示芯片的输入阻抗特性[6]。

通过添加去耦电容,优化PDN输入阻抗。实际电容模型可等效为RLC的串联电路,L为电容自身封装电感和安装寄生电感之和,R为电容总的寄生电阻。当电感阻抗矢量与电容阻抗矢量之差为零时,电容发生自谐振,此时电容阻抗最小,能有效地为射频电流提供低阻抗回流路径。其等效阻抗和自谐振频率关系为:

(4)

基于电容自谐振原理选择去耦电容方法很多,如Decade Methods和Flat Response法[7]。这2种方法都是在给定频段内使用一系列不同容值的电容器来设计PDN,但这2种方法往往受到电容器种类的限制,因此本文使用了频域对数法选择去耦电容器。具体方法:确定VRM不能提供低阻抗时对应的频率点;确定需要设计PCB的频域目标阻抗和信号截止频率;将设计频段在对数坐标下平均地划分为N段(N为实际所能提供的最大电容容值种类决定N≥4);确定所提供的电容器种类的自谐振频率;依次寻找落在每个频段的电容器种类;每个频段的电容器数量根据低于目标阻抗来决定[8]。

2 电源完整性仿真分析

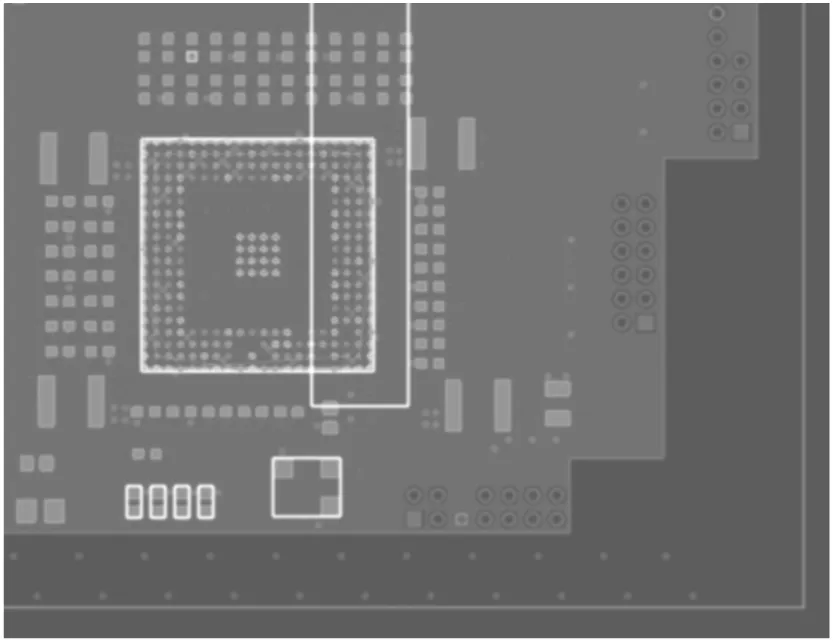

本文以XX电子控制器10层PCB板为例,该板上包括数字电路和模拟电路,其中DSP芯片为主要的高速器件和噪声源,因此本文以DSP的3.3 V电源网络为例,进行了PDN阻抗分析和同步开关噪声分析。通过ANSYS公司的Ansoft SIwave仿真软件对DSP的3.3 V电源网络进行了详细的电源完整性分析;通过在SIwave中提取DSP与SDRAM之间的数据线S参数模型并在Ansoft Designer中搭建仿真电路,从时域观察对比了同步开关噪声的抑制情况。

图3 PCB板3.3 V电源平面部分示意图

2.1电子控制器仿真前的计算

通过查找DSP芯片的芯片手册及功耗手册得到3.3 V电源最大电压波动范围为5%,由最大平均功耗计算得到平均电流为250 mA,则目标阻抗为:3.3×5%/0.25=0.66 Ω;信号的最短上升时间为0.5 ns,则由公式:0.35/Tr[9]得信号截止频率为700 MHz(Tr是指信号的上升时间,0.35为一个比例常数)。

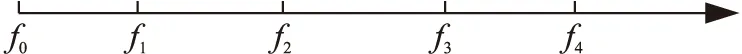

由于电源稳压模块及储能电容可以对DC到1 MHz以内的瞬态电流做出响应。因此在1 MHz到700 MHz范围内需要在芯片附近添加一系列去耦电容为工作器件提供瞬态电流,即为芯片提供低输入阻抗。假设最大提供电容器容值种类N为4,则可计算在1 MHz到700 MHz范围内:f0=1 MHz,f1=5.14 MHz,f2=26.4 Mz,f3=135.8 MHz,f4=700 MHz;所选择的电容器容值分别为:2.2 μF、100 nF、10 nF、1 nF;电容的安装寄生电感分别取3 nH、2 nH、1.5 nH、1 nH;根据电容自谐振原理可计算他们的自谐振频率分别为:1.96 MHz、11.3 MHz、41 MHz、159 MHz。通过观察可知所选电容的安装自谐振点都分别落在图4中的频段内,因此可以选择这4种电容对PDN进行设计。

图4 设计频段分割示意图

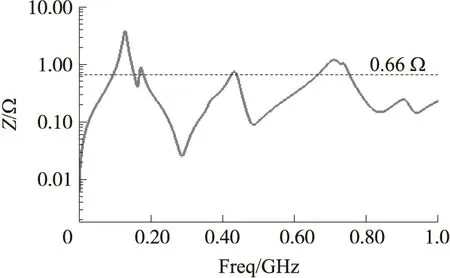

图5 优化前PDN输入阻抗

2.2电子控制器PCB板仿真分析

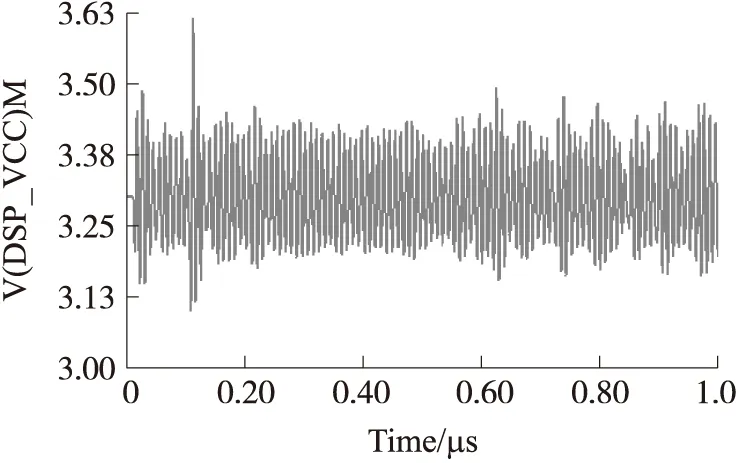

从图5可以看出在700 MHz内频率在100 MHz、400 MHz、700 MHz几个频段都出现了大的阻抗波动,并超过了目标阻抗。同时在Designer中搭建仿真电路观察到同步开关噪声引起的电压波动范围在3.1 V到3.6 V,远超过了最大电源波动范围0.165 V,如图6所示。

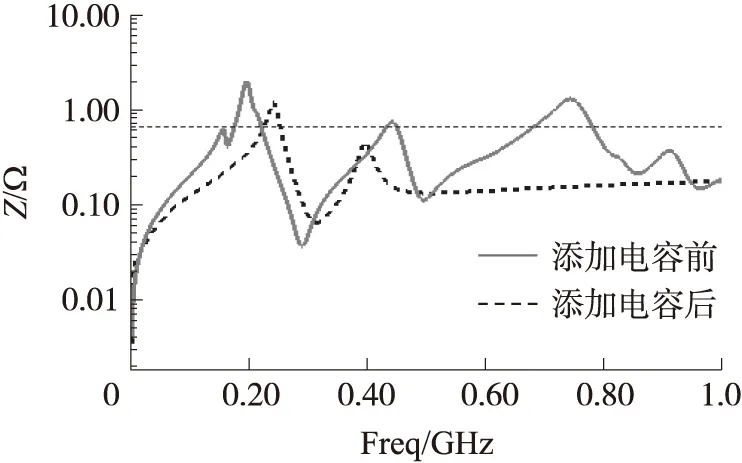

(1)可先在DSP芯片4个角落分别对称添加1个2.2 μF电容,图7为添加电容前后对比图。

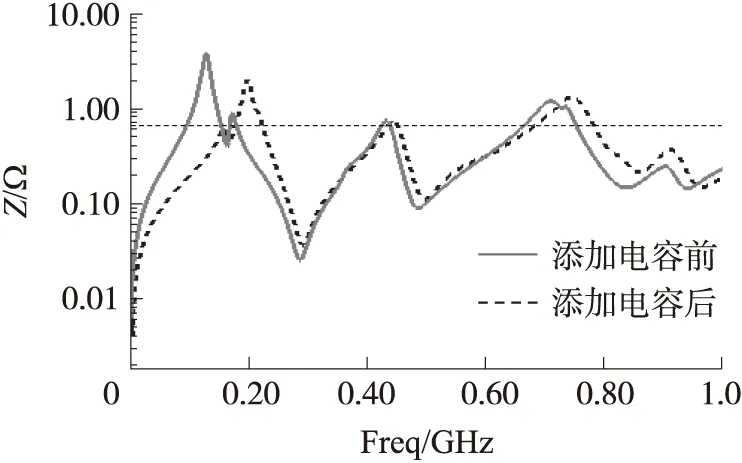

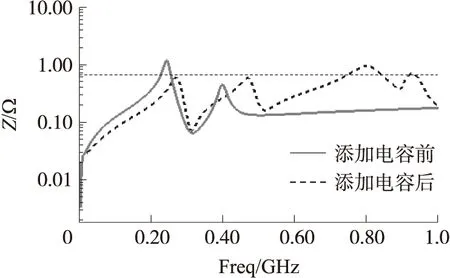

(2)在DSP芯片附近添加4个100 nF的电容。图8为添加电容前后阻抗曲线对比图。

(3)在DSP芯片附近再添加多个10 nF的电容,并尽量靠近DSP的电源地引脚。图9为添加电容前后阻抗曲线对比图。

(4)在DSP芯片附近再添加12个1 nF高频去耦电容,并尽量靠近芯片或直接添加在芯片的电源地引脚上。

图6 优化前电源波动

图7 DSP阻抗曲线对比图

图8 DSP阻抗曲线对比图

图9 DSP阻抗曲线对比图

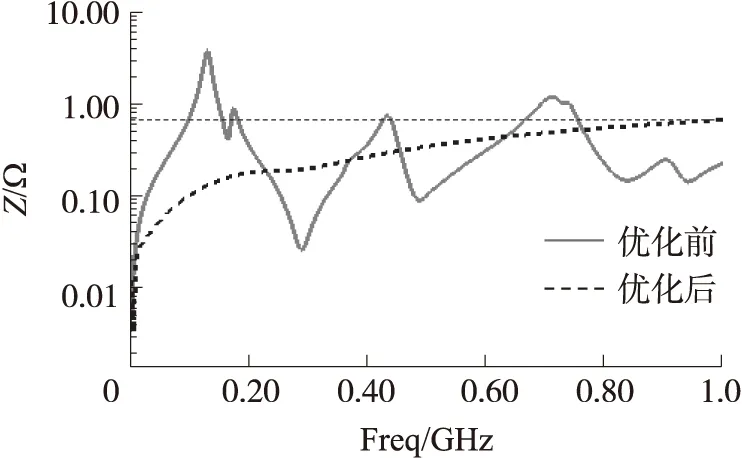

从图10可以看出工作器件3.3 V电源网络的输入阻抗在700 MHz内低于0.66 Ω,且没有大的阻抗波动,即PDN阻抗设计达到了要求。从图11观察优化前后SSN抑制情况,可以看到优化后电压波动远小于0.165 V,即SSN噪声得到了显著的抑制。

图10 优化前后阻抗曲线对比图

图11 优化前后电源波动对比图

3 结论

本文通过使用Ansoft公司的仿真软件对XX电子控制器PCB板进行电源完整性分析,通过使用频域对数法选择去耦电容器设计了工作器件DSP的3.3 V电源网络的输入阻抗,并通过时域直观的对比了优化前后SSN的抑制情况。验证了优化PDN抑制SSN的有效性。

参考文献:

[1]Senthinathan R,Prince J L.Simultaneous Switching Ground Noise Calculation for Packaged CMOS Devices[J].IEEE Journal of Solid-State Circuits,1991,26(11):1724-1728.

[2]Swaminathan M,Chung Daehyun,Grivet-Talocia Stefano,et al.Designing and Modeling for Power Integrity[J].IEEE Transactions on Electromagnetic Compatibility,2010,52(2):288-309.

[3]陈伟,黄秋元,周鹏.高速电路信号完整性分析与设计[M].北京:电工业出版社,2009:109-118.

[4]闫静纯,李涛,苏浩航.高速高密度PCB电源完整性分析[J].电子器件,2012,35(3):296-299.

[5]Smith Larry D,Anderson Raymond E,W Forehand Douglas,et al.Power Distribution System Design Methodology and Capacitor Selection for Modern CMOS Technology[J].IEEE Transtrationon Advanced Packaging,1999,22(3):284-290.

[6]张木水,李玉山.信号完整性分析与设计[M].北京:电工业出版社,2010:179-195.

[7]Weir Steve,Teraspeed Consulting Group.Bypass Filter Design Considera-tions for Modern Digital Systems,A Comparative Evaluation of the Big "V",Multi-pole,and Many Pole Bypass Strategies.Design Con,2006.

[8]杨丽湘.基于遗传算法的电源分配网络设计[D].西安:西安电子科技大学,2010.

[9]陈伟,黄秋元,周鹏.高速电路信号完整性分析与设计[M].北京:电工业出版社,2009:24-30.

余青旺(1988-),男,汉族,安徽人,硕士,研究方向为电源完整性分析(PI),yuqingwang08@163.com;

张赤斌(1968-),男,汉族,教授,硕士生导师,研究方向为机电控制及EMC可靠性研究,chibinchang@aliyun.com。

SuppressionAnalysisofSSNSimulationinHigh-SpeedPCB

YUQingwang1,ZHANGChibin1*,WANGGuangping2

(1.School of Mechanical Engineering,Southeast University,Nanjing 210096,China;2.Aviation Motor Control System Institute,Wuxi Jiangsu 214063,China)

Abstract:From the aspect of Power Integrity(PI),the effective way of suppressing simultaneous switching noise(SSN)is reduce chip’s input impedance.With the method of target impedance determined by the number of decoupling capacitance which frequency domain logarithmic is used to optimize power delivery network(PDN).Based on XX-electronic-controller PCB,a high-speed complicated PCB’PDN is analyzed and optimized by Ansoft SIwave and using time-domain observes the inhibition of SSN by Ansoft Designer.The simulation resultes show that the optimization of power distribution network can reduce SSN effectively.

Key words:PI;SNN;target impedance;Ansoft SIwave;Ansoft Designer

doi:EEACC:523010.3969/j.issn.1005-9490.2014.04.006

中图分类号:TN41

文献标识码:A

文章编号:1005-9490(2014)04-0609-04

收稿日期:2013-07-24修改日期:2013-08-14