POWERLINK 网络管理的Verilog HDL实现

赵粹臣,杨志家,刘 念

(1.沈阳理工大学 信息科学与工程学院,辽宁 沈阳 110159;2.中国科学院沈阳自动化研究所 中国科学院网络化控制系统重点实验室,辽宁 沈阳 110016)

POWERLINK网络管理的Verilog HDL实现

赵粹臣1,2,杨志家2,刘 念1

(1.沈阳理工大学 信息科学与工程学院,辽宁 沈阳 110159;2.中国科学院沈阳自动化研究所 中国科学院网络化控制系统重点实验室,辽宁 沈阳 110016)

为提高协议栈的通信实时性,利用数字电路具有的速度优势,设计了一系列电路结构来实现数据链路及以下层的功能。其中决定通信功能单元运行方式的网络管理(NMT)居于核心地位。采用数据存储排序电路结构来按顺序地存储事件。在不改变协议一致性的情况下,定义了新的主状态,用来读取事件存储队列中的新事件,实现NMT状态机的功能,以及在NMT状态改变后做相关的处理。利用Verilog HDL语言设计实现,用EDA开发软件Modelsim SE进行功能仿真,验证了功能的正确性。

POWERLINK;以太网;Verilog;EDA

在工业控制系统中,实时可定义为系统在一个可准确预见的时间范围内对某事件作出反应。反应时间由具体的应用场合决定。过程控制的反应时间只需秒级,但是传动控制的反应时间则需要微秒级。工业控制领域对实时性要求很高。工业以太网的实时响应时间可以达到5~10ms,但是对于响应时间小于5ms的应用,工业以太网则无法胜任。因此各大公司和组织提出了多种实时以太网解决方案,目前主要有EPA[1]、Ethernet/IP[2]、Modbus-IDA、PROFINET[3]、EtherCAT[4]和Ethernet POWERLINK[5]等。其中Ethernet POWERLINK的性能优越,具有很强的竞争力。

Ethernet POWERLINK是一种基于快速以太网,用于数据采集及工业控制领域数据传输的实时以太网解决方案。该技术遵循OSI模型,其MAC层和PHY都是标准的以太网,而对数据链路层进行了修改。该技术提供了C语言实现的开源协议栈,可方便地移植到不同的目标操作系统中。

NMT(Network Management,网络管理)管理网络状态,在协议栈中居于核心的地位。NMT状态机对通信功能单元的运行方式起到决定性作用,协议栈在某一NMT状态下严格执行某一类功能,所有的功能部分都跟随NMT状态有序运行。无论MN(主站)还是CN(从站)都经由通用初始化过程来启动状态机,而后根据不同的NodeId(节点号)来进入属于MN的状态机部分或者CN部分。在开源的POWERLINK代码协议栈中,采用C语言实现NMT功能。

Verilog HDL是一种硬件描述语言(HDL:Hardware Description Language),能够描述数字系统的行为、数据流与结构[6]。采用Verilog HDL描述的状态机能够实现硬件算法。文中将原先由C语言实现的NMT功能改为由Verilog HDL描述的状态机实现。

1 NMT的总体结构

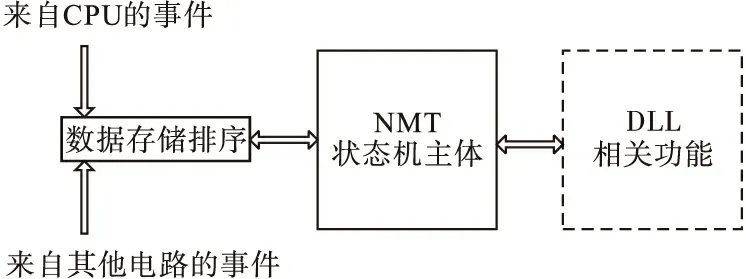

NMT状态机由输入的NMT事件来推动运行,因为有时事件并不能立即得到处理,所以必须有一个数据存储排序结构。因此状态机的设计结构应由两部分组成,一是状态机主体部分,一是事件存储排序结构。总体结构框图如图1所示。

数据存储排序模块类似于同步FIFO[7](First In First Out,先进先出)结构,但是并不设置full信号,因为事件的数量有限,并不足以使存储溢出。该结构深度为32字节,宽度为8bit。

图1 总体结构框图

NMT状态机主体模块在处理完之前的事件,并且数据存储排序结构不为空的时候,读取新的事件作为自身的输入,推动状态机运转。相比原先由C语言实现的方式,该模块做了较大调整,新设置若干主体状态,而原先的状态机包含在其中一个主体状态中。状态机主体右侧接口连接用来模拟DLL相关功能的激励文件,当状态改变时,NMT主体部分通知后者,后者做出确认后再取出新的事件。整个执行过程如此反复。

2 各模块设计

2.1 数据存储排序模块

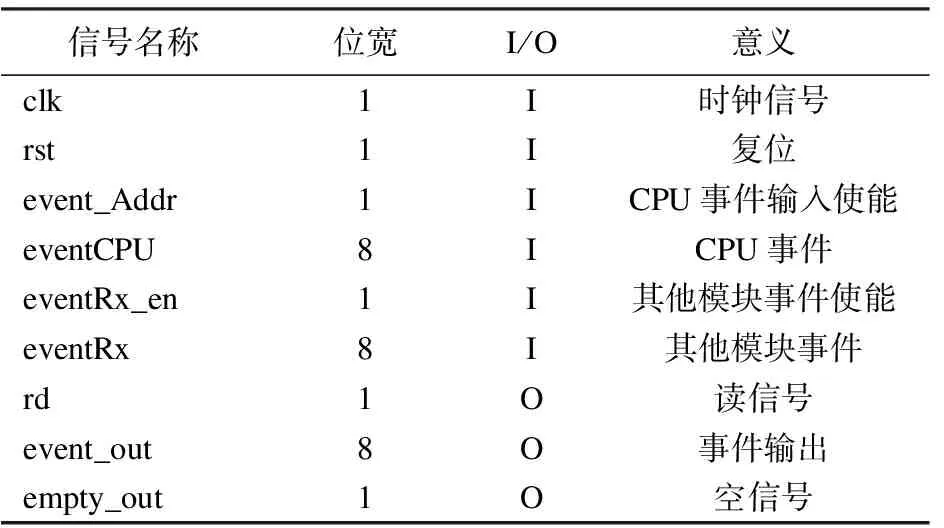

该模块的输入输出信号如图2所示。该模块允许两个事件端口同时输入,同时被存储,而来自CPU的事件存储位置靠前。

图2 数据存储排序模块

各信号的意义见表1。

表1 端口各信号的意义

该模块深度为32字节,宽度为8bit,每次写入一个事件,内部写指针就加1,同时写入则加2;而读出一个事件,读指针则加1。当各指针数值等于31,再加1时则跳回到0,如此周而复始,当读指针等于写指针时,则空信号有效,表示事件已经被取空。

2.2 NMT状态机主体模块

为实现NMT功能,在确保协议一致性的基础上,对原先C语言实现的方案作了较大改动,定义了8个主状态,主状态之间的转换如图3所示。这8个状态及其功能为:

NmtReady:将上一轮的新NMT状态寄存器的值赋给旧NMT状态寄存器,并且发出读信号到存储队列;

eventRd:将读信号清零;

eventGet:将事件存储队列输出的事件寄存以供NMT状态机使用;

NmtSm:NMT状态机功能主体;

staCh:寄存新的NMT状态,然后发送状态改变信号,通知数据链路层(DLL)NMT状态已经改变了,DLL会同时寄存新旧两个状态;

staCh_n:状态改变信号清零,请求DLL处理NMT状态改变这一事件并做好相应的一系列准备工作;

dllDeal_n:请求处理信号清零;

dllDealwait:等待DLL处理NMT状态改变这一事件,并且做好一系列准备工作,直到得到DLL对处理请求的确认,再跳到NmtReady状态。

其中,必须输出新的NMT状态和旧的NMT状态给数据链路层,并且必须准确控制状态机,使得它只有等到DLL做好准备才能跳到下一状态,否则会出现数据流的紊乱,进而导致整个系统的功能设计失败,这一点尤为关键。

在图3中,当主状态处于NmtReady,并且事件队列不空(有新的事件)的时候,主状态机发出读信号,读取事件队列中的事件,开始新一轮的状态机循环。根据NmtSm状态下包含的NMT状态机功能主体运行的结果,即NMT状态是否改变,可以有两种状态转换方式:1)当NMT状态改变时,则继续依次经历staCh、staCh_n、dllDeal_n、dllDealwait这几个状态,而后跳回到NmtReady状态;2)当NMT状态未变时,则直接跳回到NmtReady状态,结束这一轮循环。

图3 主状态转换图

对于NmtSm状态下包含的NMT状态机功能主体,可分为两大部分,一是通用初始化部分,二是主站NMT状态机或者从站NMT状态机部分。各部分状态转换关系如图4所示。

GsOff为关闭状态,通用初始化部分NMT状态与所实现的功能为:

GsInitialising:完成基本的节点初始化;

GsResetApplication:设置制造商特定行规区和标准设备行规区的参数;

GsResetCommunication:设置通信行规区的参数;

GsResetConfiguration:用对象字典中的配置参数进行设备配置。

图4阴影部分中的CN状态机的NMT状态和功能为:

CsNotActive:只监视网络状态;

CsPreOperational1:接到MN的SoA帧才发送一帧;

CsStopped:节点不参与数据帧交换,但监视SoA帧;

CsPreOperational2:忽略接到的PDO数据,但响应SoA帧;

CsReadyToOperate:参与周期帧的交换;

CsOperational:CN的正常运行状态;

CsBasicEthernet:进行传统以太网通信。

MN状态机的状态和功能为:

MsNotActive:监视网络状态,确保没有其他活动的MN;

MsPreOperational1:开始执行POWERLINK短周期;

MsPreOperational2:开始执行等时同步POWERLINK周期;

MsReadyToOperate:执行等时同步POWERLINK周期;

MsOperational:POWERLINK正常运行状态;

MsBasicEthernet:进行传统以太网通信。

图4 NMT状态机功能主体

如图4所示,状态机最初处于GsOff状态,在事件的推动下,首先经历一个初始化过程,即图中的NMT_GS_INITIALISATION,而后根据具体的配置,决定站点进入MN状态机或者CN状态机。

3 仿真

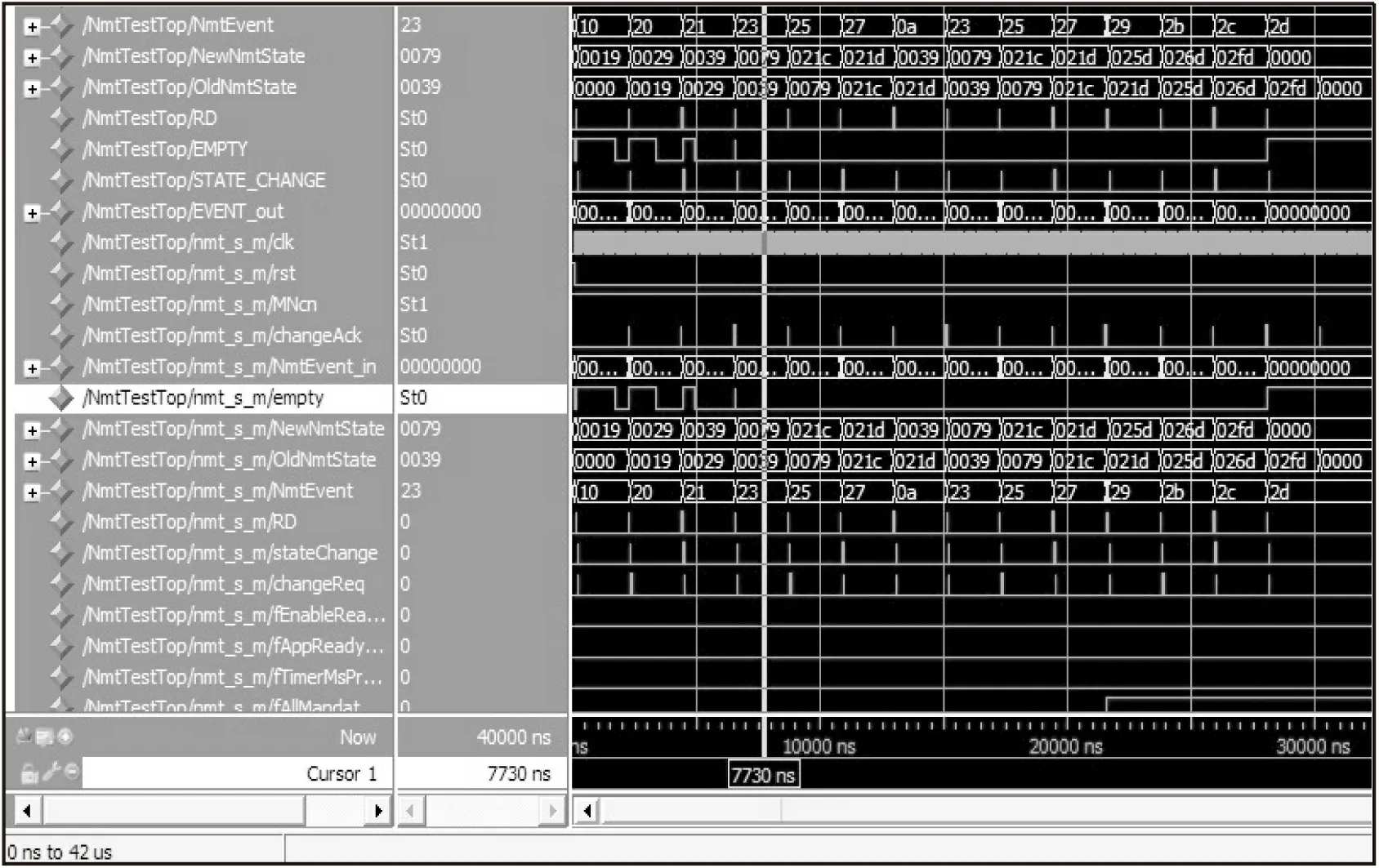

在普通的PC机平台之上,使用仿真软件Modelsim SE[8]进行功能仿真。仿真模型如图5所示。用同一个仿真模块来完成两个作用:事件来源,以及DLL中与NMT相关的那部分功能。

涉众型经济犯罪中,很少是单人作案的,所以大部分涉众型经济犯罪都是有组织的。犯罪嫌疑人为了提升可信度,往往会通过合法公司的开设方式实施经济犯罪,而且在这个过程中需要多个人的分工完成,这也需要组织的严密性和合理性[2]。这些犯罪分子往往是通过对社会上不法分子的勾结,并与金融机构的员工串通,实施犯罪。银行部分内部人员在大量金钱的诱惑下,意志薄弱,难以抵抗腐败,这也是导致犯罪分子得逞的重要原因。比如,中国银行广州分行会计组长利用职务之便与某诈骗公司勾结,伪造存款单据、伪刻公章,共骗取广州12家企事业单位超过8 000万元。

用Verilog HDL语言编写激励信号文件[9],向状态机输送事件,使之从GsOff状态一直转换到MsOperational状态,而后再关闭到GsOff状态,通过这一周而复始的过程来检验这两个模块(NMT状态机和数据存储排序模块)的功能。对于其中的TimerMsPreOp1同时加上一个来自DLL功能区域的事件DllCeSoa,用来检验两事件同时进入队列时,队列能否正确完成排序功能。输入的事件(只有一个来自DLL功能区域)及其十六进制编码按照顺序如下:

图5 仿真模型

SwReset(8′h10)

EnterResetApp(8′h20)

EnterResetCom(8′h21)

EnterResetConfig(8′h23)

EnterMsNotActive(8′h25)

TimerMsPreOp1(8′h27)同时DllCeSoa(8′h0A)

EnterResetConfig(8′h23)

TimerMsPreOp1(8′h27)

AllMandatoryCNIdent(8′h2A)

TimerMsPreOp2(8′h29)

EnterReadyToOperate(8′h2B)

EnterMsOperational(8′h2C)

SwitchOff(8′h2D)关闭

若功能正确,则随之产生的NMT状态变化过程应当为:

GsOff( 16′h0000)

GsInitialising(16′h0019)

GsResetApplication(16′h0029)

GsResetCommunication(16′h0039)

GsResetConfiguration(16′h0079)

MsNotActive(16′h021C)

MsPreOperational1(16′h021D)

GsResetCommunication(16′h0039)

GsResetConfiguration(16′h0079)

MsNotActive(16′h021C)

MsPreOperational1(16′h021D)

MsPreOperational2(16′h025D)

MsReadyToOperate(16′h026D)

MsOperational(16′h02FD)

GsOff(16′h0000)

激励文件部分代码如下:

′timescale 1ns/1ns

′define timeslice 20

module NmtTestSig;

always#(′timeslice/2)CLK=~CLK;

initial

begin

CLK=0;

RESET=1;

MNcn=1;

CPU_ADDR=0;

RX_EN=0;

CHANGE_ACK=0;

CPU_EVENT=NoEvent;

RX_EVENT=NoEvent;

#100;

RESET=0;

#(′timeslice+′timeslice/2);

CPU_ADDR=1;

CPU_EVENT=SwReset;

#(′timeslice);

CPU_ADDR=0;

CPU_EVENT=NoEvent;

…………………………以下代码从略。

仿真结果如图6所示。

图6 仿真结果图

图6中的NewNmtState表示NMT状态发生改变后的新状态,OldNmtState则记录了在NMT状态发生改变后,未改变之前的旧状态。从图6可见,NMT状态机最初处于GsOff( 16′h0000)状态,随后来自CPU的事件SwReset(8′h10)使状态机转换至GsInitialising(16′h0019)状态。CPU按照这种方式,利用输入事件的方法逐步使NMT状态机运转,事件依次为EnterResetApp(8′h20),EnterResetCom(8′h21),EnterResetConfig(8′h23),EnterMsNotActive(8′h25);随之变化的状态依次为GsResetApplication(16′h0029),GsResetCommunication(16′h0039),GsResetConfiguration(16′h0079),MsNotActive(16′h021C)。在CPU输入事件TimerMsPreOp1(8′h27)的同时,其他电路也输入事件DllCeSoa(8′h0A),以此来检测数据存储排序模块是否能够准确存储同时输入的事件,随之的状态改变为GsResetCommunication(16′h0039),GsResetConfiguration(16′h0079)。在前述事件的依次作用下,NMT状态最终转换到GsOff( 16′h0000)状态,完成了一个状态机循环。图中显示的状态变化结果符合预期,所以验证了设计功能的正确性。

4 结论

NMT状态机是POWERLINK通信协议栈中的核心模块,该模块通常是由C语言实现,包含在POWERLINK开源代码之中。现对原先的实现方式做了调整,设计了电路排序结构代替原先的数据结构,定义了新的主状态,采用Verilog HDL语言进行描述,经仿真验证,功能正确可行。

[1]刘宁.EPA 工业以太网实时性分析及调度方法的研究[D].大连:大连理工大学,2010.

[2]LI W,ZHENG S,CHEN W.Research and Application of Ethernet/IP Industrial Ethernet[J].Electronic Design Engineering,2011,19(9):26-29.

[3]Feld J.PROFINET-scalable factory communication for all applications[C].Factory Communication Systems,2004.Proceedings.2004 IEEE International Workshop on.IEEE,2004:33-38.

[4]Jansen D,Buttner H.Real-time Ethernet:the EtherCAT solution[J].Computing and Control Engineering,2004,15(1):16-21.

[5]Cena G,Seno L,Valenzano A,et al.Performance analysis of Ethernet Powerlink networks for distributed control and automation systems[J].Computer Standards & Interfaces,2009,31(3):566-572.

[6]Reese R B,Thornton M A.Introduction to logic synthesis using Verilog HDL[J].Synthesis Lectures on Digital Circuits and Systems,2006,1(1):1-84.

[7]Tsigas P,Zhang Y.A simple,fast and scalable non-blocking concurrent fifo queue for shared memory multiprocessor systems[C].Proceedings of the thirteenth annual ACM symposium on Parallel algorithms and architectures.ACM,2001:134-143.

[8]Aparna P R,Thomas N.Design and implementation of a high performance multiplier using HDL[C].Computing,Communication and Applications(ICCCA),2012 International Conference on.IEEE,2012:1-5.

[9]李瑛,张盛兵.Verilog Testbench 设计技巧和策略[J].计算机工程与应用,2003,39(10):128-130.

ImplementationofPOWERLINKNetworkManagementUsingVerilogHDL

ZHAO Cuichen1,2,YANG Zhijia2,LIU Nian1

(1. Shenyang Ligong University,Shenyang 110159,China;2. Key Lab. of Networked Control Systems,Shenyang Institute of Automation,Chinese Academy of Science,Shenyang 110016,China)

In order to take advantage of the speediness of digital circuit to improve the real-time performance of protocol stack,a series of circuits are designed to implement the functions of data link layer and layer below.The network management(NMT)which determines the operational mode of communication functional unit is on the core status.A circuit for data storage and sorting is used to store the events orderly.Without changing protocol consistency,a few new main states are defined to read events from the event queue,implement the function of the NMT state machine,and do some relevant treatment after the NMT state has been changed.All of them are designed by Verilog HDL.Finally,the circuits are simulated by Modelsim SE,an EDA development software,and the correctness of the function of them is verified.

POWERLINK;ethernet;Verilog;EDA

2013-11-29

国家863项目(2013AA040301)

赵粹臣(1988—),男,硕士研究生.通讯作者: 杨志家(1968—),男,研究员,研究方向:片上系统设计与验证.

1003-1251(2014)05-0021-06

TN495

A

马金发)