一种高效视频编码插值滤波VLSI架构设计

连晓聪,周 巍,段哲民,李 茸

(西北工业大学电子信息学院,西安710072)

1 概述

由联合视频编码组制定的高效视频编码(High Efficiency Video Coding,HEVC)标准,比以前的编码标准实现了更高的编码效率[1],尤其是在高分辨率和高帧率的视频应用中[2]。HEVC较高的编码性能主要体现在自适应内插值滤波器、1/8像素运动估计、多参考帧内预测、基于块的自适应环路滤波器等[3]。然而,这些先进的视频编码技术在编码进程中需要更大的计算复杂度和内存带宽。因此,设计一个快速的编码器超大规模集成电路(Very Large Scale Integration,VLSI)架构对于实现实时视频应用是十分重要的。

运动估计[4](Motion estimation,ME)是 HEVC中运用相邻帧的时间相关性最多的部分[5],它也是编码过程中消耗时间最长的进程。在HEVC中,一个全新的8抽头的内插值滤波器应用于ME的分数像素点预测中。对于亮度插值,其精确度是1/4像素,所以总共有15个位置的像素值需要被计算出来。对于8×8子块的预测,最多需要16×16的参考像素。相比H.264/AVC标准中使用的6抽头滤波器[6],8抽头滤波器在硬件实现时将花费更多的面积。因此,设计一个高效的内插值滤波器VLSI架构对于实时实现高品质的视频是必要的。

本文设计一个内插值滤波器VLSI架构。为便于VLSI实现,提出一种快速内插值滤波算法[7],将所有的4×8,4×16和12×16预测单元从处理队列中跳过。然后根据提出的快速算法,设计和实现内插值滤波器VLSI架构,提出一个可重新配置的滤波器,减少使用的加法器的数目,并设计单元块复用的硬件结构,以降低硬件的实现面积。

2 HEVC内插值滤波算法

在最新的视频编码标准HEVC中[8],一个全新的8抽头内插值滤波器应用于分数像素运动估计中[9]。对于亮度块来说,精度是1/4像素,而对于色度块,精度是1/8像素。本文的研究是对亮度块的内插值滤波器进行的,对1/2像素点采用的8抽头内插值滤波器,而对于1/4像素点,采用的是7抽头内插值滤波器。

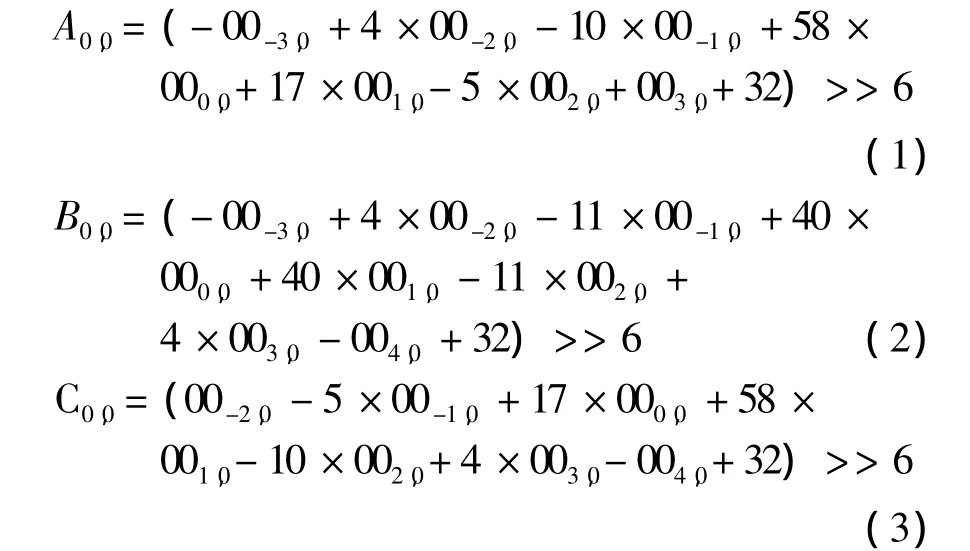

先进行1/2像素点的内插值滤波。图1给出的是插值点的位置和参考像素点的位置,其中02像素点是对水平方向上的8个00像素点应用式(2)进行水平1/2插值得到的,20像素点是对垂直方向上的8个00像素点应用式(2)进行垂直1/2插值得到的,22像素点是经水平1/2插值和垂直1/2插值后得到的。在完成1/2像素点的内插值滤波之后,计算结果将被传输到下一模块,经哈达玛变换后计算数据块的预测残差绝对值总和(SATD),找到最佳的运动矢量(Motion Estimation,MV)[10],再进行 1/4像素点的内插值滤波。在不同的运动矢量下需要得到的就是00,02,20,22像素点周围的8个1/4像素点的插值结果。其中,01,03像素点分别是在水平方向上利用式(1)和式(3)对00像素点进行插值得到的;10,11,12,13像素点分别是在垂直方向上应用式(1)对00,01,02,03 像素点进行插值得到的;21,23像素点分别是在垂直方向上应用式(2)对01,03像素点进行插值得到的;30,31,32,33像素点分别是在垂直方向上应用式(3)对00,01,02,03像素点进行插值得到的。

图1 像素点的位置

对于8×8子块的预测,最多需要16×16预测块的参考像素值。相比于 H.264/AVC中使用的6抽头内插值滤波器,HEVC中使用的8抽头内插值滤波器需要消耗更多的面积。因此,设计一个高效的亮度插值的VLSI架构对于实时实现视频编码是十分重要的。

3 架构设计

3.1 快速内插值滤波算法

HEVC中的帧间预测的预测单元(PU)有8种不同的分割块[11]:4种对称的分割块(2N×2N,2N×N,N×2N,N×N)和4种非对称的分割块(2N×nU,2N ×nD,nL×2N,nR ×2N)。

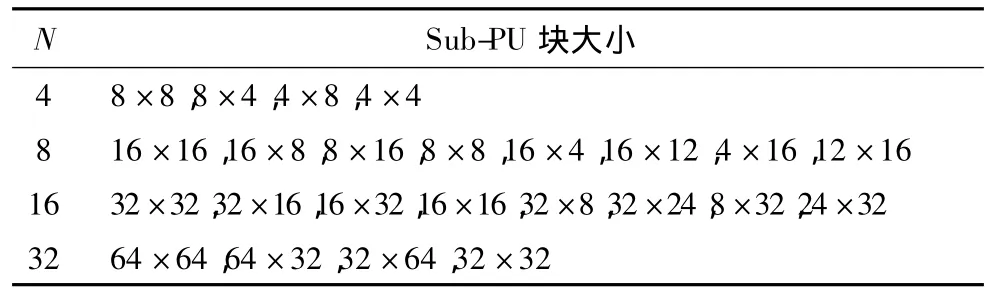

在HEVC中帧间预测的PU块中最大处理单元(LPU)为64×64块,根据上述所描述的分割规则,每个 LPU可以分割成21种 sub-PU,如表1所示。

表1 帧间预测PU块的分割模式

从表1中可以看出,如果要对每种大小的块分别设计插值滤波的硬件结构,硬件的门数和面积是非常大的,所以,在VLSI架构的设计中,要考虑通过将最小的单元块拼接复用来实现较大块的插值滤波操作[12]。但如果选择宽度为4的块为最小复用块,对64×64块要复用16次,结构会很复杂,所以提出一种快速算法,如图2所示。将4×8,4×16,12×16大小的PU从处理队列中跳过,再用A,B,C 3种类型的滤波器进行插值。

图2 快速内插值算法流程

针对本文提出的快速内插值算法,对分辨率为416×240(A),832 ×480(B),1 280 ×720(C),1 920×1 080(D),2 560×1 600(E)的视频序列进行测试,得到的编码性能及码率的变化如表2所示。

表2 不同分辨率的视频序列编码性能及码率

从表2可以看出,在对内插值滤波器的算法进行改进之后,视频编码的峰值信噪比(detal_BR)[13](改进算法的PSNR–原始算法的PSNR)下降平均值为0.041 1 dB,对于编码的性能改变不太明显。同时比特率平均提高1.158%,并能节约10.06%的编码时间,说明多数视频序列在进行内插值操作时对于宽度为4的块并不是很敏感,提出的快速算法能够高效实时地完成内插值滤波操作,并可以较大幅度地降低硬件的实现面积。

3.2 高性能内插值滤波器VLSI架构

基于上述提出的快速内插值滤波算法,本文对内插值滤波器VLSI架构进行设计,结构框图如图3所示,将输入数据进行划分,用8个处理模块进行处理,每个模块处理宽度为8的数据块(在图3中标示为“8×”)。单元块的内插值滤波结构框图如图4所示。

图3 内插值滤波器整体的结构框图

图4 单元块的内插值滤波架构

首先对于水平滤波,设计有3组滤波器(Level1:H_F1/4,H_F2/4,H_F3/4)。其中在进行第 1 轮1/2像素点滤波时,打开 H_F2/4,关闭H_F1/4和H_F3/4。在进行第2轮1/4像素点滤波时,全部打开。对于垂直滤波,设计有4组滤波器(level2,仅在第2轮1/4像素点滤波时打开),V_F1/4,V_F3/4分别对01,03位置进行1/4,3/4垂直滤波,得到11,31和13,33像素点。此外还有另外4组滤波器(level3),其中有2组根据1/2插值时确定的最优MV进行,仅在第2轮1/4像素点滤波打开。在 HOR=0时,V_F1/4,V_F3/4对00进行1/4,3/4垂直滤波得到10,30像素点;否则对02进行1/4,3/4垂直滤波得到12,32像素点。另外2组在第1轮1/2像素点滤波时打开对00,02进行1/2垂直滤波得到20,22像素点;在第2轮1/4像素点滤波时,在1/2插值时确定的最优MV的垂直分量不等于0的情况下,对01,03进行2/4的垂直滤波得到21,23像素点。

3.3 内插值滤波器计算模式的架构设计

从式(1)~式(3)中内插值滤波器插值系数可见,类型A和类型C的系数是对称的。所以A型和C型滤波器的插值可以通过仅由反转输入的参考像素的顺序而用相同的硬件架构来实现。从公式中的系数可以看出,需要10个加法器来实现A型滤波器,9个加法器来实现B型滤波器。因此,8抽头滤波器总共需要至少19个加法器实现硬件。本文所设计的最优的A,B型滤波器硬件结构如图5(a)和图5(b)所示。

图5 内插值滤波器的硬件架构

a,b,c,d,e,f,g,h 为 8 个输入参考像素,使用 C型滤波器时,只要将它们的顺序颠倒过来作为滤波器输入。输出Afir和输出Bfir是A、B型滤波器的内插结果。所提出的滤波器由19个加法器组成,与原有的3种类型的滤波器(29个加法器)可以节省10个加法器,面积降低30%以上。水平和垂直滤波器的结构是相同的。

3.4 单元块复用的数据分割

在得到输入数据时,先要按宽度对数据进行分割,以宽度为64的数据为例。由于在进行插值滤波时使用的是8抽头的内插值滤波器,因此输入数据的宽度应为72,而分割给每个宽度为8复用块的数据宽度都为16,有大量数据重叠。宽度为64的数据分割图表示数据分割的情况如图6和图7所示,其中,对于1/4像素点的数据分割,在1/4水平插值时2组数字分别表示hor<0/hor≥0;而对于3/4水平插值分别表示hor≤0/hor>0。

图6 1/2像素点的数据分割

图7 1/4像素点的数据分割

在进行完数据分割之后,就依次进行水平插值和垂直插值。插值单元的结构如图8所示。这个插值滤波器可以支持大部分不同的块尺寸。例如,一个16×16块可以被划分为2个8×16块,对于64×64的PU,要复用这个基本的插值单元8次。由于进行垂直插值需要8行水平插值的结果,因此使用了一个移位寄存器对水平插值的结果进行处理,避免时序混乱。

图8 8抽头插值单元的结构

4 实现结果

本文针对内插值滤波器进行的内插值滤波算法优化和硬件实现是基于HEVC参考编码器HM8.1的编码结构进行的。编码器配置采用HM8.1的基本类(编码配置文件为encoder_lowdelay_main.cfg)。实验中主要编码参数如下:FramesToBeEncoded=500,Frame–Rate=50,SearchRange=64,其他参数为缺省设置。

本文所设计的硬件结构通过Modelsim仿真进行验证,总共通过了30万PB验证了架构的正确性。表3给出本文设计的架构的实现结果,以及与其他方法的实现结果的比较。

表3 实验结果对比

最大工作频率能够达到193 MHz,在不使用RAM的情况下,实现面积为64.5千门。虽然与文献[15]的HEVC方法相比,实现面积增大了接近一倍,但工作频率能够达到它的4倍,能很好地实现视频的网络传输。同时处理时间也能降低8%。与原始的HEVC方法相比,面积能够降低30%,处理时间节约一半以上。本文所提出的并行8像素插值滤波结构的优势就在于能够在400 MHz的频率下完成720 P视频的实时传输,并能节约131 040 bit的RAM。同时,本文的设计完全能够满足3 840×2 160(4:2:0格式)视频的实时传输。

5 结束语

本文设计了一个高效的内插值滤波器VLSI架构。为便于VLSI实现,首先对内插值滤波器的算法进行了改进,将所有的4×8,4×16和12×16预测单元从处理队列中跳过。在视频编码质量PSNR只降低0.125 6%的基础上,编码时间减少10.06%。然后根据提出的改进算法,设计和实现了内插值滤波器VLSI架构,提出一个可重新配置的滤波器,减少了使用的加法器的数目,并设计了单元块复用的硬件结构。通过采用以上方法,本文的设计仅使用64.5千门来实现,工作频率能够达到193 MHz,并能节约131 040 bit的RAM,可高效实时地完成视频的编码传输工作。

[1] 沈燕飞,李锦涛,朱珍民,等.高效视频编码[J].计算机学报,2013,36(11):2340-2355.

[2] Bull D B,Delp E J,Takamura S,et al.Introduction to the Issue on Emerging Technologies for Video Compression[J].IEEE Journal of Selected Topics in Signal Processing,2011,5(7):1277-1281.

[3] Sullivan G J,Ohm J R,Han Woo-Jin,et al.Overview of the High Efficiency Video Coding(HEVC)Standard[J].IEEE Transaction on Circuits and Systems for Video Technology,2012,22(12):1649-1668.

[4] Favorskaya M,Pyankov D,Popov A.Motion Estimations Based on Invariant Moments for Frames Interpolation in Stereovision[J].Procedia Computer Science,2013,22:1102-1111.

[5] 李 元,何小海,钟国韵,等.一种基于时域相关性的高性能视频编码快速帧间预测单元模式判决算法[J].电子与信息学报,2013,35(10):2365-2370.

[6] Ruiz G A,Michell J A.An Efficient VLSI Architecture of Fractional Motion Estimation in H.264 for HDTV[J].Journal ofSignal Processing Systems,2011,62(3):443-457.

[7] Rhee Chae Eun,Lee Kyujoong,Kim Tae Sung,et al.A Survey of Fast Mode Decision Algorithms for Interprediction and Their Applications to High Efficiency Video Coding[J].IEEE Transactions on Consumer Electronics,2012,58(4):1375-1383.

[8] Ohm J R,Sullivan G J.High Efficiency Video Coding:The Next Frontier in Video Compression[J].IEEE Signal Processing Magazine,2013,30(1):152-158.

[9] Ugur K,Alshin A,Alshina E,et al.Motion Compensated Prediction and Interpolation Filter Design in H.265/HEVC[J].IEEE Journal of Selected Topics in Signal Processing,2013,7(6):946-956.

[10] Lin Jianliang,Chen Yiwen,Huang Yuwen,et al.Motion Vector Coding in the HEVC Standard[J].IEEE Journal of Selected Topics in Signal Processing,2013,7(6):957-968.

[11] Kim Il-Koo,Min Jung-Hye,Lee T,etal.Block Partitioning Structure in the HEVC Standard[J].IEEE Transactions on Circuits and Systems for Video Technology,2012,22(12):1697-1706.

[12] Tanskanen J K,Niittylahti J T.Scalable Parallel Memory Architectures for Video Coding[J].The Journal of VLSI Signal Processing,2004,38(2):173-199.

[13] Lee B,Kim M.No-reference PSNR Estimation for HEVC Encoded Video[J].IEEE Transactions on Brodcasting,2013,59(1):20-27.

[14] Wang Shengzen,Lin Ting’an,Liu Tsu-Ming,et al.A New Motion Compensation Design for H.264/AVC Decoder[C]//Proceedings of IEEE International Symposium on Circuits and Systems.Washington D.C.,USA:IEEE Press,2005:4558-4561.

[15] Guo Zhengyan,Zhou Dajiang,Guto S.An Optimized MC Interpolation Architecture for HEVC[C]//Proceedings of IEEE International Conference on Acoustics,Speech and Signal Processing.Washington D.C.,USA:IEEE Press,2012:1117-1120.