高速低功耗双尾比较器的设计

任志德,郭春生

(北京工业大学电子信息与控制工程学院,北京 100124)

随着人们对便携式电子器件需求的不断增加,对器件的功耗、工作电压、响应速度等性能的要求也越来越严格。器件能工作在低压的优势在于电池的面积和重量均可相对减小,低功耗可延长工作在高频的电池寿命等[1-2]。模数转换器是大多数电子器件中不可或缺的电路模块,比较器却是应用在模数转换器中最基本的一个子模块。比较器的速度、延时、功耗等性能在一定程度上也制约着整个电子器件的性能。

比较器是将模拟信号转换成数字信号的关键模块,它将一个模拟电压信号与一个基准电压相比较,当输入电压大于基准电压时,对应输出二进制数字信号1,反之输出数字0。并且当输入电压的差值增大或者减小时,其输出电压的差值保持恒定不变。由于电路结构的复杂以及MOS器件的不匹配和延时的存在导致了比较器的速度、功耗等重要指标面临着巨大挑战。此外,随着芯片几何尺寸的逐渐减小,低压操作也显得至关重要。然而带有双尾结构的比较器恰能解决以上问题,它在低压应用中具有更好的综合性能。

1 双尾比较器

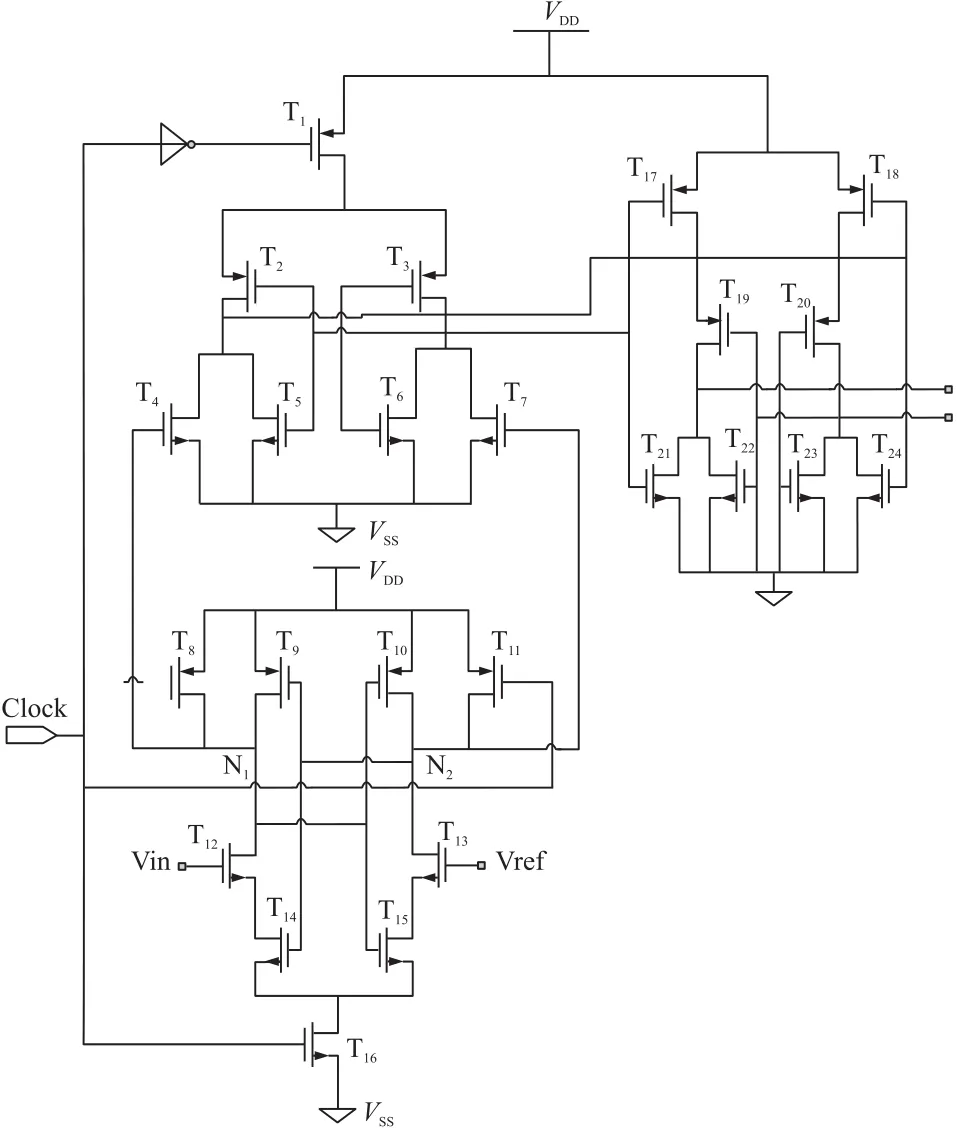

对于一个实际的比较器来说,很难实现满幅输入输出的轨到轨操作,但可利用电容对输入进行简单的去耦来实现轨到轨操作[3],但这种方法不仅增加了生产成本,而且由于其C-V特性中体现出了很强的非线性和很大的噪声干扰,因此这种方法并没有得到广泛应用[4]。图1是一个高速低功耗的双尾比较器[5],这种设计结构避免了基于电容的输入网络,且既能提高电路的驱动能力(提高了电流),又能提高锁存器的再生速度[6]。为获得更大的锁存器再生速度,将两个控制晶体管T9和T10以交叉耦合的方式分别并联在了T8和T11的两边。当时钟为低电平(Clock=0)时,比较器处于复位模式,晶体管T1和T16均处于截止状态以避免产生静态功耗,此时T8和T11导通,可将节点N1、N2迅速拉升至电源电压Vdd,因此T9和T10也处于截止状态。对于晶体管T4和T7,其栅端电压均为Vdd,因此都处于导通状态,进而将两个输出端(T4和T7的漏端)拉低至Vss。当时钟为高电平(Clock=1)时,比较器处于再生模式,此时T1和T16均处于导通状态,但在时钟变为高电平的瞬间,节点N1、N2仍为高电平Vdd,因此在此瞬间 T8、T9、T10、T11、T14、T15均截止,此后,节点N1、N2的电压会随Vin和Vref的不同而有不同程度的下降。如果Vref大于Vin,则节点N1的电压值下降的要比节点N2快,因为T15提供的电流要比T14的大,导致节点N1被拉低的速度更快一些。反之亦然!晶体管T17~T24组成一个SR锁存器,为比较电路提供稳定性。前一级的输出作为SR锁存器的输入,Vout1与Vout2是比较器最终的两个输出端。

图1 传统双尾比较器结构图

虽然此款双尾比较器在低压操作中拥有较好的综合性能,但对其电路结构还可做进一步简化和改善,在速度和功耗等指标上仍有不小的提升空间。

2 改进的双尾比较器

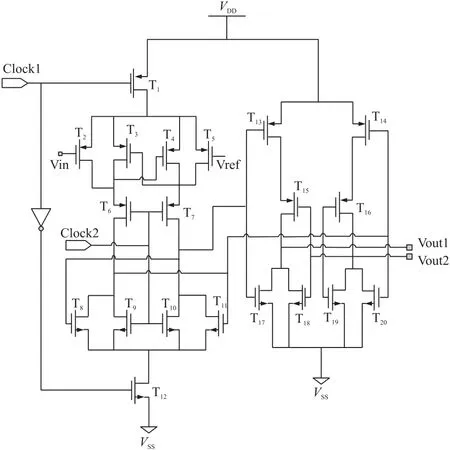

电路的改进思路主要是通过增加交叉耦合式的正反馈通路提高比较器的速度,通过减少电源到地的支路条数和电路中器件的个数来降低功耗。图中主要由一个CMOS锁存电路和一个SR锁存电路构成。其中CMOS锁存电路由晶体管T1~T12构成,SR 锁存电路由晶体管 T13~T20构成。晶体管T1和T12是锁存电路的延伸双尾。CMOS锁存电路用来分辨哪一个输入信号较大,并对输入的信号差值进行放大[7]。当Clock1为低电平时,T1和T12导通,当其为高电平时(复位模式)晶体管T1和T12关断。由于这种拓扑结构具有较少的MOS管层叠堆积,因此与以往其他的动态比较器相比,其具有更低的操作电压[5-7]。而对于图2的双尾比较器,当Clock1为高电平时,复位阶段被激活,这意味着T1和T12都关闭,避免了静态功耗的产生。而Clock2作为采样开关被放置在比较器的输入之前,并具有两倍的输入信号频率。在再生阶段,这些开关均导通,电路的其余输入断开[8]。晶体管 T8~T11形成 NMOS 再生电路。T3和T4是 PMOS 开关,T8和 T11是 NMOS开关,影响切换时间,可以大大提高比较器响应速度[9-10]。晶体管T13~T20构成一个SR锁存器,充当一个存储器,在一个时钟周期内可保持输出数值不变。此SR锁存器作为模拟输入和数字输出的衔接部分,为比较电路提供了较好的稳定性。

图2 改进的双尾比较器结构图

3 仿真与对比

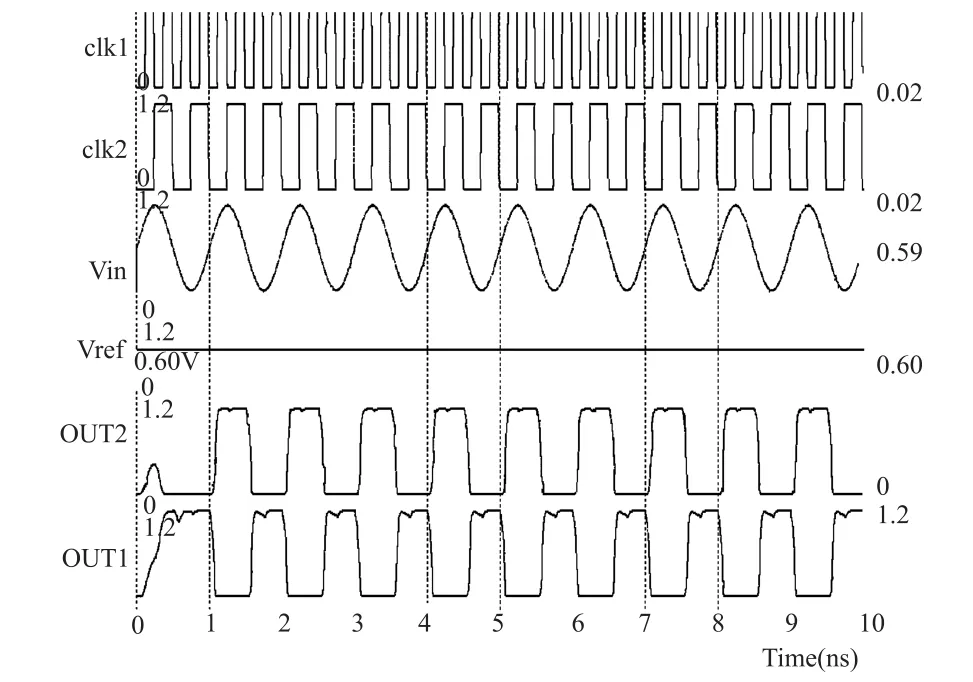

采用Microwind 3.1工具90 nm工艺技术在不同的输入信号频率下对此双尾比较器进行了仿真,满幅电压为1.2 V,轨到轨输入摆幅为0~1.2 V,取Vref=0.6 V。仿真时长设定为10 ns,对于每一个不同频率的输入信号而言,图1中的采样时钟Clock和图2中的Clock2的频率均是输入信号的2倍,以此来保证电路的正常采样。

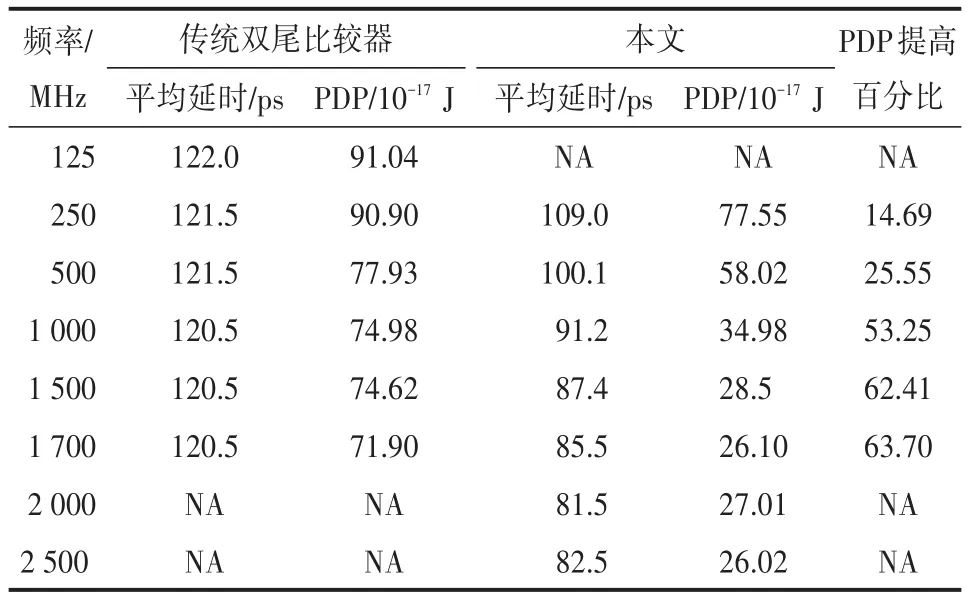

通过仿真可知,该双尾比较器较适合的工作频率范围为175 MHz~2.5 GHz。其输入信号带宽可达2.3 GHz,而之前的传统双尾比较器的输入信号带宽一般为1.7 GHz左右。当比较器工作在0~200 MHz内时,传统比较器的功耗以及功耗延时积稍优于本设计[11]。但当输入信号大于200 MHz以后,本设计体现出了明显优势。首先对于功耗的比较,当输入信号频率小于350 MHz时,传统比较器的功耗要优于本设计,当大于350 MHz时,本设计功耗明显优于传统比较器。且随着工作频率的增加,其节省的功耗也越来越大。具体比较如表1所示。

表1 改进前后功耗对比

然而功耗并不是衡量比较器电路好坏的唯一因素,我们对其延时和功耗延时积(PDP)也做了进一步的仿真和计算,其中功耗延时积是数字电子中衡量电路性能好坏的一个重要品质因数[12]。图3是输入信号频率在1 GHz时的仿真图,在此频率下,每个开关管的平均延时是91.2 ps,功耗为69.17μW,电路中共有18个晶体管,因此电路的功耗延时积(PDP)为35.05×10-17J。比传统比较器提高了约53.25%的PDP性能。

图3 输入信号为1 GHz时的仿真结果

不同输入信号频率下的PDP的比较如表2所示。

表2 改进前后延时与PDP对比表

从175 MHz增至200 MHz期间,传统比较器有较好的功耗延时积,在200 MHz时改进的比较器和传统的比较器的PDP均约为100×10-17J。当输入信号频率大于200 MHz以后,本设计的PDP开始呈现明显优势,传统双尾比较器的最高工作频率约为1.7 GHz,而改进后的双尾比较器最高工作频率可达2.5 GHz。

4 结束语

当该款双尾比较器工作在高频段时,速度、功耗、PDP等性能方面均有明显改善。其拥有2.3 GHz的输入信号带宽,最高输入信号频率可达2.5 GHz,最多可节省43.94%的功耗和63.7%的PDP性能。但当其工作在低频段时,其性能没有体现明显优势,这也是本设计的缺点所在,这有待于我们今后进一步研究和探索。综上所述,本设计更适用于高速、低功耗的模数转换电路之中。

[1]Peluso V,Vancorenland P,Marques A M.A 900 mV Low-Power ΣΔ A/D Converter with 77 dB Dynamic Range[J].IEEE Journal of Solid-State Circuits,1998,33:1887-1897.

[2]Roh H,Choi Y,Roh J.A 89 dB DR 457 W 20 kHz Bandwidth Delta-Sigma Modulator with Gain-Boosting OTAs[J].Analog Inte⁃grated Circuits and Signals Processing,2010,64:173-182.

[3]Wu J.T,Wooley B A.A 100 MHz Pipelined CMOS Comparator[J].IEEE Journal Solid-State Circuits,1988,23(6):1379-1386.

[4]Rivoir R,Maloberti F.A 1 mV Resolution,10 MS/s Rail-to-Rail Comparator in 0.5 μm Low-Voltage CMOS Digital Process[C]//IEEE International Symposium on Circuits and Systems,1997:461-464.

[5]Babayan-Mashhadi S,Reza Lotfi.Analysis and Design of a Low-Voltage Low-Power Double-Tail Comparator[J].IEEE Transac⁃tions on Very Large Scale Integration Systems,2013,22(22):343-352

[6]Khosrov D S.A New Offset Cancelled Latch Comparator for High-Speed,Low-Power ADCs[C]//IEEE Asia Pacific Conference on Circuits and Systems,2010:13-16.

[7]Wang Riyan,Li Kaihang,Zhang Jianqin.A High-Speed High-Res⁃olution Latch Comparator for Pipeline Analog-to-Digital Convert⁃ers[C]//IEEE International Workshop,2007:28-31.

[8]Figueiredo P M,Vital J C.Low Kickback Noise Techniques for CMOS Latched Comparators[C]//International Symposium on Cir⁃cuits and Systems,2004(1):537-540.

[9]Le H P,Zayegh A,Singh J.Performance Analysis of Optimized CMOS Comparator[J].Electronics Letters,May 2003,39:833-835.

[10]Gray P R,Hurst P J,Lewis S H.Analysis and Design of Analog In⁃tegrated Circuits[M].John Wiley and Son Iuc,USA,2009,5th editon.

[11]Moghaddam M,Ghaznavi M B.Ghoushchi.A New Low Power De⁃lay Product,Low-Area,Parallel Prefix Adder With Reduction of Graph Energy[C]//19th Iranian Conference on Electrical Engi⁃neering,May 2011:1-6.

[12]Chuang P,Li D,Sachdev M.A Low-Power High-Performance Sin⁃gle-Cycle Tree-Based 64 Bit Binary Comparator[J].IEEE Trans⁃actions on Circuits and Systems II:Express Briefs,2012,59(2):108-112.

任志德(1987-),男,汉族,辽宁省铁岭市,北京工业大学硕士研究生,研究方向为模拟集成电路设计,756859945@qq.com;

郭春生(1980-),男,副教授,硕导,于北京工业大学工作,主要从事半导体器件结温实时测量及结温控制、加速寿命试验、失效分析等可靠性研究,10461935@qq.com。