基于Matlab/Simulink的数字电路仿真

(玉溪师范学院 信息技术工程学院,云南 玉溪 653100)

数字电路是数字电子技术课程的一个重要内容.在以往的教学中,对于所设计数字电路的正确性和有效性的验证,是通过学生使用实验箱搭建电路来完成的,实验过程不仅费时费力,而且受实验条件的影响,很难达到预期效果.而运用计算机仿真软件进行验证是一种新的实验途径,它不需要实验设备和元器件,只要搭建电路模型进行仿真即可完成,在实验效率和准确程度上均有很大提高.MATLAB具有强大的图形处理、符号运算和数值计算功能,其中的动态仿真工具箱Simulink是从底层开发的一个完整的仿真环境和图形界面.运用Simulink用户可以完成面向框图系统仿真的全过程,直观和准确地达到仿真目标.本文中,笔者以组合逻辑电路和时序逻辑电路为例,介绍Simulink在数字电路仿真中的应用.

1 简单组合逻辑电路的仿真

在数字电路中,全加器是实现两个一位二进制数及低位来的进位数相加,求得和数及向高位进位的逻辑电路,将多个一位全加器进行级联,就可实现多位二进制数的相加.

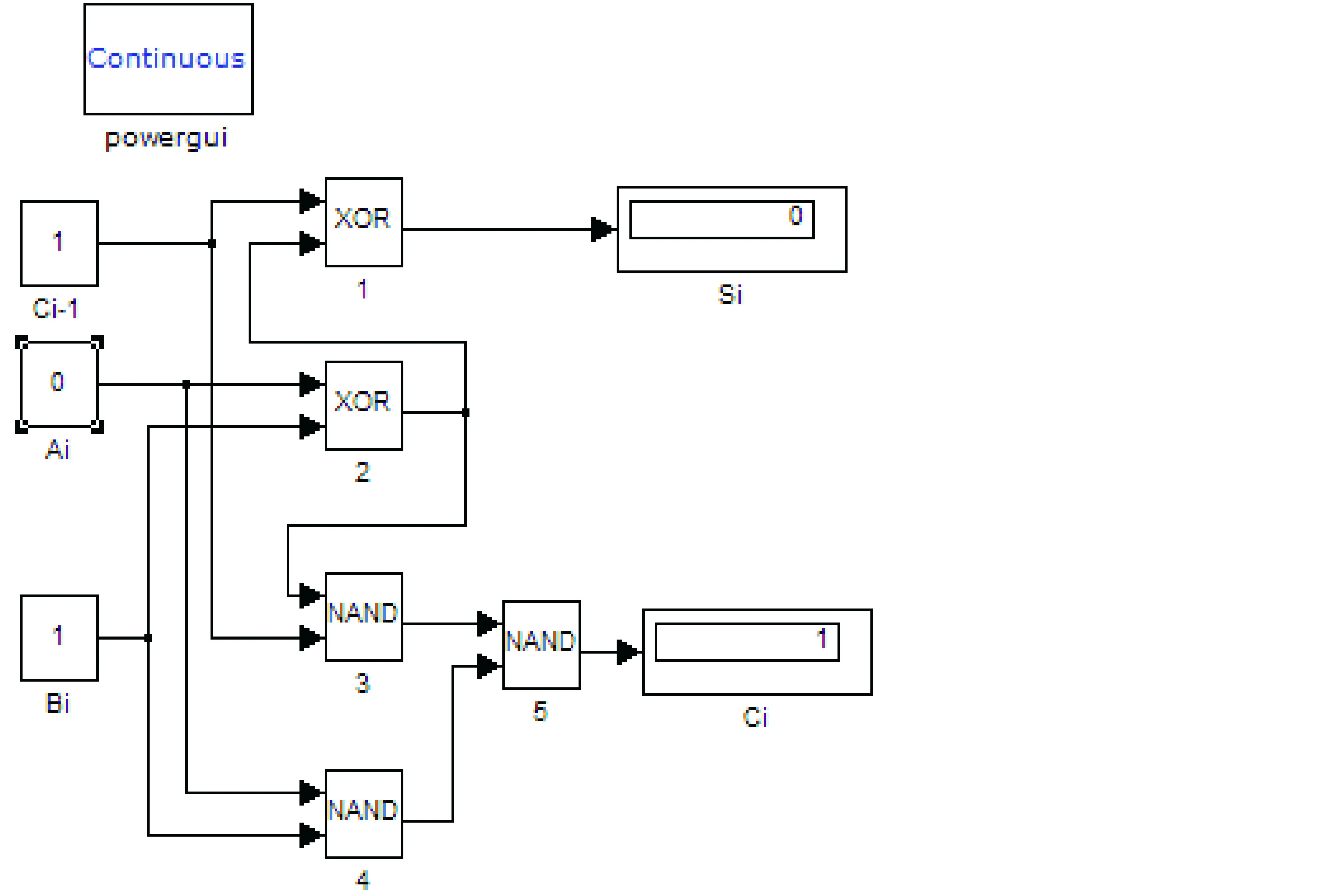

图1 全加器仿真模型及验证结果

表1全加器真值表

Ci-1AiBiSiCi0000000110010100110110010101011100111111

表1为一位全加器的真值表,其中Ai为被加数,Bi为加数,Ci-1为相邻低位来的进位,Si为输出本位和,Ci为向高位进位.化简真值表可得全加器的表达式为:Si=Ai⨁Bi⨁Ci,Ci=AiBi+Ci-1(Ai⨁Bi).根据逻辑表达式,利用Simulink的Logic and Bit Operations子库中的Logic Operator模块[1]和其他相关模块可搭建全加器的仿真电路模型如图1所示,根据表1分别设置Ci-1,Ai,Bi的值为1、0、1,运行后2个Display模块所显示Si、Ci的值为0、1,与真值表一致,说明搭建的仿真电路模型是正确可行的.

2 复杂组合逻辑电路的仿真

两位二进制乘法器可实现两个两位二进制数的相乘,输出的乘积为一个四位二进制数,设A1、A2、B1、B2分别为两个乘数的高位和低位,乘积为Y4、Y3、Y2、Y1,其真值表如表2所示.

表2 两位二进制乘法器真值表

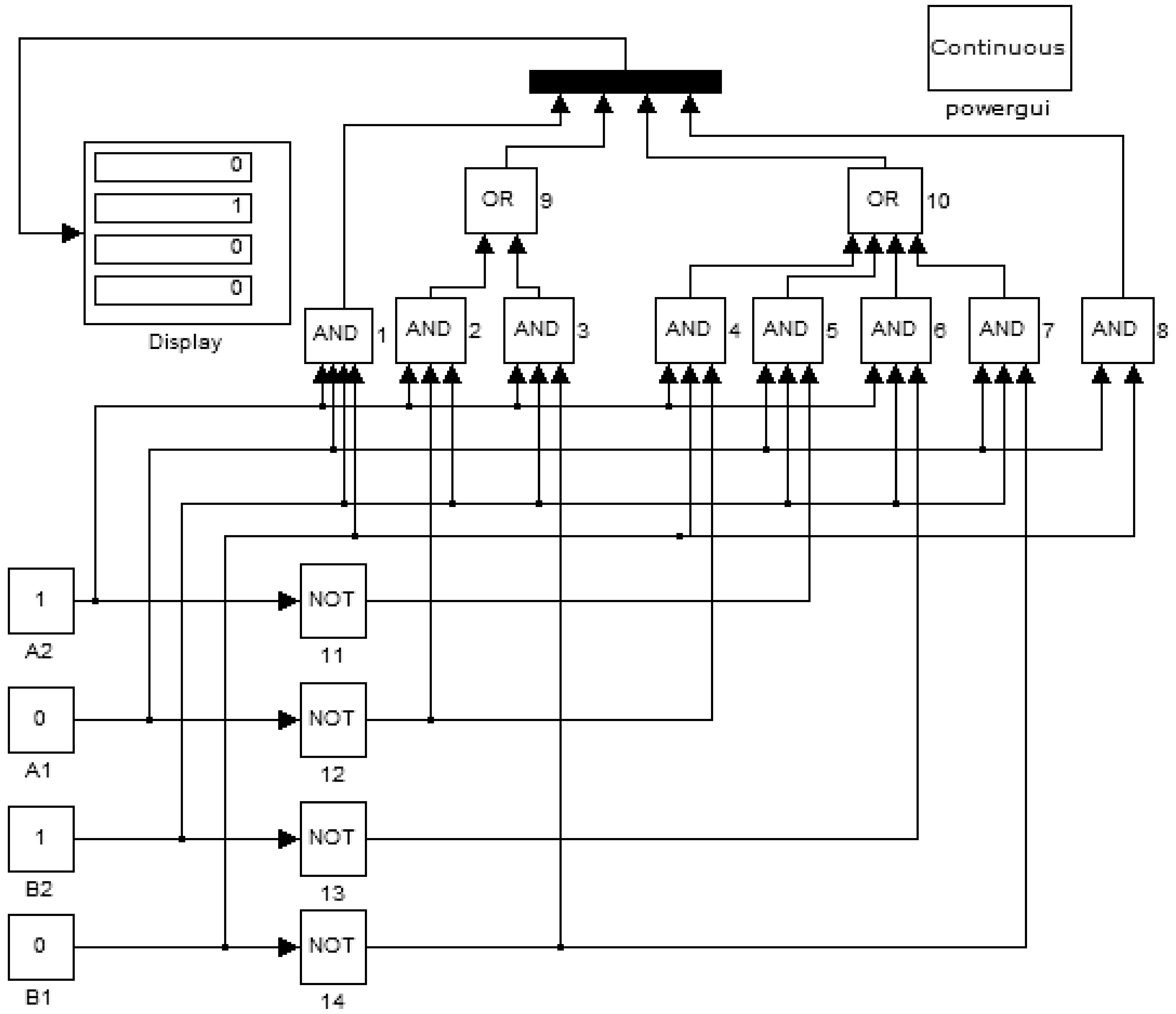

图2 两位二进制乘法器仿真电路模型

根据其真值表可得到化简后的逻辑表达式为:

利用Simulink搭建乘法器的电路模型如图2所示.根据表2设置A1A2B1B2为1010,运行后,Display模块显示0100,仿真结果与真值表一致.

由于两位二进制乘法器电路比较复杂,用实验箱搭建实际电路来验证其设计的正确性,往往很难达到预期结果,而使用Simulink,只要正确搭建电路模型,便可快速地完成验证.

3 时序逻辑电路的仿真

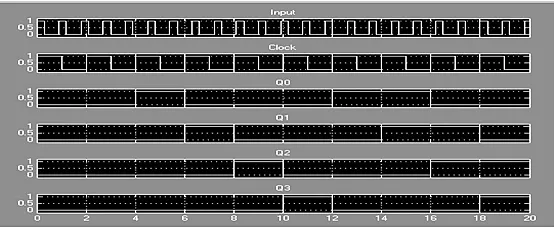

具有移位功能的寄存器称为移位寄存器[2],属于时序逻辑电路.移位寄存器除了可以寄存数据外,还可以在时钟脉冲控制下将所存数据向左或向右移位.在移位寄存器中,输入信号输入到第一个触发器的输入端,前一个触发器的输出作为下一个触发器的输入,所有触发器使用同一个时钟脉冲,信号每经过一个触发器,就被缓存一次.但实际上,信号通过触发器是有时延的,当时钟脉冲的第一个上升沿到来时,信号就被第一个触发器读入并送到其输出端,但此时第二个触发器还不能读入这个信号.因为当该信号到达第一个触发器的输出端时,时钟脉冲的上升沿已经结束,因此只有等到下一个上升沿到来时,第二个触发器才能读入这个信号.这样,信号就在每个触发器的输出端保持一个时钟周期,且每个触发器的输出端信号依次延迟一个时钟周期,从而实现信号的移位.采用D触发器设计一个4位移位寄存器,并使用Simulink搭建仿真电路模型如图3所示,图4是仿真运行后示波器的输出结果.从仿真输出波形可以看出,只有在时钟信号的上升沿时,各个触发器的输出端Q0、Q1、Q2、Q3才会发生变化,且四个触发器的输出依次延迟一个时钟周期.

图3 4位移位寄存器仿真电路模型

图4 4位移位寄存器输出波形

[1]霍加﹒托和塔森.基于MATLAB的数字电路建模与仿真[J].伊犁师范学院学报:自然科学版,2010(1):49-52.

[2]侯建军.数字电子技术基础:第2版[M].北京:高等教育出版社,2007:36-59.