一种PCIe总线MAC模块的设计与验证

王 澧,王 蕾,张 玲(中国电子科技集团公司第58研究所,江苏 无锡 214035)

一种PCIe总线MAC模块的设计与验证

王 澧,王 蕾,张 玲

(中国电子科技集团公司第58研究所,江苏 无锡 214035)

摘 要:根据PCI Express 2.0协议,介绍了PCI Express总线的基本概念,并着重对物理层的基本功能以及内部构成进行了详细说明。在此基础上,采用自顶向下的设计方法,完成了物理层中关键的MAC子层部分的电路设计。另外还搭建了一套验证平台,可自动生成数据包并进行比对,完成了模块的功能验证。最后使用FPGA进行验证,PCIe接口可以正常工作,设计达到了预期的目标。目前用户时钟已稳定工作在250 MHz,可以满足大部分系统数据处理的需求。

关键词:PCIe总线;MAC;FPGA

1 引言

总线技术是系统设计中的关键技术,其性能的优劣直接影响到系统性能。随着处理器和外部接口的不断提速,迫切需要速度更快、带宽更大的总线。但是,随着频率的提高,传统的并行总线由于结构的局限,信号间的相互干扰日趋严重,速度已达到瓶颈,无法满足高速数据传输的要求,面临淘汰的境地。而高速串行总线凭借速度快、抗干扰能力强、发展潜力大的优势,短短数年间几乎全盘取代了传统的并行技术,成为高速互连领域的绝对主导。高速串行总线摒弃了传统的单端信号传输方式,使用了差分信号(differential signal)传输技术。与以往的并行信号相比,差分信号可以使用更高的时钟频率、更少的信号线,达到之前需要大量并行数据线才能实现的总线带宽,并能克服天线效应对传输线路的干扰以及线路之间的串扰。目前典型的高速串行总线有USB、SATA、Rapid I/O、Ethernet和PCI Express等。

PCI Express(Peripheral Component Interconnect Express)全称为外围组件互联扩展,简称PCIe,是由PCI SIG(PCI Special Interest Group)提出的第三代IO互连技术(3GIO),在保留PCI总线特性的基础上,更注重数据通信的高实时性和高可靠性,已经取代PCI在芯片到芯片级的应用或电路板传输系统中使用。

2 PCIe简介

PCIe作为新兴的高性能总线,技术优势明显:可以向上兼容PCI规范;通过数据包(packets)在两个设备间进行点对点的数据传输;每个通路使用2对低压差分信号进行传输,可同时进行发送和接收数据;支持热插拔和热交换;在2.0规范中单通路带宽达到5 GB/s;通过流量控制和信用管理模块有效利用总线资源;通过循环冗余校验(ECRC)保证数据的可靠性。

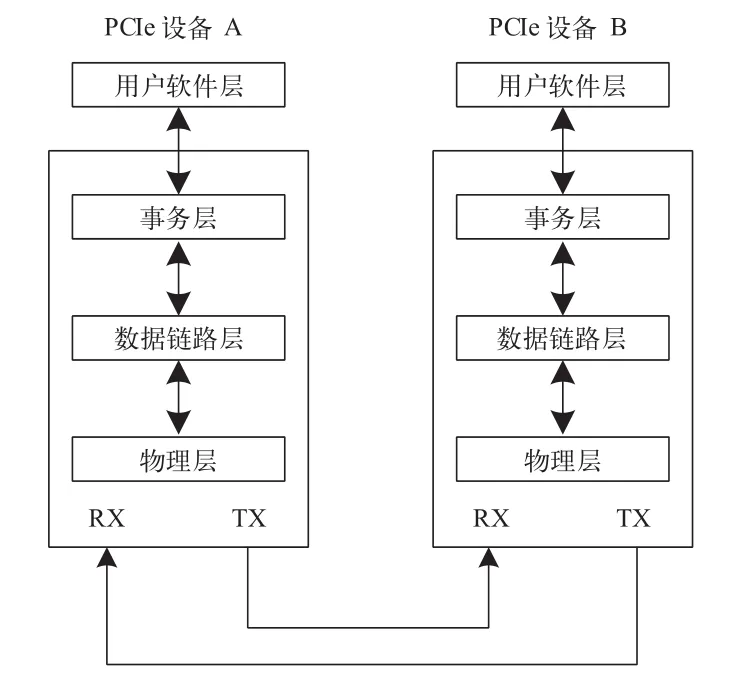

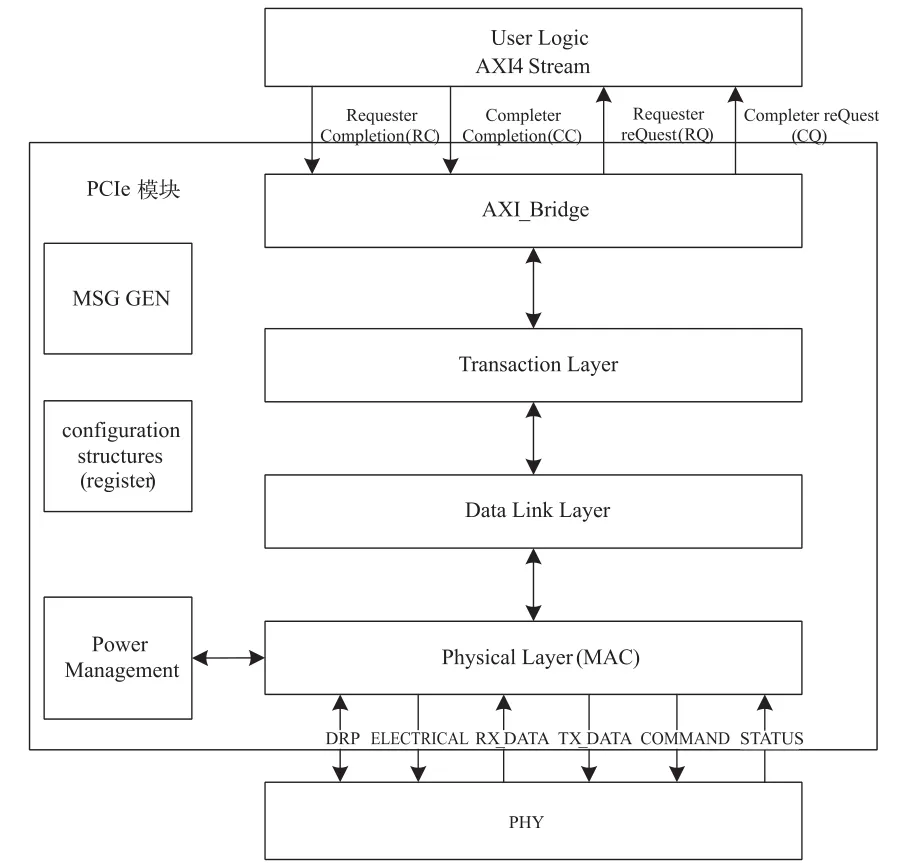

图1 PCIe总线层次结构

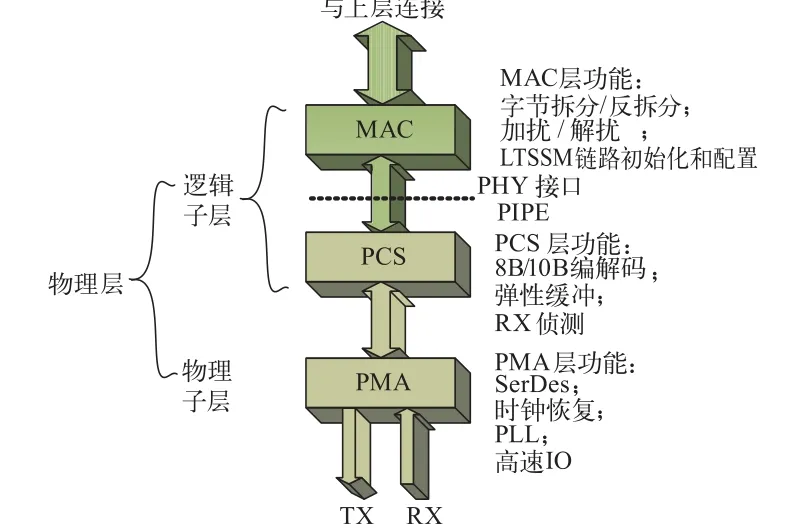

PCIe总线规范借鉴了OSI(Open System Interconnection)网络模型,采用分层传输,各层次具有独立功能又能紧密联系。如图1所示,数据传输从上至下需要经过事务层(Transaction Layer)、数据链路层(Data Link Layer)和物理层(Physical Layer)。如图2所示,物理层可细分为MAC(Media Access Control Layer)、PCS(Physical Coding Sub-Layer)和PMA(Physical Media Attachment Layer)子层。其中MAC子层主要对数据进行逻辑处理。PCS和PMA子层包含高速模拟收发模块,需要使用全定制方式设计,因此一般用单独的芯片或模块实现。它们之间的接口信号遵循物理层接口规范PIPE(Physical Interface for PCI Express)。

图2 物理层划分

物理层作为PCIe总线的最底层,是整个体系中真正的核心。MAC层是数据链路层与物理层的接口,将上层的指令转化为相关控制信号,通过PIPE接口传送到PCS层,是控制物理层的关键模块,本文将对其进行重点描述。

3 设计

本文设计的PCIe端点(Endpoint)模块支持PCIe 2.0协议,采用全正向设计,使用Verilog HDL语言,使用SMIC 40 nm制造工艺,将以硬核的方式存在。其中的PHY层采用Xilinx公司的Virtex-6 GTX。整体架构如图3所示。

图3 PCIe整体架构框图

3.1概述

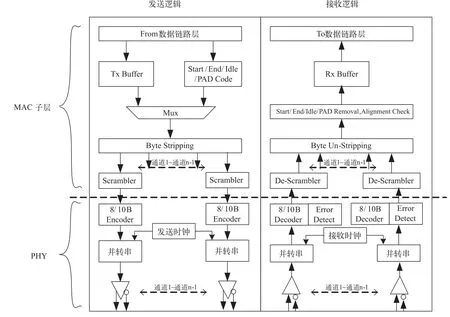

MAC子层位于PCS层和数据链路层之间,复位后LTSSM(Link Training and Status State Machine)状态机对链路进行初始化和管理,接着通过PIPE接口收发数据、加扰/解扰、通道翻转、对数据链路层收发数据包等。整个模块由发送逻辑和接收逻辑组成,具体功能如图4所示。

如图4所示,MAC层发送数据的过程如下:

(1)从数据链路层获得数据包TLP或DLLP,放入发送缓存Tx Buffer中。

(2)将这些数据包加入物理层的前缀和后缀,和物理层的PLP一起通过多路选择器Mux,进入字节分配Byte Stripping部件。

(3)整个PCIe链路可能由多个Lane组成,Byte Stripping部件可以把数据分配到不同Lane中。

(4)数据进入到各自Lane的加扰Scrambler部件,加扰后进行8/10b编码,最后经过并转串发送到PCIe链路中。

MAC层的接收过程是发送的逆过程。图4中虚线以下部分由PHY部分来完成。

图4 物理层逻辑细节

3.2总体设计

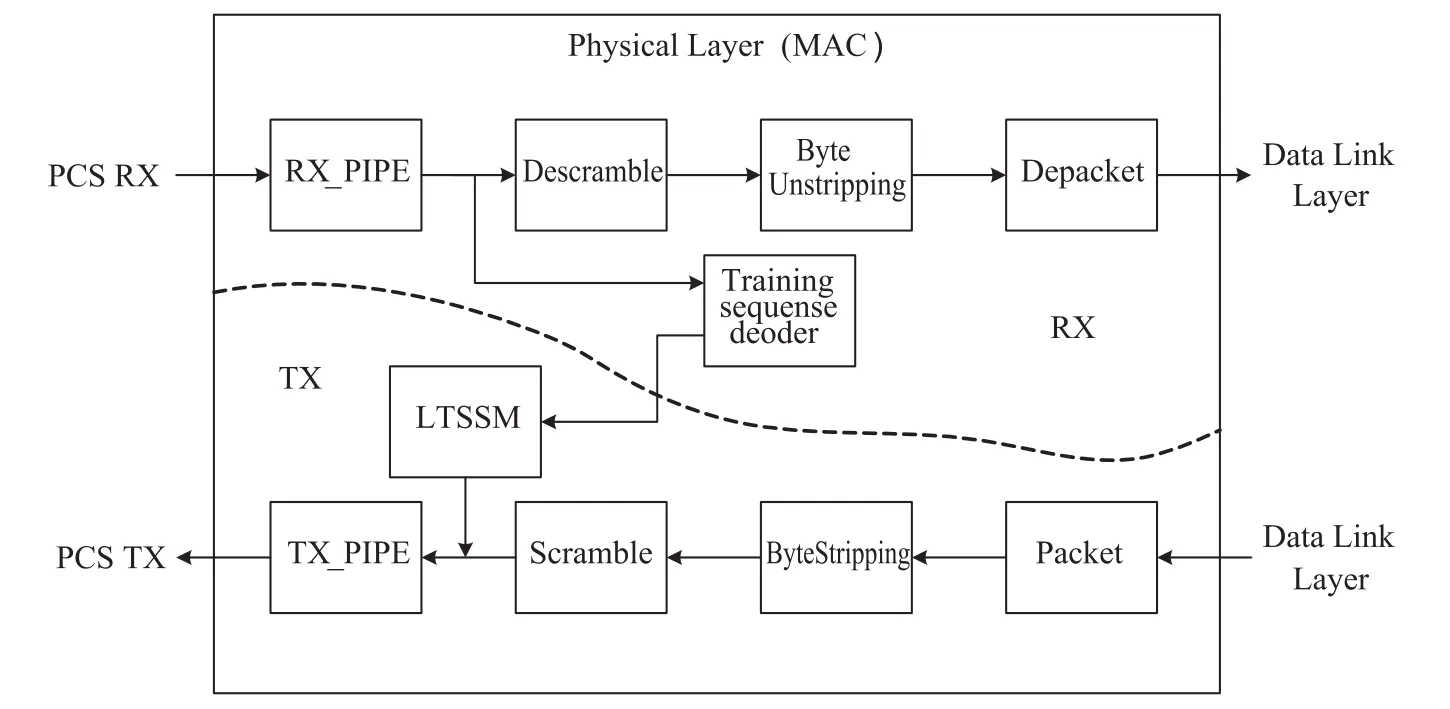

按照上述功能划分,MAC层的整体框图如图5所示。

主要包括以下模块。

图5 MAC模块框图

RX_PIPE模块:接收PIPE接口过来的数据,并对接收的数据进行分类,将收到的链路训练字符序列发送给Training Sequence Decoder模块,TLP和DLLP数据则发送给Descramble模块;

Scramble/Descramble模块:对数据进行加扰/解扰处理;

Training Sequence Decoder模块:对收到的链路训练序列进行识别,并把识别的链路训练信息发送给LTSSM模块;

Byte Stripping/Byte Un-Stripping:根据链路训练的结果,对Lane数据的顺序进行调整;

Packet/Un-Packet:把数据加入物理层的前缀和后缀后打包,或将数据拆包;

LTSSM:主要实现链路训练、重训练、低功耗状态控制等功能;

TX_PIPE模块:主要完成LTSSM和Scramble数据的选择,再发送至PIPE接口。

3.3LTSSM设计

PCIe初始化的流程比较复杂,整个链路训练完全由硬件自动完成,与软件无关,训练成功结束后才能进行数据交换。训练主要包括初始化端口配置信息、链路状态,了解对端的拓扑结构、确定数据传输速率、相位补偿等。

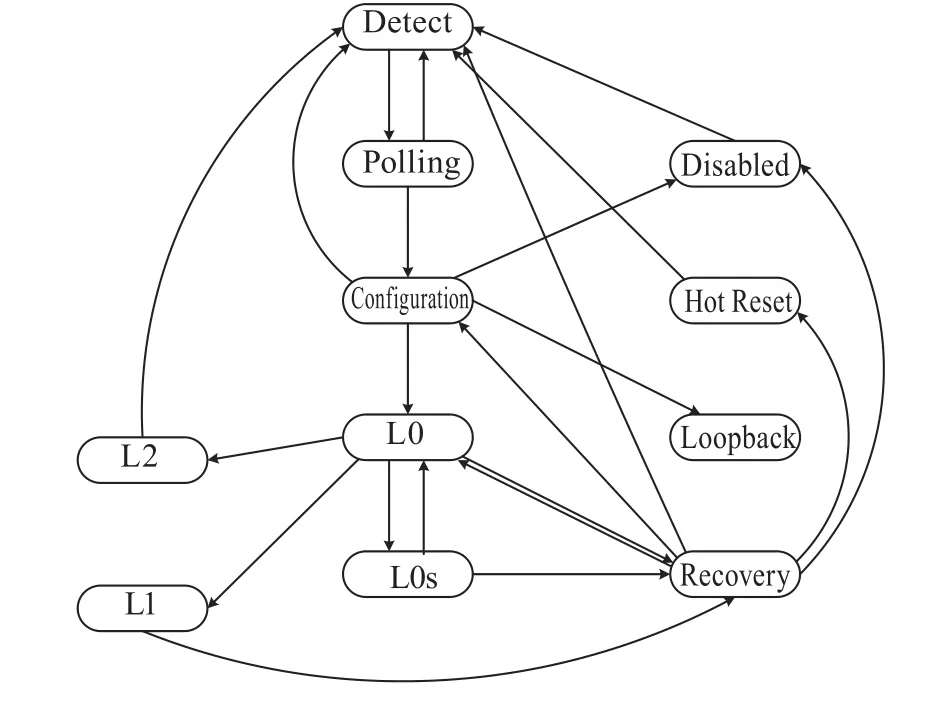

负责链路训练的是状态机LTSSM,共由“Detect”、“Polling”、“Configuration”、“L0”、“L0s”、“L1”、“L2”、“Recovery”、“Loopback”、“Hot Reset”、“Disable”11个状态组成。其中每个状态下还有数个子状态,迁移模型较复杂。“Detect”、“Polling”、“Confi guration”属于链路训练状态,完成远端设备检测、比特及符号锁定、确认通道极性和数据速率、配置链路宽度和链路号以及通道反转和极性反转等功能。“L0”、“L0s”、“L1”、“L2”是关于电源管理的链路状态,提供了几种低功耗模式。“Recovery”是链路的重训练状态,更改链路配置或故障时进入该状态。“Loopback”是一种调试模式,并不用于正常运行。“Disable”状态下将禁止PCIe链路。图6显示了状态机所有关系以及状态间的转移。

图6 LTSSM状态机

状态机的部分代码如下:

always @(posedge core_clk or negedge core_rst_n) begin

if(~core_rst_n)

lts_state <= DETECT_QUIET; else

lts_state <= lts_next_state;

end

always @ (*)

begin

if(phy_lane_loop_back)

lts_next_state = DETECT_QUIET; else begin

case (lts_state) DETECT_QUIET: begin

if((cur_link_spd == 1'b1) | phy_lane_loop_back)

else if((and_rx_lane_elceidle == 1'b0) & (wait_timer > 512)) lts_next_state = DETECT_ACTIVE; else if(wait_timer >= 21'h16_E360 ) lts_next_state = DETECT_ACTIVE; else lts_next_state = DETECT_QUIET;

...

3.4加扰模块

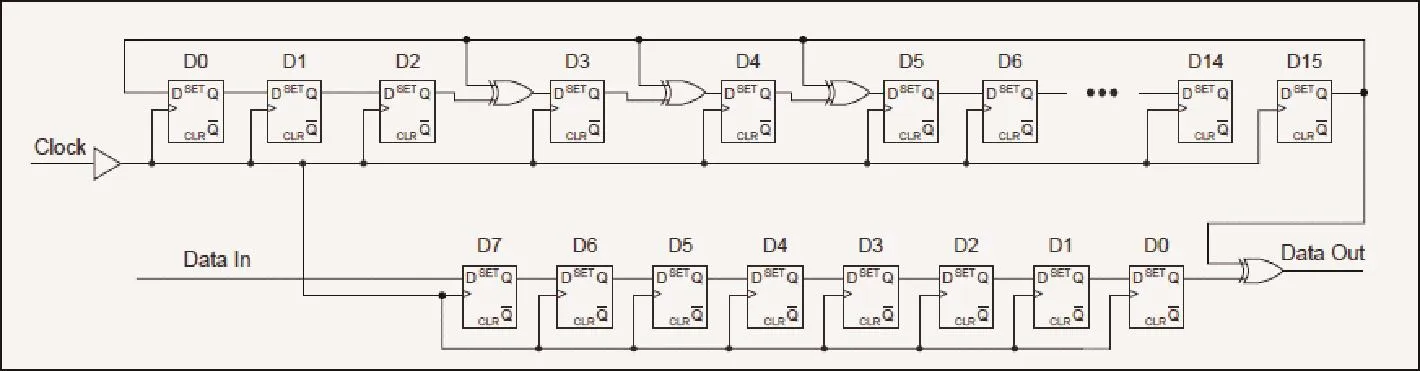

字节拆分后,数据包要进行加扰,接着再发送到通道中。加扰主要是通过减少数据的重复出现达到降低EMI噪声的目的。也就是将数据和一个随机序列进行异或操作成伪随机数,再发送出去。PCIe协议规定的生成随机序列的LFSR的表达式为:

G(X)=X16+X5+X4+X3+1

加扰的规则如下:

(1)收到COM字符时,初始化LFSR;

(2)除了SKP字符以外,每收到一个字符,LFSR的值移位8次;

(3)除了TS1、TS2、EIEOS、Compliance Pattern以外的数据字符都需要进行加扰;

随着时间的演变,使用广泛的英语语言形式出现了各种区域性变体。英语方言也出现了具有区域性的语词(语音和词汇上的特点)和语法。一种方言的某一特征所占据的区域可能不同于同一方言的另一特征所占据的范围,但各种特征的区域大体上具有某种一致性,从而使我们有可能谈论一种方言的区域界限[3]。这是一条宽度不等的地域带,在这里可能有两种方言的混合形式。

(4)所有的控制字都不进行加扰;(5)LRSR的初始值为0xFFFF;

(6)Scramble在Detect状态时使能,并且只允许在Confi guration状态的结束阶段被禁止;(7)Loopback状态时,Scramble无效;LFSR的电路图如图7所示。

先对输入数据的低8位进行加扰,再对高8位进行操作,其中低8位加扰的部分代码如下所示:if (dsc_data_vld == 1’b1) begin

if((datak[0] == 1’b1) & (data[7:0] == `COM)) lfsr_tmpa = 16’hffff;

else if((datak[0] == 1’b1) & (data[7:0] == `SKP)) lfsr_tmpa = lfsr; else begin

lfsr_tmpa[0] = lfsr[8];

lfsr_tmpa[1] = lfsr[9];

lfsr_tmpa[2] = lfsr[10];

lfsr_tmpa[3] = lfsr[11] ^ lfsr[8];

lfsr_tmpa[ 4] = lfsr[12] ^ lfsr[ 9] ^ lfsr[8];lfsr_tmpa[ 5] = lfsr[13] ^ lfsr[10] ^ lfsr[9] ^ lfsr[8]; lfsr_tmpa[6] = lfsr[14] ^ lfsr[11] ^ lfsr[10] ^ lfsr[9]; lfsr_tmpa[ 7] = lfsr[15] ^ lfsr[12] ^ lfsr[11] ^ lfsr[10]; lfsr_tmpa[ 8] = lfsr[ 0] ^ lfsr[13] ^ lfsr[12] ^ lfsr[11]; lfsr_tmpa[ 9] = lfsr[ 1] ^ lfsr[14] ^ lfsr[13] ^ lfsr[12]; lfsr_tmpa[10] = lfsr[ 2] ^ lfsr[15] ^ lfsr[14] ^ lfsr[13]; lfsr_tmpa[11] = lfsr[ 3] ^ lfsr[15] ^ lfsr[14];

图7 LFSR实现图

lfsr_tmpa[12] = lfsr[ 4] ^ lfsr[15]; lfsr_tmpa[13] = lfsr[ 5];

lfsr_tmpa[14] = lfsr[ 6];

lfsr_tmpa[15] = lfsr[ 7];

end

end

else

lfsr_tmpa = lfsr; ...

4 仿真验证

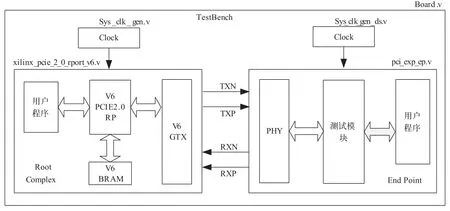

在完成代码编写后,使用Synopsys公司的仿真验证工具VCS进行功能测试,主要是验证模块是否能遵循协议,正确地发送用户逻辑产生的数据包以及正确接收链路上的数据包。图8是验证环境的组成,分为主机和从机两个部分,互相进行数据收发。其中从机是要测试的模块,PHY使用Virtex-6 GTX模型,主机模型使用Virtex-6的PCIe模型。

在两端的用户程序部分,分别封装了一系列task产生各种报文,供TC调用。

图8 验证环境框图

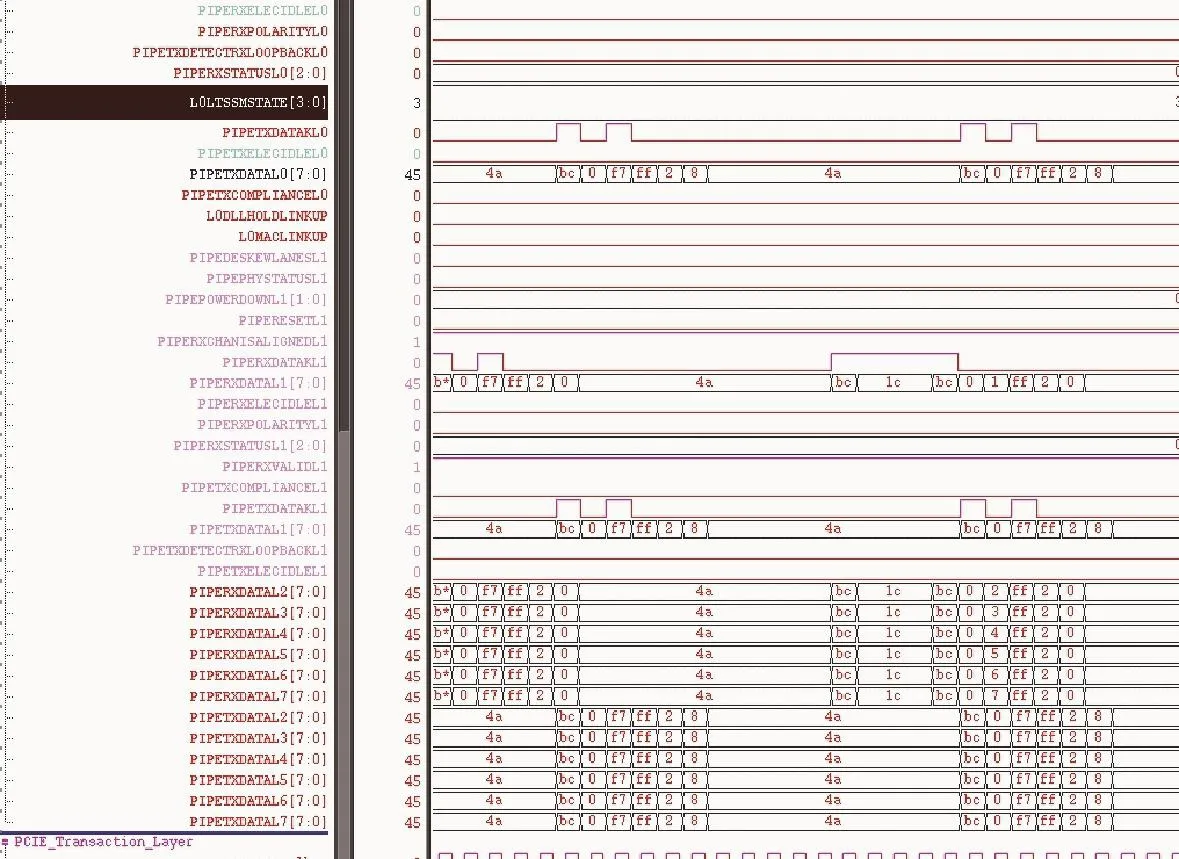

4.1链路初始化

首先要对系统复位后链路初始化进行验证,LTSSM进入L0状态后才能进入正常工作。PCIe设备的物理层复位后,LTSSM状态机沿着“Detect”→“Polling”→“Confi guration”→“L0”的顺序进入正常工作状态“L0”。

如图9所示,RX端接收到TS1序列,其中Link Number为0,Lane Number为0~7,后经过TS2确认,再向对端发送至少16个IDLE数据,RX接收到后,置LinkUp状态位为1,PCIe数据链路层将从DL_Inactive迁移到DL_Init状态,进入L0正常工作状态。

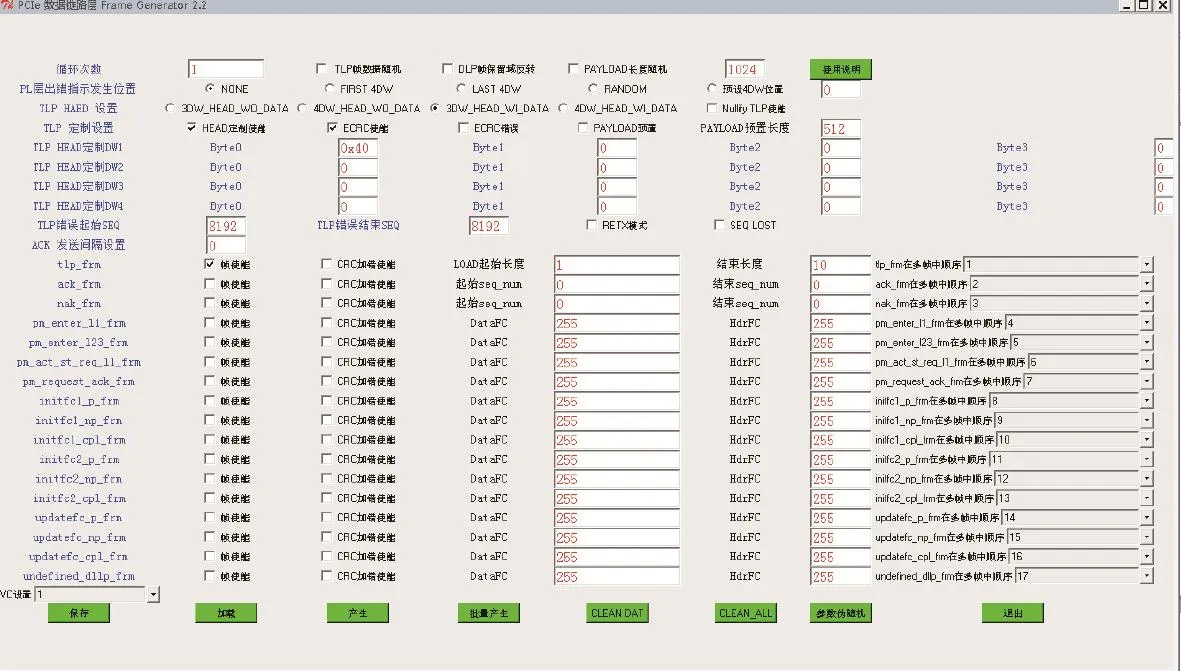

4.2数据传输

进入正常工作状态后,开始进行数据收发测试。如图10所示,通过软件构造出激励源,在用户接口端产生各种TLP报文。其中TLP 报文头可以定制,报文长度可以定制,可以组合成各种报文类型,达到较高的测试覆盖率。

图9 LTSSM初始化

图10 TLP报文生成界面

5 结束语

本文介绍了一种PCIe端点模块的设计,重点叙述了MAC子层的设计实现,通过功能仿真以及FPGA验证,模块可以正常工作,输入时钟250 MHz,达到了预期的设计目标。下一步将使用SMIC 40 nm工艺进行流片验证。

参考文献:

[1] 王齐. PCI Express体系结构导读[M]. 北京:机械工业出版社,2010.

[2] 张锐,曹彦荣. 基于FPGA的PCIE总线接口设计[J]. 硅谷,2014(7).

Design and Verifi cation of MAC Layer Based on PCIe Bus

WANG Li, WANG Lei, ZHANG Ling

(China Electronic Technology Group Corporation No.58 Research Institute, Wuxi 214035, China)

Abstract:The paper is according to the PCI Express protocol, introduces the basic concepts of PCI Express bus and focuses on the basic function and structure of physical layer.On this basis, using TOP-DOWN design method,fi nish the circuit design of the MAC sub-layer,key part of physical layer.Additionally, we have build a verify platform, can automatically generate data packets and compare, fi nish the function verifi cation.The circuit has passed FPGA verifi cation after synthesis, PCIe interface can work normally. The design achieves the expected goal.Now theuser clock can work well at 250 MHz,can meet the most system’s data process requirements.

Keywords:PCIe bus; MAC; FPGA

中图分类号:TN402

文献标识码:A

文章编号:1681-1070(2015)10-0020-06

收稿日期:2015-6-25

作者简介:

王 澧(1982—),男,江苏无锡人,本科,工程师,现在中国电子科技集团第58研究所从事电路设计工作。