一种复杂指令系统译码器设计方法

赵 香

一种复杂指令系统译码器设计方法

赵香

(中国电子科技集团公司第三十八研究所集成电路设计中心,合肥230088)

介绍一种面向处理器复杂指令系统的译码器软件模型设计方法,该设计采用平衡二叉树的数据结构存储译码表,加入指令缓存,提高指令译码速度,详细描述译码器的设计过程。

指令集模拟器;译码器

0 引言

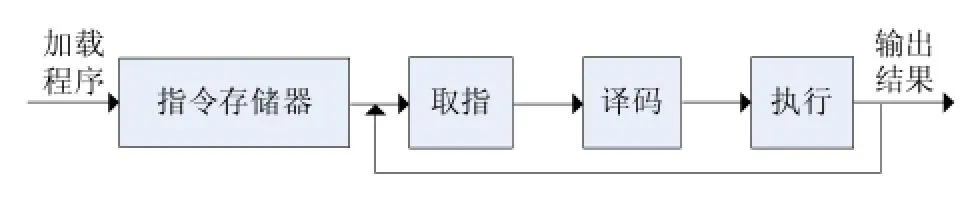

每款处理器都有各自配套的指令系统[1],处理器功能越强大对应的指令系统也越复杂。指令系统的发展是一个从简单到复杂的过程。早期的处理器由于硬件设计成本的原因,其指令系统相对结构简单,所支持的指令也相对较少。后来伴随着超大规模集成电路技术的迅速发展,在设计高性能处理器时,为提升处理器的运行效率,设计师采用的方法是不断地增加可实现复杂功能的指令和多种灵活的编址方式,致使处理器的指令系统变大复杂、庞大,给硬件和软件的译码器设计带来很多困难[2]。译码器[3~4]是指令集模拟器的关键模块(如图1),它是指令运行之前的准备工作,其功能是从一个二进制的机器码中提取出指令运行的信息或相关的程序控制信息。面对复杂指令系统,如何快速译码[4]是本文要解决的问题。

图1 指令集模拟器工作流程

本文所设计的译码器是基于中国第一款自主研发高性能通用DSP“魂芯一号”[5],该处理器一款32位浮点DSP,同时兼容16位和32位定点数据格式,采用VLIW架构,具有强大的并行处理能力,能较好地满足高速实时信号处理的应用要求。其核内部包含4个基本执行宏,每个执行宏由8个算术逻辑单元(ALU)、4个乘法器(MUL)、2个移位器(SHF)、1个超算器(SPU)以及1个通用寄存组组成。

1 指令系统

BWDSP100提供了十分丰富的指令系统,从功能上可以分为算术指令、逻辑指令、程序控制指令等3大类,共200多条基本指令,由于操作数的寻址方式不同,基于这些基本指令可以派生出更多的指令。BWDSP100指令系统的指令按指令字长度分为单字指令和双字指令,其单字指令字长32位,双字指令字长64位,大多算术类、逻辑运算类指令为单字指令,少量算术类和控制类指令为双字指令。

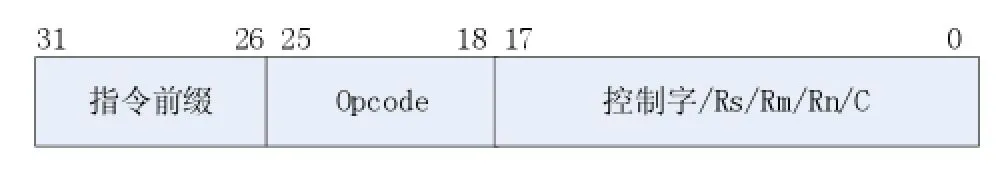

指令字格式如图2、图3所示,对各字段说明如下:

指令前缀:表示单/双字信息和运算宏信息,即该指令是单字指令还是双字指令,及该指令是在哪个宏上运算;

Opcode:是该指令的唯一标识,在译码器设计中,其作为译码表中的索引;

指令后缀:表示控制字、寻址方式、立即数等,例如该指令是有符号运算还是无符号运算,操作数是从何处读取,可以是立即数,也可以从通用寄存器读取。

图2 单字指令结构

图3 双字指令结构

2 译码器设计

一般译码器的设计采用if-else语句的多层嵌套结构或者switch-case多分支选择语句结构等,其特点是运行方向是向前的,结果只能是众多分支当中的1支。switch-case结构是对if-else结构的一个优化,但效率并无明显提高。查找每条指令都需要经过多次条件比较,若按顺序排列指令,排在后面的指令搜索的时间明显长于排在前面的指令。

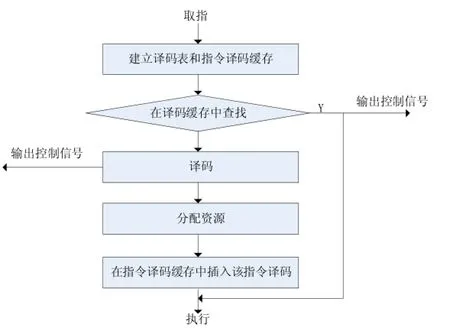

为提高芯片的运行效率,结合处理器使用Cache的设计思想[4],在设计时采用译码缓存DecodeCache策略和平衡二叉树[6]的结构构件译码表,对同一指令减少译码次数,缩短指令搜索时间,提高译码效率。译码器的设计流程图如图4所示。

(1)建立译码表,为提高指令的搜索速度,减少不同指令之间的搜索时间差距,采用平衡二叉树的数据结构,以opcode作为索引建立译码表,每个opcode对应一个译码的函数接口。整理指令系统,将所有指令按照指令字格式进行分类,对指令字格式相同的指令可以使用同一函数接口。

(2)建立译码缓存DecodeCache,大小定义为1024,可根据实际需要调整。实现时译码缓存DecodeCache可以定义为一组无符号的整型数,其定义如下。

图4 译码器流程图

typedef struct

{

unsigned int UnitsUseCalc;//运算宏信息

unsigned int ALUNum;//ALUNum中的每一位表示对应ALU的索引

unsigned int MULNum;//MULNum中的每一位表示对应乘法器的索引

unsigned int SHFNum;//SHFNum中的每一位表示对应移位器的索引

unsigned int SPUNum;//SPUNum中的每一位表示对应特定运算单元的索引

}INT_RES_USED;

typedef struct

{

unsigned long DecodeInfo[MAX_PARA_NUM];//用于存放通用寄存器索引、立即数等

unsigned long Opcode;

unsigned long Inst0;//单字指令字或双字指令的第一个指令字

unsigned long Inst1;//双字指令的第二个指令字INT_RES_USED InstReSource;//指令所占用的资源信息}INST_DEC_INFO;

INST_DEC_INFO DecodeCache[1024];

(3)在DecodeCache中找寻是否已经对该指令字译码,如存在,则直接进入下一级模块取操作数执行指令,否则对指令字进行译码。

(4)对指令进行译码,对于运算类指令和逻辑类指令,从32位/64位指令字中获取运算宏信息、寻址方式(立即数或者通用寄存器索引);对于程序控制类指令,产生相关控制信号。

(5)分配资源,对运算类指令和逻辑类指令分配运算部件,分配的结果保存于InstReSource数据项中。运算部件分配的基本原则是:首先,若指令需要指定的运算部件,则优先分配;其次,其余的运算部件,按顺序由低到高分配。

(6)将译码结果存入DecodeCache中,准备读取操作数执行指令。译码缓存DecodeCache的维护可以采用LRU算法对缓存中各条记录进行替换。

3 实验结果分析

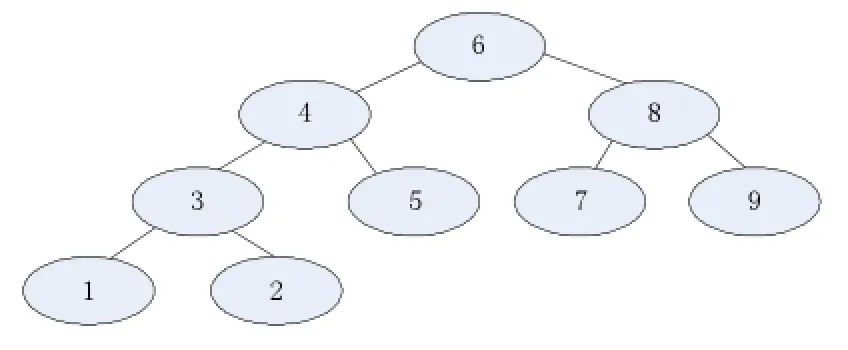

随意选取BWDSP100指令系统中9条指令做译码,如表1,具体BWDSP100指令系统可以参照BWDSP100软件用户手册[5]。在构建译码表时按顺序构建一般的表,那么搜索到最后一条Sin指令需要查找9次。按照本文中设计方法构建译码表,如图5,该表的查找深度是4,查找Sin指令只需要3次,若查找1000条指令最差的查找次数是10。

4 结语

本文针对复杂指令系统的译码器设计提出了一种设计方法,详细讲述了译码器设计流程,给出了主要的数据结构,适用于各种处理器的指令系统,有效提高了指令译码的速度,进而提升了指令集模拟器的工作效率。鉴于指令集模拟器的快速建模技术在DSP开发中的重要性,若能将译码器设计为一个可重用的构件,直接应用于指令集模拟器的快速建模,那么可以为设计者减少很多工作量,因此进一步对译码器的可复用性研究具有重要的意义。

表1 BWDSP100指令

图5 四层译码表

[1]王元元.基于VLIW的指令格式的研究设计.计算机工程与应用,2003,3(72-74)

[2]沈斌,张多利.周期精确的指令集模拟器的建模与封装方法.中国集成电路,2007,11:60~64

[3]孙立宏.高性能通用DSP译码器设计.中国集成电路,2014,06:(29-31)

[4]Nohl A,Braun G,Schliebusch O,et al.A Universal Technique for Fast and Flexible Instruction Set Architecture Simulation.DAC.2002

[5]中国电子科技集团公司第三十八研究所.BWDSP100软件用户手册[M].合肥,2011:1~20

[6]解晨.AVL树研究与实现.电脑知识与技术,2013,07期(1532~1536)

Instruction Set Simulator(ISS);Decoder

A Design Method of Complex Instruction System Decoder

ZHAO Xiang

(IC Design Center,No.38 Research Institute of CETC,Hefei 230088)

Introduces a design method of complex instruction system decoder.Adopts balanced binary tree to store information in decoder table and use instruction cache for improving decode speed of instruction in the design.Describes the design method of decoder particularly.

1007-1423(2015)12-0080-04

10.3969/j.issn.1007-1423.2015.12.019

赵香(1983-),女,工程师,研究方向为集成电路软件设计

2015-03-10

2015-04-07