高速串行数据发送接收芯片CY7B923/933的原理及应用设计(上)

耿启立

(中国地质装备集团有限公司,北京 100102)

1 概述

HOTLink发送接收芯片CY7B923/933是由CYPRESS半导体公司推出,可用于构建点对点高速串行数据传输链路。CY7B923/933采用单一+5V电源供电(发送芯片CY7B923功耗为350mW,接收芯片CY7B933功耗为650mW),可兼容光纤、IBM ESCON、DVB-ASI及 SMPTE-259M 等多种传输协议,可采用光纤、同轴电缆和双绞线等作为传输介质。标准HOTLink数据传输速率为160~330Mb/s,高速 HOTLink数据传输速率为160~400Mb/s。HOTLink系统连接示意图如图1所示。

图1 HOTLink系统连接示意图

HOTLink串行数据发送过程:八位并行数据或协议信息加载到发送芯片,经过内部编码器编码、内部移位寄存器移位转换成串行数据,串行数据以特定的位流速率、通过差分PECL输出端口发送。

HOTLink串行数据接收过程:接收芯片通过差分输入接口接收串行位流数据,利用内部集成PLL锁相环同步器实现串行位流数据接收同步;接收到的串行位流数据,通过移位寄存器实现反序列化、解码、校验,转换为字节数据,利用字节时钟同步、通过接收芯片内部输出寄存器输出。

2 发送芯片

2.1 封装及引脚

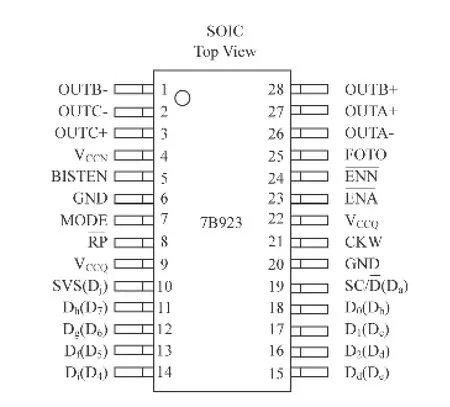

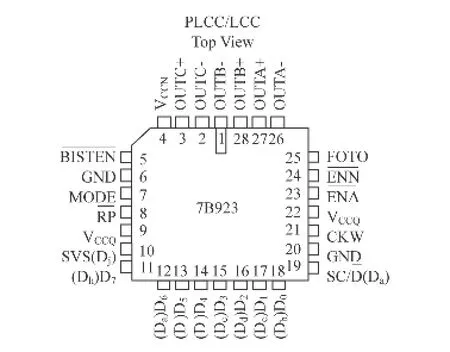

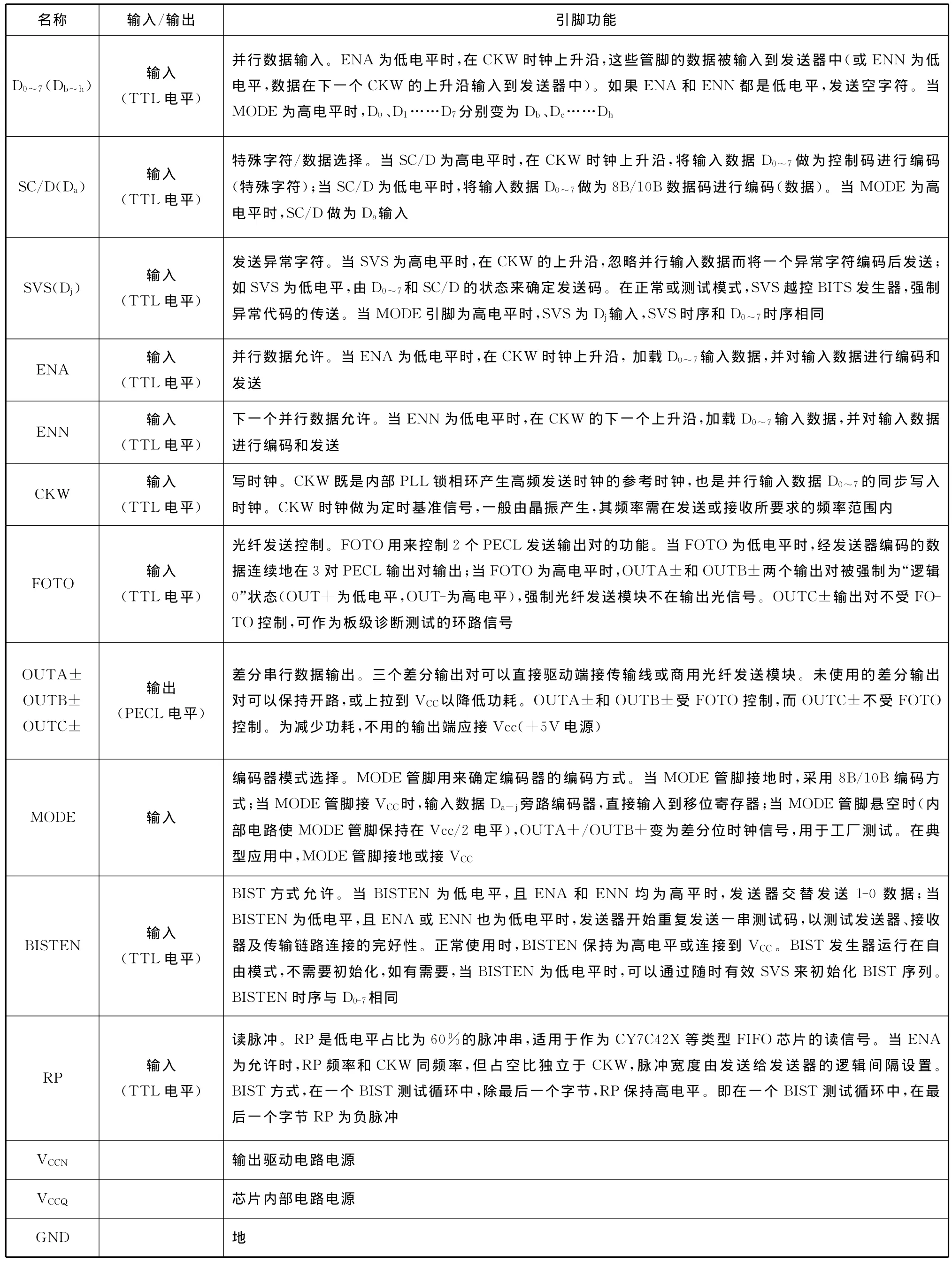

发送芯片CY7B923有28脚SOIC、PLCC和LCC三种封装形式,SOIC封装如图2所示,PLCC/LCC封装如图3所示,引脚功能如表1所示。

图2 CY7B923SOIC封装示意图

图3 CY7B933PLCC/LCC封装示意图

表1 CY7B923引脚功能说明

2.2 芯片构成及功能

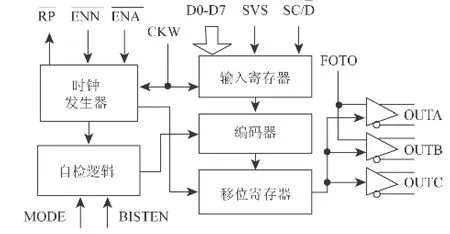

CY7B923发送芯片由时钟发生器、输入寄存器、编码器、移位寄存器、PECL差分输出对和自检逻辑等单元构成,内部功能框图如图4所示,各单元功能详述如下。

图4 芯片内部功能示意图

2.2.1 时钟发生器

时钟发生器为内嵌PLL锁相环,用来产生字节速率参考时钟CKW和10倍于CKW、用来驱动串行移位寄存器的位速率时钟。字节速率时钟CKW的上升沿,D0-7数据输入到输入寄存器。CKW时钟频率应满足HOTLink发送器/接收器的要求。时钟发生器还用来产生输入寄存器和移位寄存器之间传输数据所需的位速率时钟和时序信号。

读脉冲(RP)由PLL乘法器的反馈计数器产生,RP是一个有适当相位和脉冲宽度的字节速率时钟,用于从异步FIFO读取和传输数据,其脉冲宽度独立于CKW,由PLL确定。RP脉冲确保在无外部逻辑的条件下,异步FIFO和发送输入锁存器之间正确的进行数据传输。

2.2.2 输入寄存器

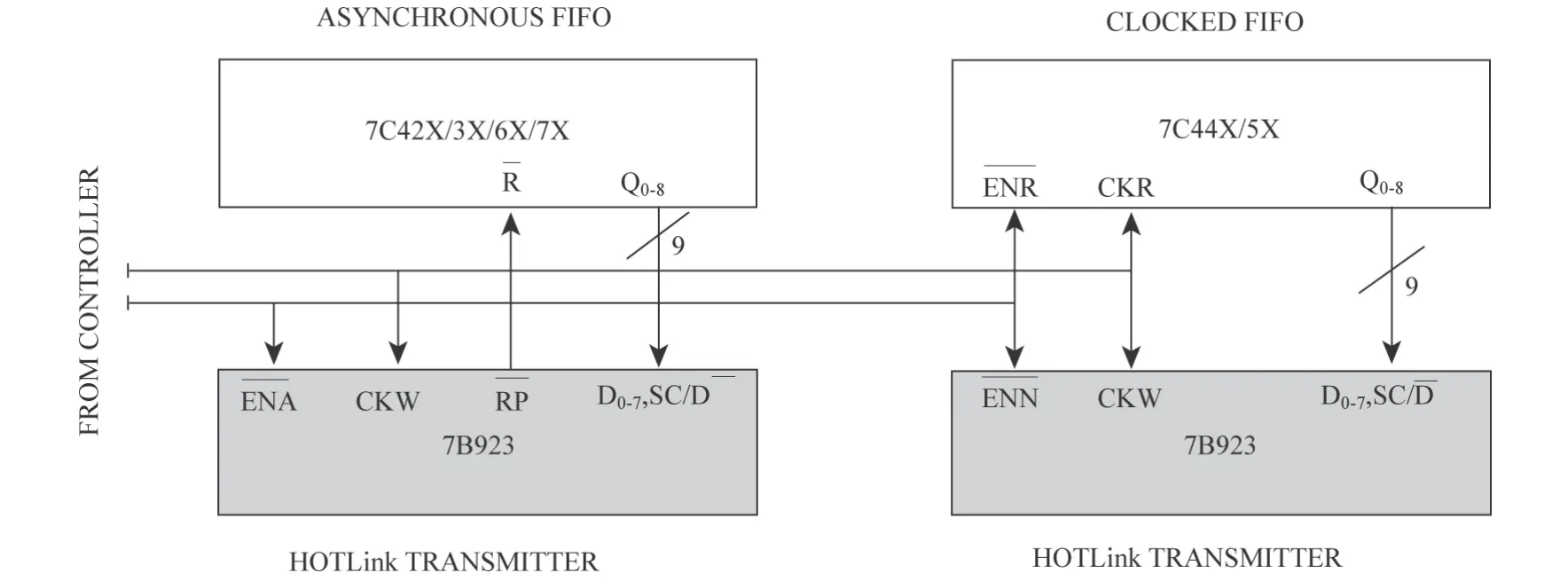

图5 CY7B923与FIFO接口示意图

输入寄存器用来保存HOTLink输入数据,其输入时序和标准FIFO一致,输入寄存器时钟为CKW,装载信 息包括 D0-7、SC/D 和 SVS,ENA 和ENN为输入使能控制。ENA为低电平,CKW上升沿将输入信息加载到输入寄存器;在CKW上升沿,如ENN为低电平,在CKW的下一个上升沿,输入信息加载到输入寄存器;如在CKW上升沿,ENA和ENN都是低电平,发送SYNC同步字符。如图5所示连接ENA和ENN,可以在无需外部逻辑情况下,和异步FIFO和时钟驱动FIFO配合使用。

在BIST模式,输入寄存器通过逻辑控制变为标识发生器,由并行输入寄存器转换为线性反馈移位寄存器(LFSR),用来产生一个511字节的序列码,该序列码由数据和包括异常字符的特殊字符码构成,提供与接收器特定LFSR相匹配的预设伪随机序列码。

2.2.3 编码器

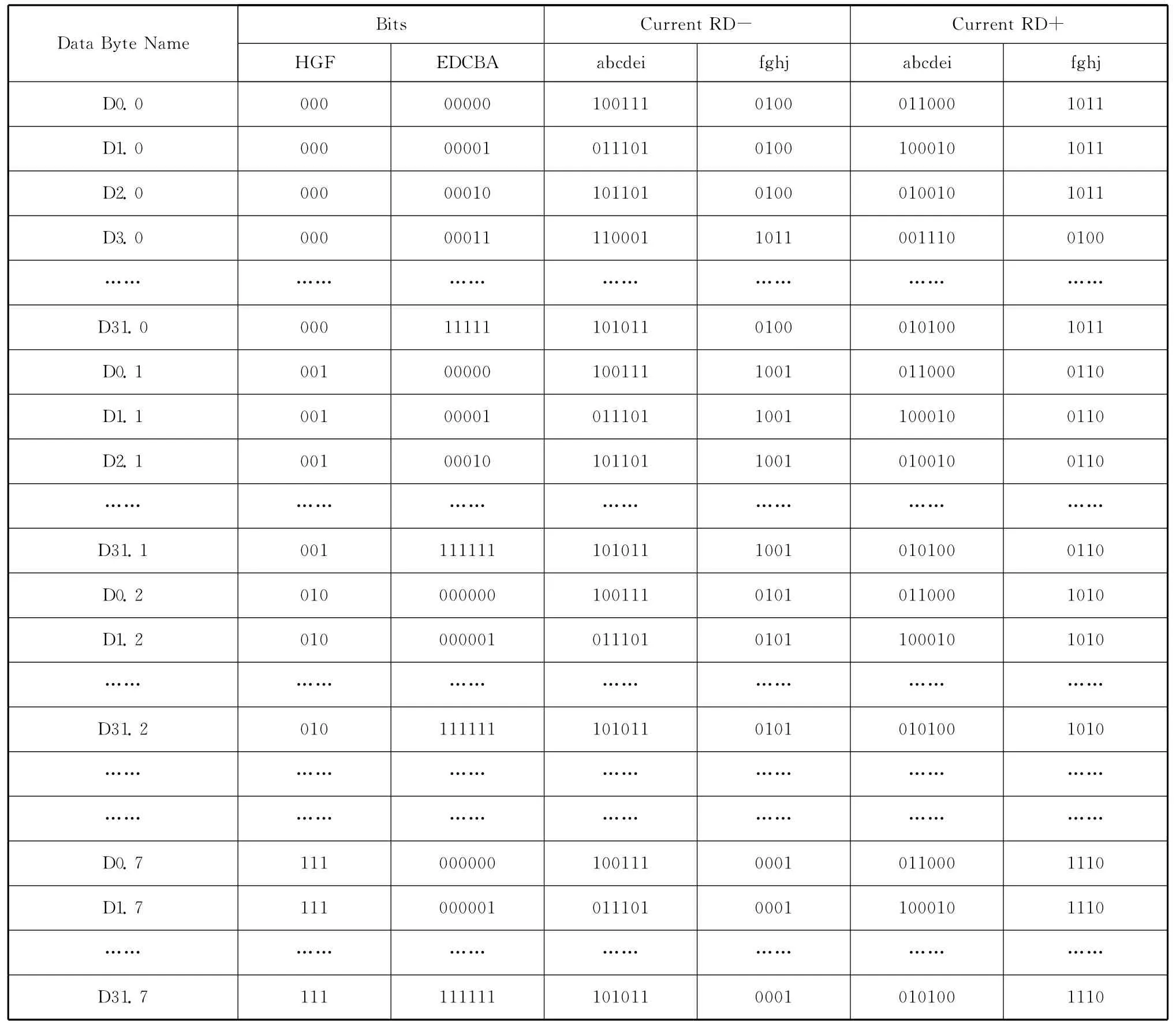

编码器依据ANSI X3.230(光纤通道)和IBM ESCON通道规范、将输入寄存器保存的数据转换为适于串行接口链路发送的编码。根据SC/D输入状态,输入数据D0–7转换成一个数据码或特殊字符。如SC/D为高电平,输入数据为控制代码,依据特殊字符编码表(参见表4)进行编码;如SC/D为低电平,输入数据依据数据编码表(参见表2)进行编码。如果输入禁止超过一个字节的时间,编码器输出一个特殊字符K28.5(或SYNC)用来保持链路同步。SVS输入强制发送特定异常编码,用户据此检查处理错误或异常。

设置MODE引脚为高电平,可以由外部编码器或带扰频器的控制器旁路编码器的8B/10B编码功能。在旁路模式,Da-j成为移位寄存器的10位输入,Da为首位,第一个从移位寄存器移出。

表2 有效数据字符集(SC/D=LOW)

2.2.4 移位寄存器

移位寄存器接收来自编码器的并行数据,由10倍于CKW字节时钟的PLL锁相环位速率时钟,将数据移位并输出到串行接口输出缓冲器。

2.2.5 PECL输出(OUTA、OUTB、OUTC)

包含相同串行数据的三对PECL差分输出缓冲器连接到内部移位寄存器,用来驱动串行传输介质(光纤、同轴电缆、双绞线),期中两对(OUTA±和OUTB±)差分输出可由POTO管脚控制,通过系统控制器可强制其输出“0逻辑”(即使光纤发送器不输出光信号)。第三个PECL差分输出缓冲器(OUTC±)不受POTO控制,适合用来输出连续的串行位流数据,用于子系统的环路测试。

为降低功耗,设计时,建议将未使用的PECL差分输出对连接到VCC。

2.2.6 测试逻辑

测试逻辑包括BIST发生器初始化和控制、测试模式时钟分配多路开关、数据编码控制逻辑等。

[1]CYPRESS.CY7B923/CY7B933HOTLinkⓇ Transmitter/Receiver[Z],2014.

[2]CYPRESS.HOTLinkⓇDesign Considerations[Z],2014.