毫米波通信系统QPSK 调制器设计*

黄 刚,陈昌明

(成都信息工程大学 通信工程学院,成都 610225)

1 引言

随着4G 网络在全球大范围的部署和使用,它在给人们带来高速上网以及多业务服务的同时,其不足也开始慢慢凸显出来,主要体现在安全保密性、数据通信能力以及容量受限等方面。为了克服这些缺点,5G 网络已经悄然兴起,它不仅能够满足诸如3D 电影、远程服务以及实时流的超高清内容传输,而且其基于毫米波通信系统的数据传输速率可以达到峰值10 Gb/s,是目前通信网络的10~100 倍。毫米波作为一种新的电磁频谱资源[1-2],由于其具有宽阔的信息带、独特的电磁波传播特性、穿透能力强以及天线尺寸小、分辨率高和重量轻等优势,可以很好地应用于5G 网络、卫星通信、无线通信以及交通工具防撞等领域。文献[3]介绍了2013 年研发出的60 GHz、数据率2.5 Gb/s、基于π/2-QPSK 调制方式的收发芯片,文献[4]介绍了研发出的中心频率60 GHz、数据率2 Gb/s、相位噪声-90 dBc/Hz@1 MHz、采用QPSK调制方式的宽带通信系统,但上述基于集成电路的毫米波通信系统在调制方式[5]、数据速率和相位噪声等指标方面都可以进一步改善。基于此,本文以毫米波通信系统为背景,采用改进型π/4-QPSK 调制方案,引入FPGA 控制,设计了一种高速率、低相噪可用于毫米波通信系统的QPSK 调制器。

2 系统指标要求与方案设计

毫米波QPSK 调制器设计指标如下:

(1)中心频率:30 GHz;

(2)QPSK 数据速率:3 Gb/s;

(3)相位噪声:≤-100 dBc/Hz@10 kHz,

≤-100 dBc/Hz@100 kHz;

(4)输出功率:≥4 dBm。

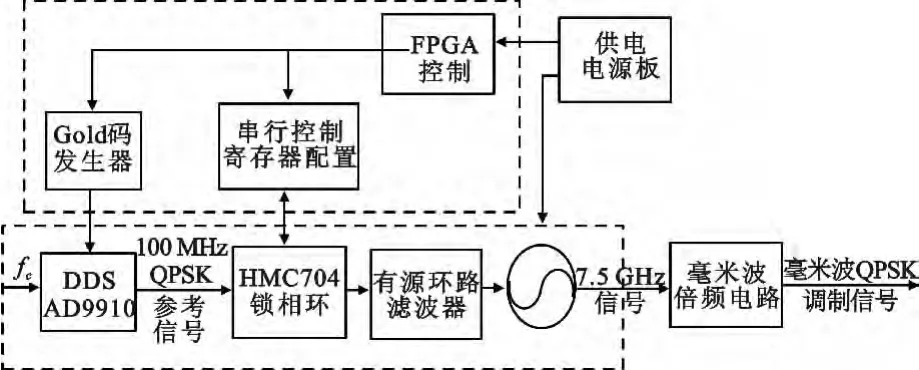

通过对毫米波QPSK 调制器系统特性以及设计指标的分析,对系统电路进行总体规划,提出了如图1 所示的系统设计方案图。通过FPGA 生成伪码发生器和控制单元,以Gold 码为伪随机序列输出,控制DDS 单元AD9910 产生100 MHz QPSK 信号,然后对锁相环(Phase-locked Loop,PLL)输出信号倍频,将7.5 GHz 微波信号搬移到毫米波频段,通过调制实现中心频率30 GHz的毫米波QPSK 信号输出。系统中,FPGA 芯片选用Altera 公司的 Cyclone II EP2C35F672C6,主频时钟50 MHz;DDS 芯片使用ADI公司AD9910;锁相环芯片为HMC704LP4E;毫米波倍频器选用GaAs 工艺的单片微波集成电路芯片(MMIC)。

图1 毫米波QPSK 调制器系统方案图Fig.1 Block diagram of millimeter wave QPSK modulator

3 π/4-QPSK 调制及Gold 码分析

3.1 π/4-QPSK 调制

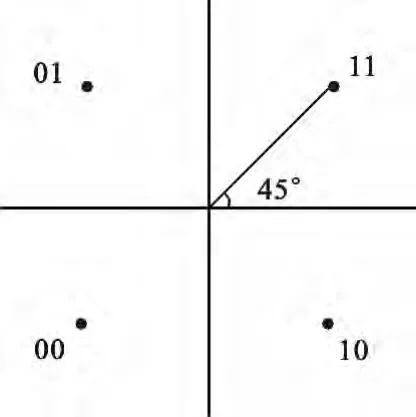

由于QPSK 调制信号相邻码元最大相位跳变为±180°,会引起载波包络起伏,使载波信号功率谱扩展,在通过带限或非线性信道时,其频谱扩散严重。为提高通信质量,本文采用改进的π/4-QPSK 调制[5],信号星座图设计如图2 所示。其载波信号相位是前一码元相位与当前码元相位增量之和,相位为π/4、3π/4、-3π/4、-π/4,相邻码元的最大相移为±135°,从而有利于接收端提取码元同步。

图2 π/4-QPSK 信号星座图Fig.2 Constellations of π/4-QPSK signal

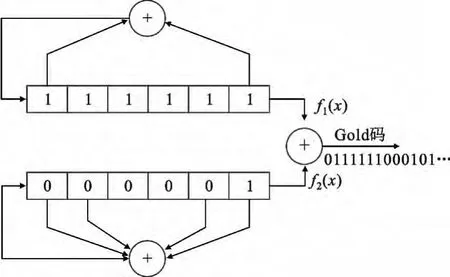

3.2 Gold 码分析

为增强通信系统抗干扰性、安全保密性以及解决频谱资源紧张等问题,本文采用扩频技术实现毫米波通信系统调制器的设计。扩频通信系统使用基于m 序列优选对的Gold 码作为伪随机编码输出,它由两个长度相同、速率一样但码字不同的m 序列优选对模2 相加后得到。由文献[6]可知,若任意两条m 序列其互相关函数Rab(τ)满足

式中,r 为移位寄存器级数,则称这两条序列为m 序列优选对。如果序列{a}和{b}为长N=2r-1 的m序列优选对,把{a}序列设为参考序列,对{b}序列进行i 次移位,则可得到新的{bi}(i=0,1,…,N-1)序列,然后与{a}序列模2 加后即可得到Gold 序列,其长度为N。

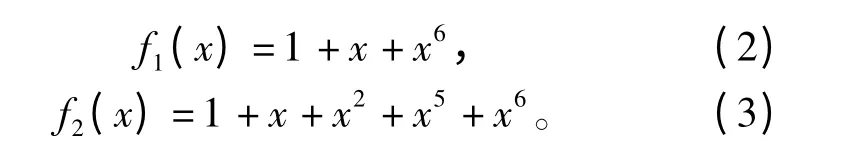

本文采用r=6 的两条m 序列,其本原多项式分别为

图3 Gold 码发生器结构图Fig.3 Generator of Gold code

将f1(x)本原多项式初始状态设为111111,f2(x)本原多项式初始状态设为000001,由此可得Gold 码序列多项式为

采用Verilog HDL 语言编写Gold 码发生器部分代码如下:

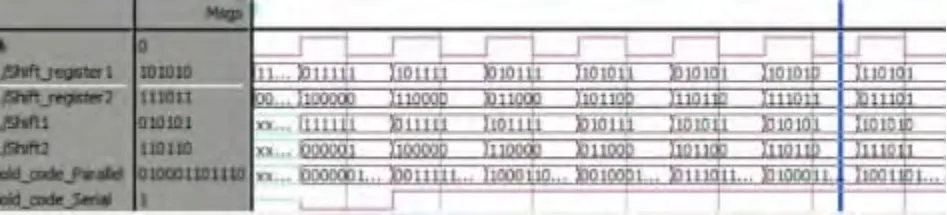

基于Modelsim 的Gold 编码仿真结果如图4 所示,其输出序列为0111111000101…,仿真结果与理论分析吻合。

图4 Gold 编码Modelsim 仿真结果Fig.4 Gold code result of Modelsim simulation

为保证DDS 输出QPSK 调制信号实现频率以及幅度不变,而相位按照Gold 编码跳变,采用单音模式控制AD9910,相位跳变点数设计为32个,其相应的寄存器十六进制参数值为

4 电路测试结果与分析

微波电路部分基板材料采用ROGERS 4350B(介电常数3.66,厚度0.508 mm),为了满足系统电磁兼容性以及可靠性要求,本文采用微波电路安装在铝腔体上层,下层安装FPGA 控制板以及电源板。毫米波电路部分由于对周围干扰较敏感,采用单独腔体设计,使用金丝键合工艺,7.5 GHz微波电路实物如图5 所示。

图5 7.5GHz 微波电路实物图Fig.5 Microwave circuit at 7.5 GHz

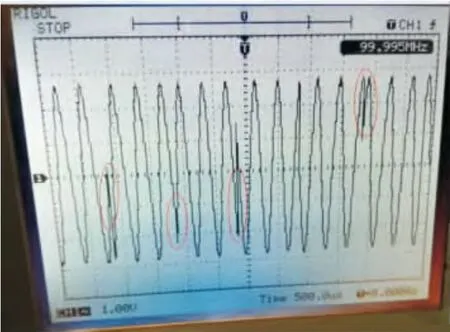

图6 为100 MHz DDS 输出QPSK 参考信号测试结果,由此可知,在FPGA 控制下,系统工作稳定,示波器测得信号相位跳变为π/4、3π/4、- 3π/4、-π/4,图中画圈的相位跳变尖峰其意义在于保证了波形的连续性。

图6 100 MHz QPSK 参考信号测试图Fig.6 Measured result of QPSK reference signal at 100 MHz

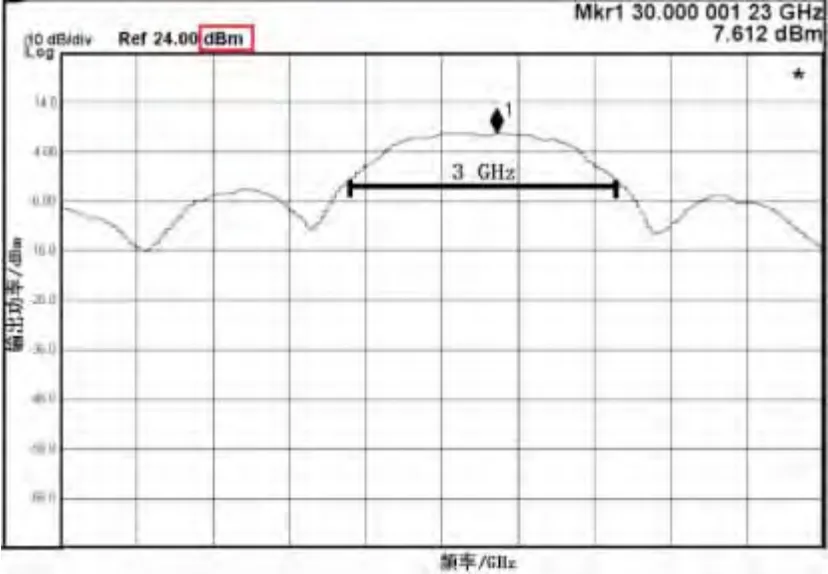

图7 为30 GHz毫米波输出QPSK 调制信号频谱图测试结果,其中心频率30 GHz,信号输出功率大于4 dBm,数据率3 Gb/s,对旁瓣抑制较差,主要原因是信号通过了非线性系统以及倍频后滤波器尺寸加工条件限制和电源干扰所引起,系统工作在毫米波频段缓解了频谱资源紧张,展宽了信号带宽。

图7 30 GHz 毫米波QPSK 调制信号(数据率3 Gb/s)测试图Fig.7 Measured result of millimeter wave QPSK modulation signal at 30 GHz(data rate 3 Gb/s)

图8 为30 GHz载波处相位噪声测试结果,相位噪声优于-100 dBc/Hz@100 kHz,其中100 MHz信号测试仪器采用RIGOL DS 5102M 示波器,微波和毫米波部分测试仪器使用Agilent N9030A PXA 信号分析仪。

图8 30 GHz 载波处相位噪声测试图Fig.8 Measured result of phase noise at 30 GHz

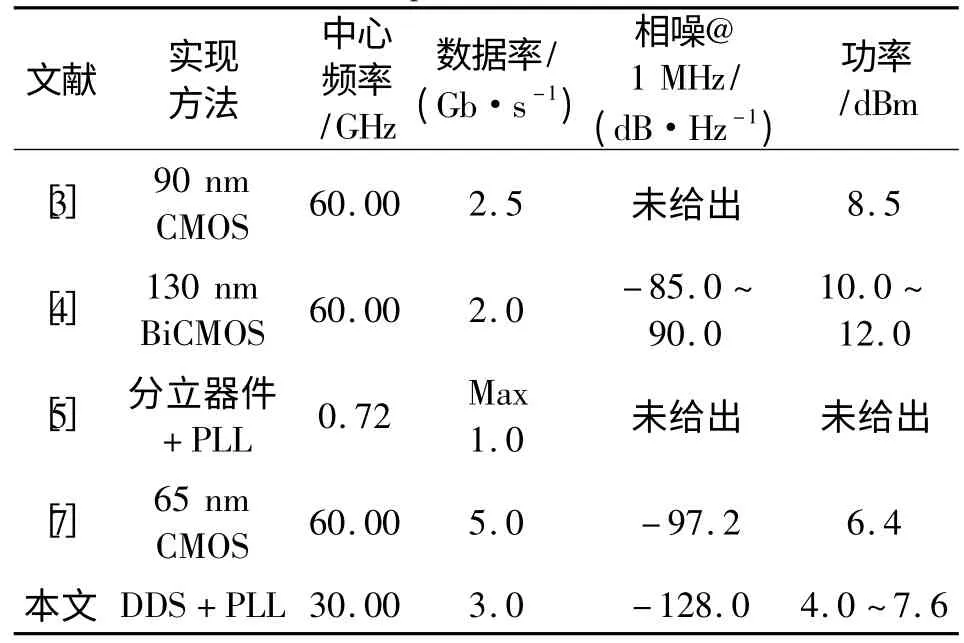

表1 给出了本文研究结果与部分文献指标的对比情况。

表1 本文与部分文献研究指标对比Table 1 Research index comparison between this papar and part references

5 结束语

本文采用改进型π/4-QPSK 调制方式设计了一种可用于毫米波通信系统的QPSK 调制器,兼备高数据率和优异相位噪声的优点,且系统运行速度快、成本低、可靠性高,对其他毫米波通信系统QPSK 调制器的设计具有一定的实际参考价值。但是,由于系统中多次使用了放大电路以及器件和工艺条件的限制,使系统功耗和体积增加,不利于小型化和低功耗,因此进一步深入研究本课题的重点在于降低系统功耗和体积。

[1]张迎春,王自力,孙婷婷,等.Q 波段倍频频率源的技术研究[J].低温与超导,2014,42(3):74-78.ZHANG Yingchun,WANG Zili,SUN Tingting,et al.Technical studies of Q-band frequency Multiplier source[J].Cryogenics and Superconductivity,2014,42(3):74-78.(in Chinese)

[2]Carpenter S,He Z X,Bao M Q,et al.A Highly Integrated Chipset for 40 Gbps Wireless D- Band Communication Based on a 250 nm InP DHBT Technology[C]//Proceedings of 2014 IEEE Compound Semiconductor Integrated Circuit Symposium.La Jolla,CA:IEEE,2014:1-4.

[3]Tsukizawa T,Shirakata N,Morita T,et al.A fully integrated 60 GHz CMOS transceiver chipset based on Wi-Gig/IEEE802.11ad with built-in self calibration for mobile applications[C]//2013 IEEE International Solid-State Circuits Conference Digest of Technical Papers.San Francisco,CA:IEEE,2013:230-231.

[4]Reynolds S K,Floyd B A,Pfeiffer U R,et al.A silicon 60- GHz receiver and transmitter chipset for broadband communications[J].IEEE Journal of Solid- State Circuits,2006,41(12):2820-2831.

[5]王志超,王平连.一种用于高速QPSK 解调的四次方环载波恢复电路[J].电讯技术,2012,52(8):1312-1316.WANG Zhichao,WANG Pinglian.A fourth power carrier recovery circuit for high- rate QPSK demodulation[J].Telecommunication Engineering,2012,52(8):1312-1316.(in Chinese)

[6]曾兴雯.扩展频谱通信及其多址技术[M].西安:西安电子科技大学出版社,2005:58-65.ZENG Xingwen.Spread communication spectrum and multiple access technology[M].Xi'an:Xidian University Press,2005:58-65.(in Chinese)

[7]Kuang L X,Yu X B,Jia H K,et al.A Fully Integrated 60 GHz 5 Gb/s QPSK Transceiver With T/R Switch in 65-nm CMOS[J].IEEE Transactions on Microwave Theory and Techniques,2014,62(12):3131-3145.