低功耗高精度全CMOS基准源的设计

福州大学物理与信息工程学院 王万金 陈群超

低功耗高精度全CMOS基准源的设计

福州大学物理与信息工程学院 王万金 陈群超

基于华大九天EDA工具以及CSMC_0.18um工艺设计了一种适用于低功耗SoC系统的高精度电压基准模块。电路后仿真结果表明,此电路在1.8V电源电压下,-40~125℃的温度系数为14.47ppm/℃,基准电压源输出电压约为564mV,27℃时静态电流约为402nA,电路总静态功耗约为724nW(包含启动电路),1kHz时的电源抑制比为-39.55dB,电源上电后,电路能够快速启动,电路版图面积(不包含外围PAD)仅为0.0045mm2。

基准源;低功耗;高精度

0 前言

在集成电路设计中,基准电压源随处可见,几乎所有的模拟和数字系统都需要用它来产生与温度变化、电源电压变化和工艺变化无关的直流电压。电压基准模块是绝大多数SoC系统中必不可少的基础模块,用以提供不随PVT变化的电压或者电流。随着SoC片上系统的发展,超大规模集成电路对于带隙基准源的精度和功耗逐渐有着更高的要求。在当代SoC系统,尤其是可穿戴设备的设计过程中,功耗已经成为与面积和性能同等重要的设计指标,降低可重用IP的功耗会使整个SoC的功耗设计与分析更加简便和快捷。因此他的性能严重影响着SoC系统的整体性能。

1 基准电路的工作原理

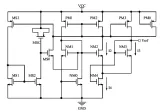

我们所提出的电压基准源完整电路如图1所示。基准模块电路主要由启动电路,电压基准电路组成。其中,启动电路由MS0~MS3、MSC组成,当电路正常启动工作后会自动从基准电路断开,以减小电路的功耗。电压基准电路中,PM1、PM2、NM1、NM2、NM4组成自偏置电流源结构,PM1和PM2以及NM1和NM2分别组成电流镜结构,并且相互提供偏置电流,通过电流镜的相互耦合(正反馈),最终形成一股稳定的基准电流。PM3和NM3组成有源负载电路。PM4和NM0用于对电压基准电路进行高温阶段的温度补偿,最终生成一个具有零温度系数,并且输出基准电压不依赖于电源电压的基准电压。

图1 高精度带隙基准模块电路图

1.1 CMOS晶体管特性分析

根据CMOS晶体管的I-V特性,当MOS管工作于亚阈值区时,漏电流公式:

式中,K为MOS管的宽长比(W/L),μ为载流子迁移率,T0为参考温度,μ0为在T0下载流子迁移率,T为绝对温度,m为一个与工艺有关的经验系数(其值在1~2之间);COX为栅氧化层电容;VTH为MOS管的阈值电压;η为亚阈值斜率;VT(=kBT/q)为热电压,kB为波尔兹曼常数,q为单位电荷。实际绝大多数情况下,MOS管漏源电压VDS远大于VT,即VDS>=4VT,因此,式(1)可以化简为:

同时,根据式(3)可推导出此时的栅源电压表达式为:

当MOS管工作于饱和区时,漏电流可表示为:

根据式(5)可得到此栅源电压表达式为:

当MOS管工作于线性区时,漏电流可表示为:

1.2 电压基准电路分析

在电流源部分,采用具有自偏置结构的电流源,此时所有PMOS晶体管工作于饱和区,NMOS晶体管NM1和NM2工作于亚阈值区,晶体管NM3工作于饱和区,晶体管NM4工作于深线性区,用做电阻,以减小版图面积。

假设NMOS晶体管NM1、NM2、NM3、NM4各自的载流子迁移率、栅氧化层电容、阈值电压相等,且先不考虑体效应和沟道长度调制效应。则根据基尔霍夫电压定律:

所以,基准电压Vref表达式为:

根据电流镜结构可得晶体管PM1与PM2、PM1与PM3的漏电流之比为:

联立式(4)、(6)、(10)、(11),经化简后可得表达式:

根据基尔霍夫电流定律,联立式(11)可得:

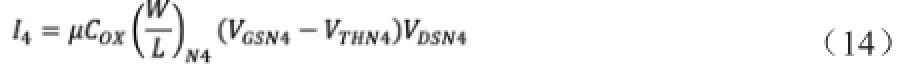

因为晶体管NM4工作于深线性区,根据式(7)其漏电流表达式可近似写成:

由电路图结构可得:VGS4=Vref,联立式(4)、(9)代入式(14)得:

联立式(12)、(13)、(15)可得表达式:

阈值电压可以写成于温度的线性关系:

式中是参考温度,是负(一阶)温度系数。

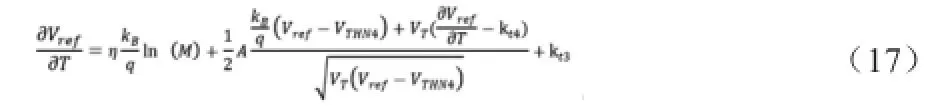

联立式(16)、(17)将基准电压对温度求偏导:

因为VTHN3(T0)=VTHN4(T0),kt3=kt4,此时式(18)可写成:

根据VT=kBT/q、式(19)可进一步化为:

式中,第一项表达式为正温度特性,第二项为负的温度特性,因此只要适当设置晶体管NM1~4、PM1~3就可以使得,即满足以上式子,实现零温度系数的基准电压。

1.3 启动电路和温度补偿电路

如图1所示,在自偏置电流镜结构中,由于负反馈电阻(工作在深线性区的MOS管NM4)存在,电路存在两个工作点。为了使自 偏置电路正常工作,附加一个由MS0、MS1、MS2、MS3、MSC组成的启动电路,保证电路正常启动。可以发现,电源上电后电路能快速启动。当电路正常稳定工作后,启动电路会自动脱离基准电路,以降低电路的功耗。

根据式(16)调整各个管子尺寸,不能使得式(20)完全满足,电路只能达到一阶温度补偿。本文利用GGNMOS和GDPMOS管在高温时的漏电流急剧增大的特性,对基准电压做高温阶段的温度补偿,使其具有更好的温度特性。

图2 常温下输出基准电压与电源电压的关系。

图3 基准电压的温度特性

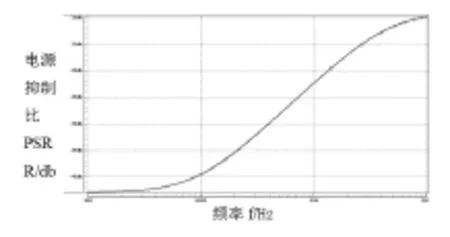

图4 交流分析:基准电压的电源抑制比

图5 常温下输出基准电压与电源电压的关系

2. 基准电路的仿真结果

基于华润上华0.18um工艺设计电路,并使用华大九天EDA工具对电路进行仿真。图2显示在常温下输出基准电压与电源电压的关系,可以看到电源电压大于0.8V时,基准能够正常输出基准电压。输出基准电压的线性度为0.7%。图3为带隙基准的温度特性曲线图,电路经过温度补偿后达到较好的温漂系数(ff工艺角下的温漂系数仅为14.47 ppm/℃),输出基准电压稳定在0.56V左右。图4是对电路进行交流分析情况下带隙基准的电源抑制比。在室温下,电源电压为1.8V时,输出基准电压在1kHz的电源抑制比为39.55dB。图5是对电路进行瞬态分析后,电源电压波形图和输出基准电压的波形图进行对比。通过对比,可以明确带隙基准在电源上电后能够稳定快速启动。

表1显示带隙基准源在三个不同工艺角(tt、ff、ss)下,各个参数的结果。仿真结果表明,该电路可以获得低功耗高精度的基准电压。图6是电压基准源的完整版图。

表1 不同工艺角下,带隙基准源的性能

图6 带隙基准源版图

3. 结论

本文提出了一种工作在亚阈值区的、不带电阻的基准电压源电路。通过MOS晶体管的栅源电压和栅源电压差产生具有正负温度系数的电压相加获得零温度系数的基准电压。该电路结构具有较低的功耗,较低的温度系数,较高的电源抑制比,并且具有较小的版图面积,适用于应用在低功耗的SOC系统的电压基准模块。

[1]陈贵灿,等译.毕查德·拉扎维著.模拟CMOS集成电路设计[M].西安,西安交通大学出版社,2002.12.

[2]Yanhan Zeng,Yirong Huang,Miaowang Zeng and Hong-Zhou Tan,A 1.2NW,2.1PPM/°C SUBTHRESHOLD CMOS VOLTAGE REFERENCE WITHOUT RESISTORS[J].IEEE J Solid-State Circuits

王万金(1995-),男,福建泉州人,大学本科,现就读于福州大学物理与信息工程学院微电子科学与工程专业。

陈群超(1983-),男,福建福州人,硕士,福州大学物理与信息工程学院助理研究员。