10 GHz低相噪扩频时钟发生器的设计与实现*

曾 云,邱玉松,张 锋,夏 宇

(湖南大学 物理与微电子科学学院,湖南 长沙 410082)

10 GHz低相噪扩频时钟发生器的设计与实现*

曾云†,邱玉松,张锋,夏宇

(湖南大学 物理与微电子科学学院,湖南 长沙410082)

摘要:基于55 nm CMOS工艺设计并制造了一款小数分频锁相环低相噪10 GHz扩频时钟发生器(SSCG). 该SSCG采用带有开关电容阵列的压控振荡器实现宽频和低增益,利用3阶MASHΔΣ调制技术对电路噪声整形降低带内噪声,使用三角波调制改变分频系数使扩频时钟达到5 000×10(-6).测试结果表明:时钟发生器的中心工作频率为10 GHz,扩频模式下峰值降落达到16.46 dB;在1 MHz频偏处的相位噪声为-106.93 dBc/Hz.芯片面积为0.7 mm×0.7 mm,采用1.2 V的电源供电,核心电路功耗为17.4 mW.

关键词:扩频时钟发生器;锁相环;ΔΣ调制器;相位噪声

当前,随着半导体工艺的不断发展,电子产品工作频率越来越高,高频信号的辐射也越来越强,芯片间的电磁干扰(EMI)变成了一个不容忽视的问题[1-2].在无线通信系统中,当数据处理与传输的速率达到Gbps的水平时,电路辐射产生的噪声大小直接决定了传输数据信号的优劣.为了抑制EMI对传输通道、设备及系统性能的影响,传统上使用金属屏蔽盒以及RCL无源器件的滤波来实现,但随着电路系统的复杂度和集成度不断提高,上述方法已很难达到目的,而基于锁相环的扩频时钟技术(SSCG)[3-7]作为有效的低成本片内解决方案正在迅速发展中,它通过将信号能量扩展到一个较宽的范围内,有效地减小峰值和谐波的功率,从而从信号的源头减小了EMI,降低了系统产品的设计难度.

近年来,国内外提出了多种不同的扩频时钟电路抑制EMI.Hsieh等采用的VCO直接调制方式需要极大的滤波电容,会增加电路的功耗和面积[3];Cheng等使用的多相时钟相位插入方式很难达到相位的良好匹配,会加大电路的设计难度[4];Wong 和Caro等采用的调制方式引入的量化噪声大,对EMI的抑制能力不够,会恶化其相位噪声[5-6].

目前对于SSCG的研究大多集中于6 GHz频率以下,而对于6 GHz以上的较少涉及.本文针对SSCG在频率、相位噪声等方面的问题,设计了一款10 GHz的超高频率低相噪扩频时钟发生器,其在1 MHz频偏处的相位噪声为-106.93 dBc/Hz,通过采用全数字电路的3阶MASHΔΣ调制器改善电路相位噪声,相比于其余的调制方式,实现简单,对EMI的抑制能力更强,且有较强的抗噪声能力.

1扩频时钟发生器电路设计

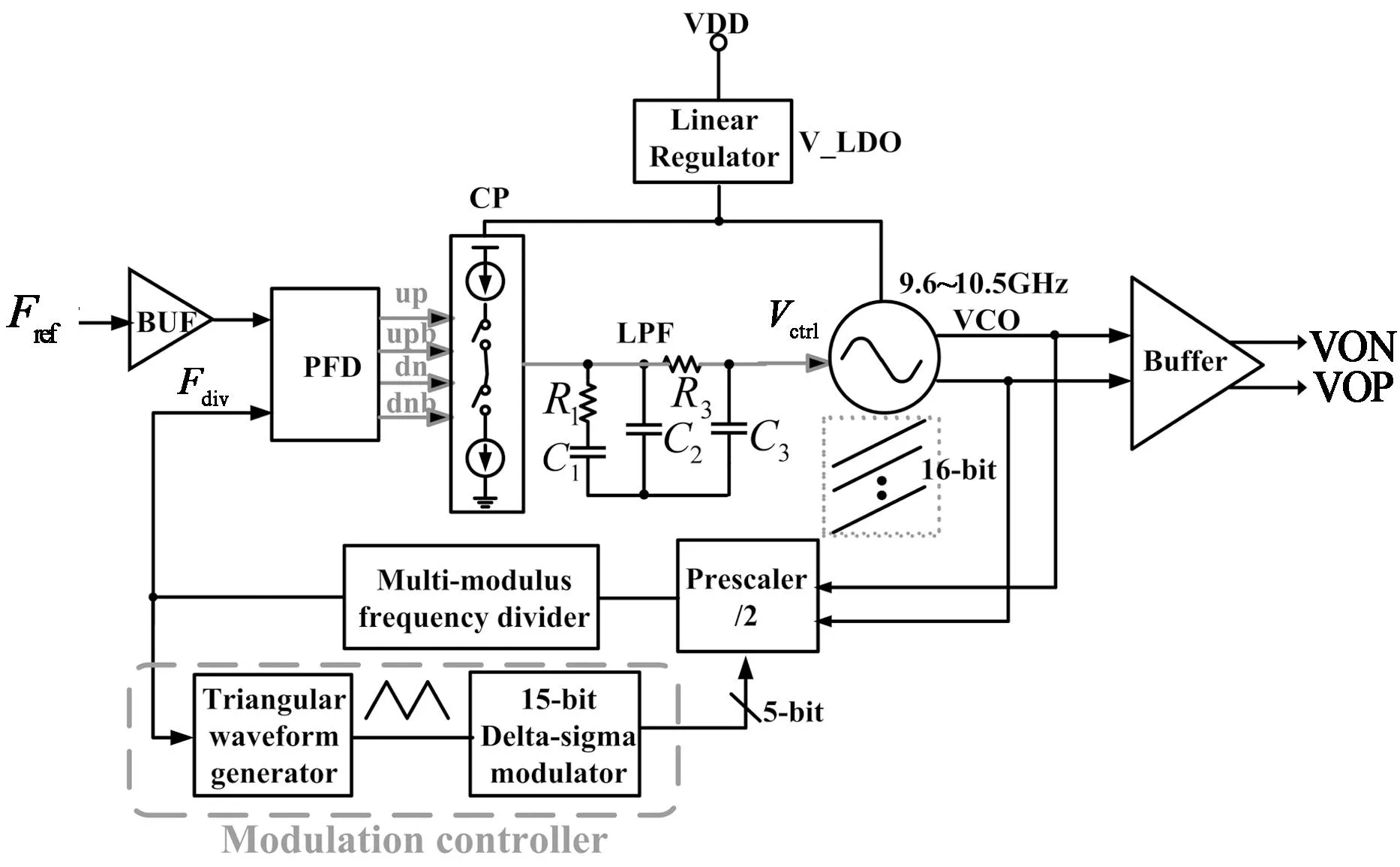

图1所示为本设计提出的扩频时钟发生器整体结构图,其中包括鉴频鉴相器(PFD)、电荷泵(CP)、环路滤波器(LPF)、压控振荡器(VCO)、多模分频器、ΔΣ调制器(DSM)及三角波发生器.

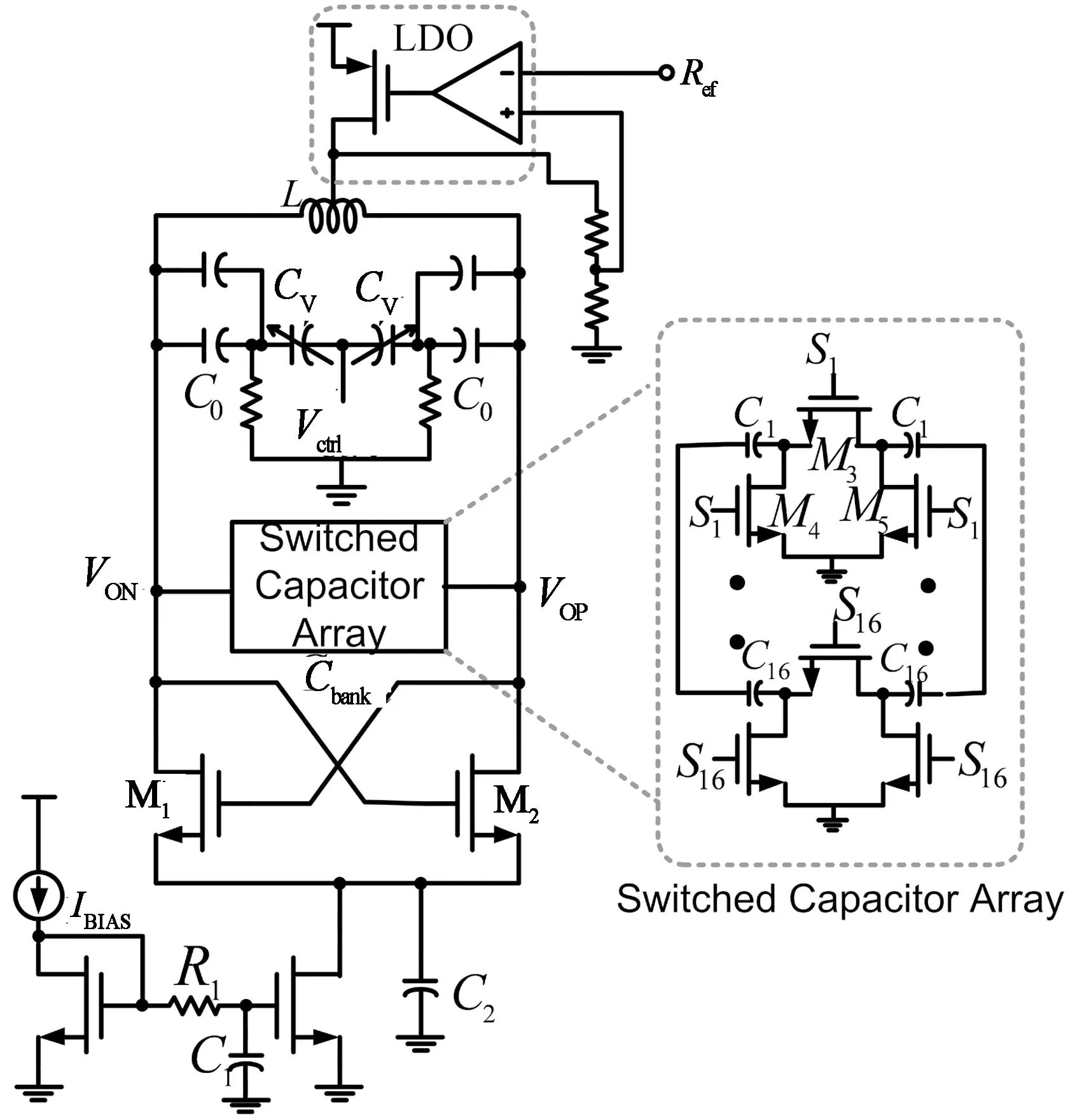

在锁相环中,低频噪声主要由PFD/CP决定,而高频噪声由VCO决定.为了获得低相噪的时钟发生器,VCO中采用了开关电容阵列技术把VCO的谐振频率范围分成若干个子频带[7],子频带的选择可以保证VCO的电压增益(KVCO)较小,避免了过大的KVCO通过AM-FM噪声转化导致VCO相位噪声的恶化;使用可编程差分电荷泵结构来提高充放电电流的匹配,减小杂散,以及满足工艺偏差的变化;通过采用小数分频技术,保证电路在很高的参考频率下也能获得很高的频率精度.通过 DSM对分频器的分频系数进行调制,随着分频系数的改变,锁相环的输出频率随之改变,并获得具有一定频率宽度的时钟信号,完成扩频的过程.同时DSM也能对输出噪声整形,大幅改善时钟发生器的相位噪声.

图1 扩频时钟发生器整体结构图

1.1宽带VCO的设计

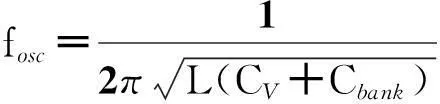

VCO设计的优劣直接决定整个时钟发生器的相位噪声性能,本设计采用了如图2所示的带开关电容阵列的宽带LC-VCO.晶体管M1和M2组成交叉耦合差分对管,作为负阻为LC谐振回路提供能量;LC频率调谐回路由片上螺旋差分电感、累积型MOS变容管和高Q值固定电容组成.VCO的振荡频率可表示为:

(1)

即VCO的电压增益KVCO为:

(2)

KVCO反映VCO输出频率对控制电压Vctrl的敏感程度,并且影响锁相环环路的增益和稳定性,以及相位噪声性能.由式(2)知:可变电容比直接影响VCO的电压增益,从而影响其调谐范围与相位噪声,但是VCO的调谐范围又与相位噪声相互矛盾.因此,为了使VCO兼具较低的相位噪声和较大的频率调谐范围,必须采用开关电容阵列来减小VCO的灵敏度.开关电容阵列中使用差分电容开关的方式来改善开关电容的Q值.为了进一步提高噪声性能,使用了具有高电源抑制比的LDO为VCO供电,加强其对电源噪声的抑制能力;为了抑制尾电流源噪声对相位噪声的影响,在共源点和地之间串入一个大的电容C2,同时利用电容C1和R1组成的低通网络滤除一部分基准电流镜像来的热噪声和闪烁噪声.该电路采用16位温度计码控制的开关电容阵列,配合可变电容形成粗调谐与细调谐相结合的技术,在减小相位噪声的同时满足了制造过程的工艺偏差和频段要求.经测试得知:VCO的调谐范围为9.6~10.5 GHz,在1 MHz处其相位噪声为-106.93 dBc/Hz.

图2 VCO电路结构图

1.2预分频器及多模分频器的设计

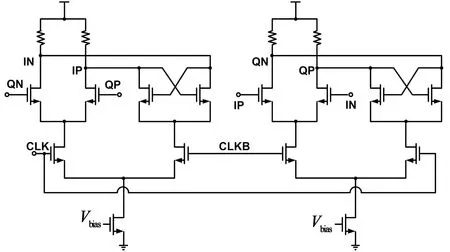

VCO的输出信号在经过输出缓冲器后作为预分频器的输入时钟,其工作频率高达10 GHz,为了满足低功耗和高速的应用要求,采用基于电流模式逻辑结构(CML)[8]的预分频器进行二分频,如图3所示.CML构成的预分频器是全差分结构,能够提供差分输出,抑制电路的共模噪声.为了减小寄生电容,提高响应速度,在设计中采用电阻作为负载;尾电流源结构的使用可以更方便地控制输出摆幅的大小,同时可以提高电路的工作速度.

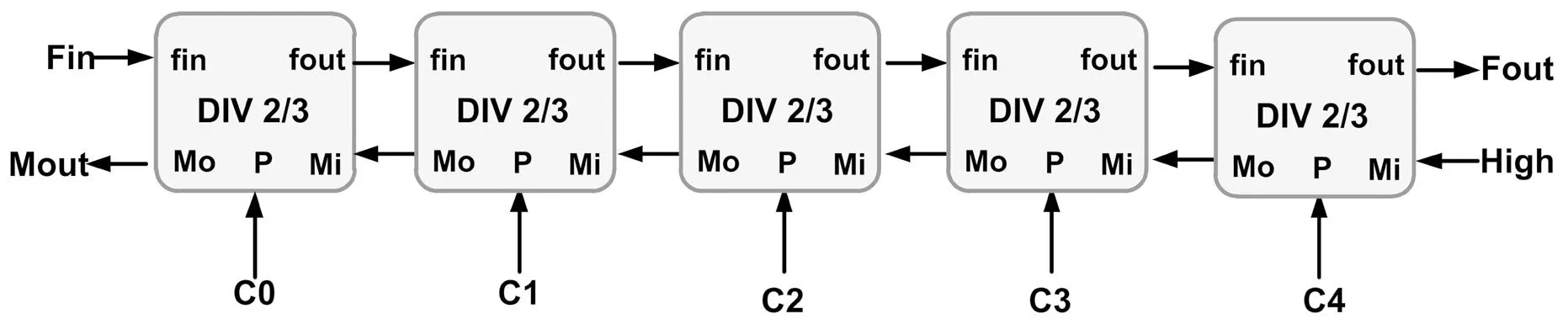

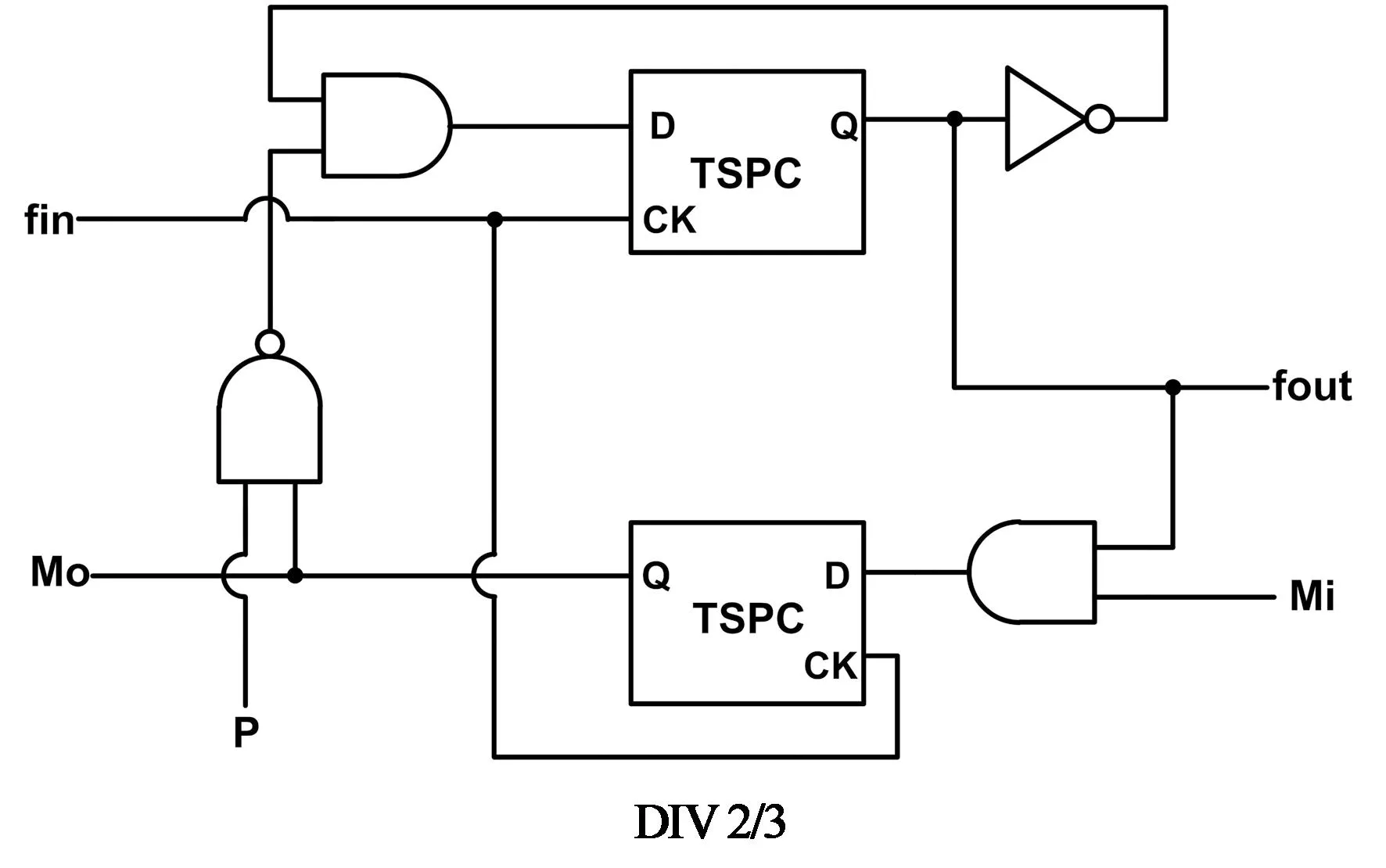

为了达到扩展频谱的目的,必须使用小数分频的锁相环结构.故在预分频器之后,使用了如图4(a)所示的多模分频器.多模分频器由5个2/3分频单元级联构成,整个分频器链中不存在延时回路,所有的2/3分频单元有着相同的结构,有利于功耗的优化及版图的便利.2/3分频器的工作原理是在一个分频周期内,当输入信号Mi有效时,若P=1,则分频单元实现3分频;若P=0,则分频单元实现 2 分频,如图4(b)所示.该分频器能够实现分频比:

N=C0+2×C1+22×C2+23×C3+

24×C4+25.

(3)

分频范围为32~61,其中可编程控制码C0~C4由DSM的输出控制.本设计中预分频器工作在10 GHz左右,经过CML二分频之后,多模分频器的输入端频率也高达5 GHz,为了能够满足电路的高速要求,2/3分频单元中的触发器均使用TSPC结构[9],经仿真验证其工作频率可达8 GHz.

图3 预分频器电路

(a) 多模分频器结构框图

(b) 2/3分频器单元

1.3鉴频鉴相器及电荷泵的设计

由于DSM的量化噪声会因非线性的存在而折叠到低频,影响带内相位噪声,而且也会导致分数杂散的产生,故对PFD及CP的线性度提出了更高的要求.如图5(a)所示,采用的PFD结构仅有3个反相器的延时,极大地缩短了死区时间,这可以减小衬底耦合的噪声和电流源噪声等对锁相环的影响;在UP信号的通路上插入了一个由传输门构成的延时单元,并设计成与反相器有近似相同的延时,以减小由两路信号到达时间不同导致的失配.在输出级加上驱动力很强的缓冲器(buffer)以保证电荷泵开关的迅速切换.

CP的输出电流噪声是锁相环带内相位噪声和参考杂散的主要来源,而电流噪声主要是由于电流失配、电荷泄漏及电荷共享等非理想效应产生的.提出的高性能CP和LPF的结构如图5(b)所示,电流源使用尺寸相对较大的晶体管,组成cascode结构,减小电流源之间的电流不匹配;采用了差分结构,两节点VF和VB通过单位增益放大器相连,使两支路的共模电平保持相同,避免了电荷共享问题,其中单位增益放大器运用了折叠式共源共栅轨到轨运放结构,提供高增益和高摆幅.由于工艺的变化,VCO的增益会发生变化,同时环路滤波器中的电阻电容也会有偏差,为了保证电路在不同工艺电压温度(PVT)的影响下仍能保持稳定,将上下开关电流设置成可编程的电流调节单元,电流在200~400 μA之间变化.同时为了更好地抑制压控振荡器控制电压上的高频成分,减小其纹波,环路滤波器采用三阶无源滤波器.其中R1与C1共同提供一个带内的零点改善相位裕度,C2提供第二个极点对分数杂散进行一定的抑制,C3提供第三个极点进一步抑制由于DSM产生的高通相位噪声对整个锁相环输出噪声的恶化.

1.4ΔΣ调制器及三角波发生器的设计

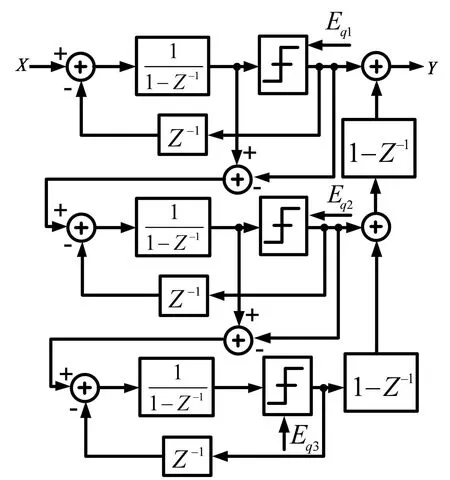

为了获得扩频时钟,必须使分频器的分频比在一定时间内发生变化,故在设计中引入了小数分频技术.但由于小数分频的分频系数存在周期性跳变问题,会产生小数杂散影响时钟发生器的相位噪声和杂散性能,所以通过采用ΔΣ调制器(DSM)[10]实现分频比的随机化,对量化噪声进行整形,将噪声往高频处推,消除小数分频带来的杂散,提高带内信噪比.为实现噪声整形并考虑到电路稳定性的需要,在设计中采用了3阶的15-bit MASH1-1-1 DSM,结构如图6所示.图中X表示输入,Y表示输出,Eqi表示第i级的量化误差,由此可得:

Y(Z)=X(Z)+(1-Z-1)3×Eq3(Z).

(4)

(a) PFD电路结构

(b) 电荷泵和环路滤波器电路

图6 MASH 1-1-1结构

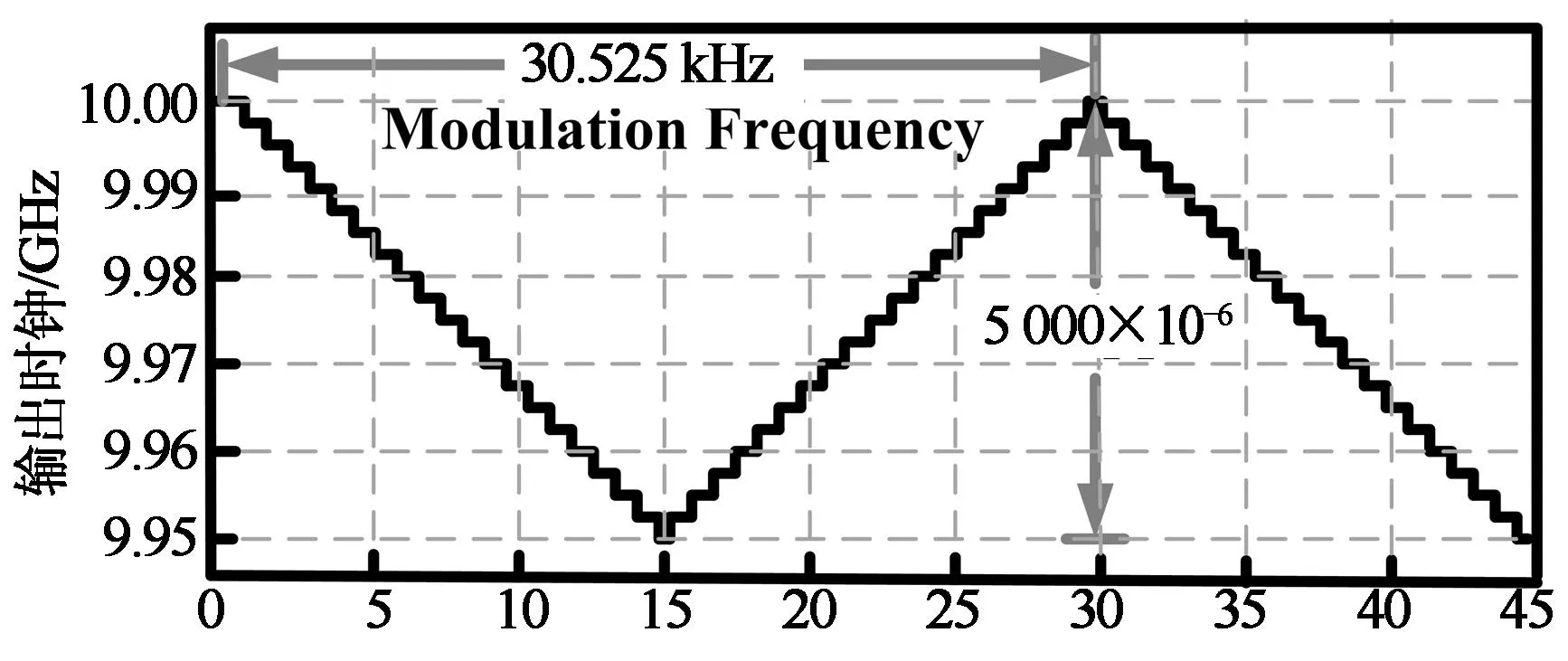

图7为输出时钟向下扩频仿真,时钟频率为9.95~10 GHz,三角波的频率为30.525 kHz.

T/us

2测试结果分析

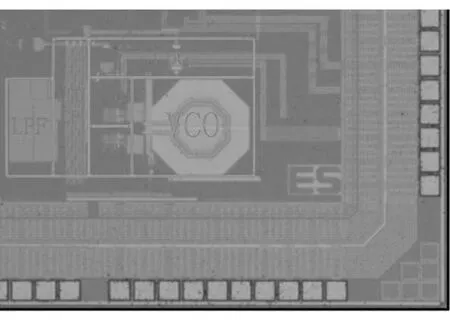

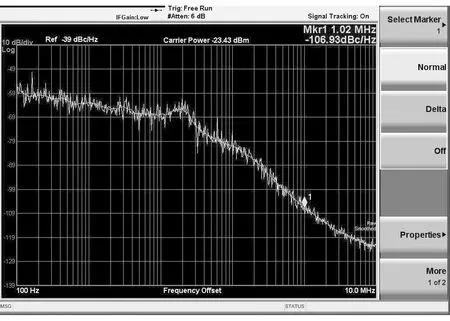

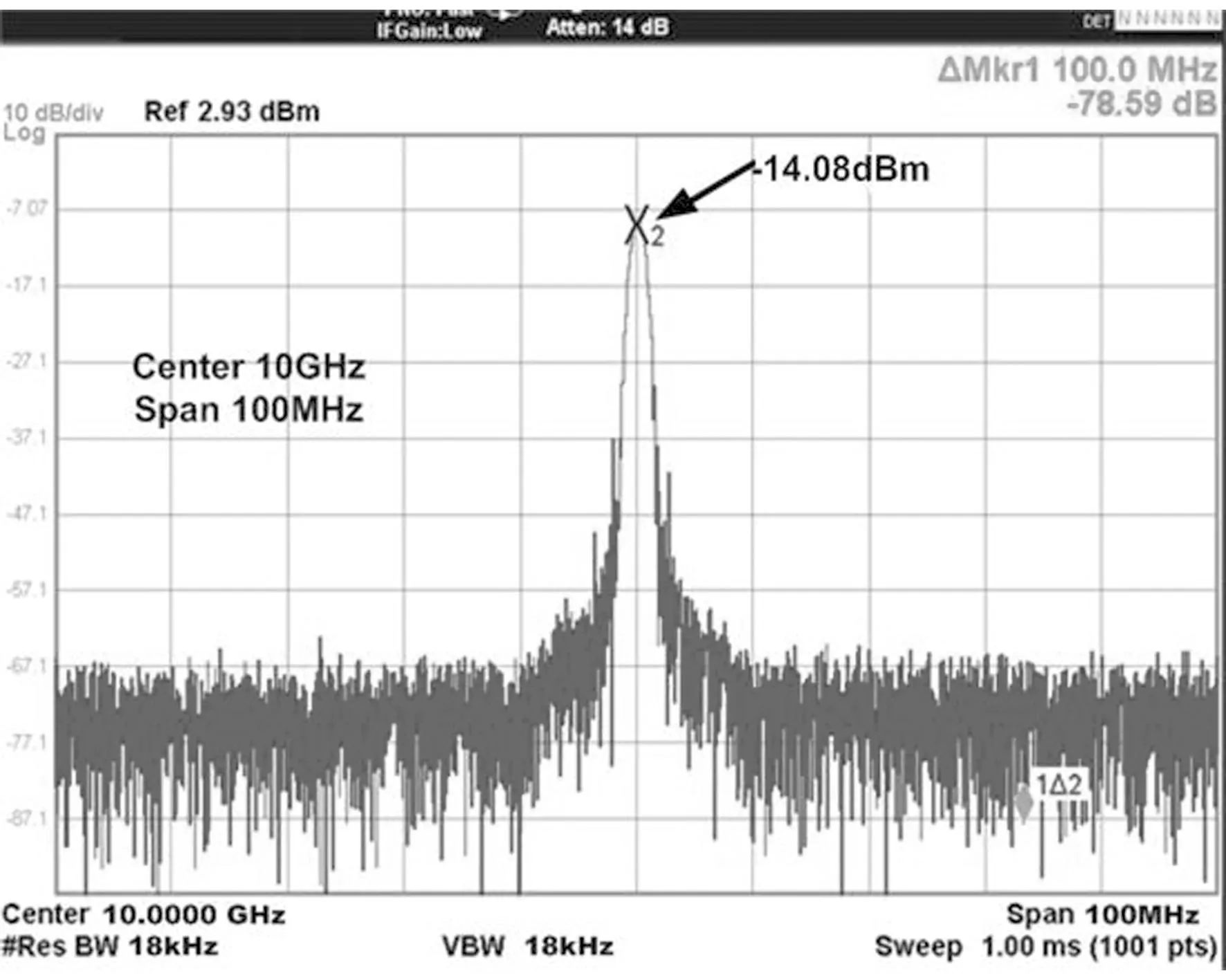

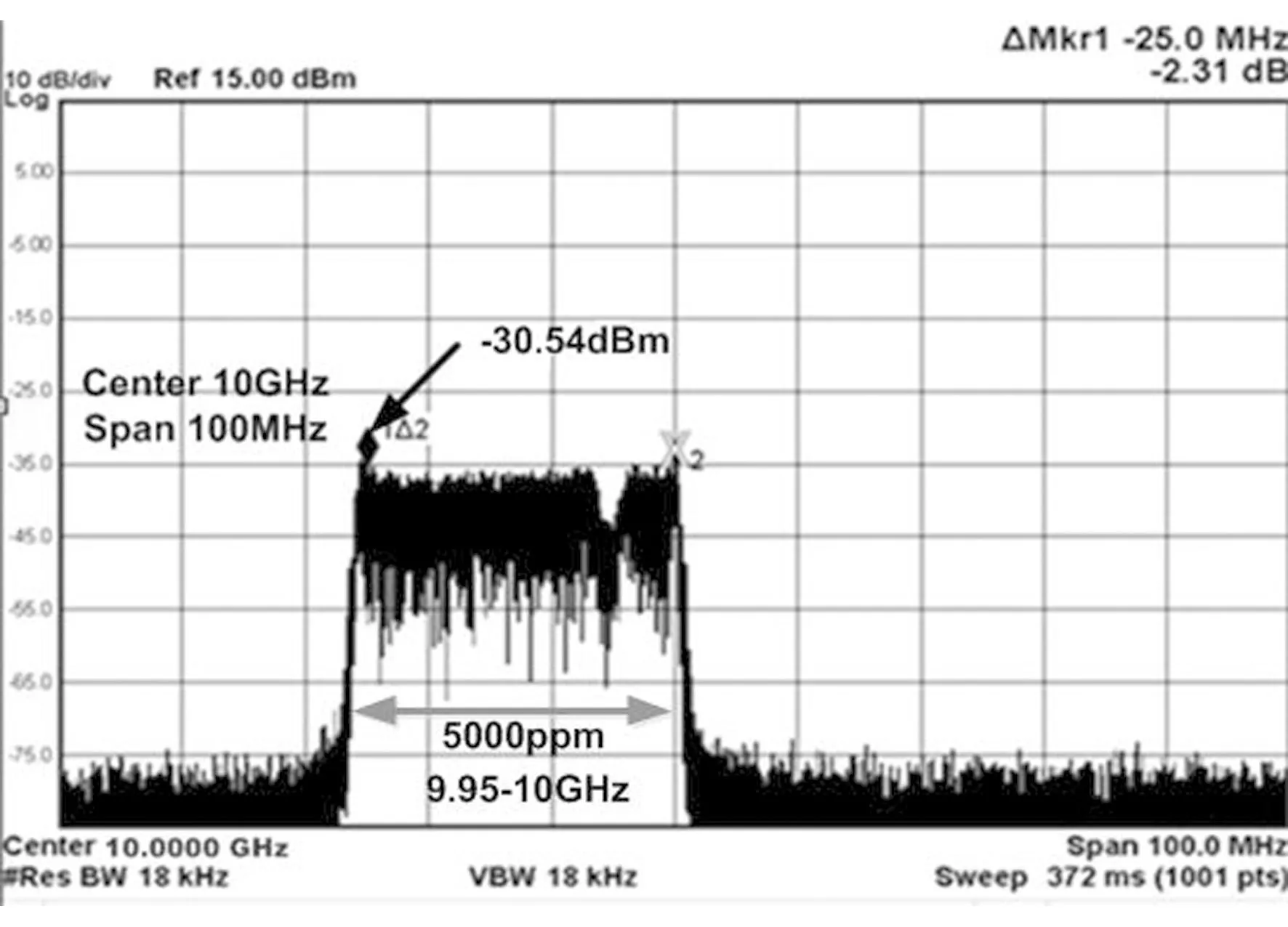

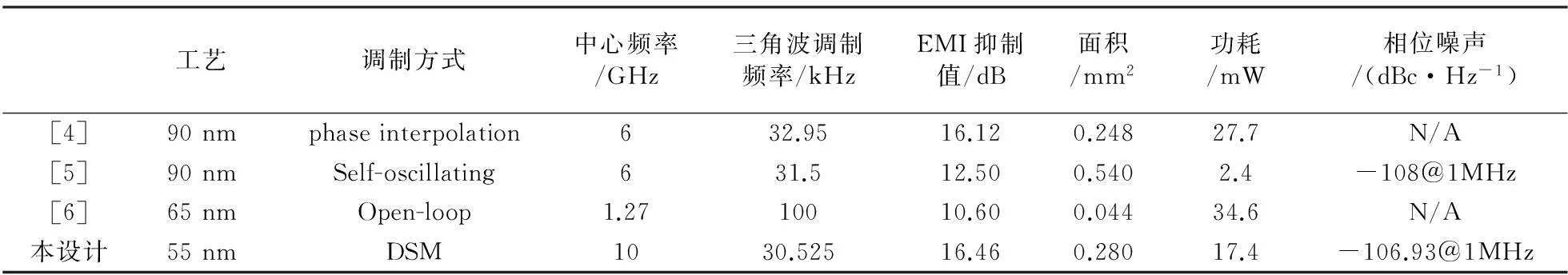

在版图布局中,为避免数字时钟对模拟射频部分的影响,采用隔离环措施对数字和模拟模块进行隔离,降低衬底耦合噪声.电路采用SMIC 55 nm CMOS 工艺流片,SSCG整体芯片照片如图8所示,电路的核心面积为0.7 mm×0.4 mm.测试时输入晶振频率为100 MHz,利用Aglient公司的频谱分析仪得到扩频时钟相位噪声测试曲线如图9所示,在1 MHz处,相位噪声大小为-106.93 dBc/Hz.扩频时钟发生器实测频谱如图10所示.在非扩频模式下,频谱的峰峰值能量为-14.08 dBm,在扩频模式下,峰峰值能量变为-30.54 dBm,向下扩频5 000×10-6,峰峰值降落16.46 dB.表1给出了与最近国际上发表的相关扩频时钟发生器测试结果的比较,本设计的显著特点是工作频率高达10 GHz,但所消耗的功耗却最低,并且在1 MHz处的相位噪声很小,对EMI的抑制效果也很好.

图8 扩频时钟发生器芯片照片

图9 相位噪声测试结果

(a) 非扩频模式

(b) 扩频模式

工艺调制方式中心频率/GHz三角波调制频率/kHzEMI抑制值/dB面积/mm2功耗/mW相位噪声/(dBc·Hz-1)[4]90nmphaseinterpolation632.9516.120.24827.7N/A[5]90nmSelf-oscillating631.512.500.5402.4-108@1MHz[6]65nmOpen-loop1.2710010.600.04434.6N/A本设计55nmDSM1030.52516.460.28017.4-106.93@1MHz

3结论

在超高频率下制造时钟发生器的最大难度在于,在高频工作下相位噪声和抗电磁干扰的能力难以提升.本文在55 nm CMOS工艺下,设计并实现了一种基于小数分频锁相环的低相噪10 GHz扩频时钟发生器.该时钟发生器采用了带开关电容阵列的VCO模块、低失配低噪声电荷泵及ΔΣ调制器模块,达到了很高的频率输出精度和良好的相噪性能.测试结果显示在扩频模式下输出频谱向下扩展5 000×10-6,时钟发生器在1 MHz处的相位噪声为-106.93 dBc/Hz,峰峰值降落为16.46 dB,验证了本设计的有效性,满足时钟发生器的应用要求.

参考文献

[1]MATSUMOTO Y, FUJII K, SUGIURA A. An analytical method for determining the optimal modulating waveform for dithered clock generation[J]. IEEE Transactions on Electromagnetic Compatibility, 2005, 47(3): 577-584.

[2]KIM J, KAM D G, JUN P J,etal. Spread spectrum clock generator with delay cell array to reduce the electromagnetic interference[J]. IEEE Transactions on Electromagnetic Compatibility, 2005, 47(4): 908-920.

[3]HSIEH Y B, KAO Y H. A fully integrated spread-spectrum clock generator by using direct VCO modulation[J]. IEEE Transactions on Circuits and Systems I: Regular Papers, 2008, 55(7): 1845-1853.

[4]CHENG K H, HUNG C L, CHANG C H. A 0.77 ps RMS jitter 6-GHz spread-spectrum clock generator using a compensated phase rotating technique [J]. IEEE Journal of Solid-State Circuits, 2011, 46(5): 1198-1213.

[5]WONG C H, LEE T C. A 6-GHz self-oscillating spread-spectrum clock generator [J]. IEEE Journal of Solid-State Circuits, 2013, 60(5): 1264-1273.

[6]CARO D, ROMANI C A, PETRA N,etal. A 1.27 GHz all digital spread spectrum clock generator/synthesizer in 65 nm CMOS [J]. IEEE Journal of Solid-State Circuits, 2010, 45(5): 1048-1060.

[7]LEI Lu, CHEN Jing-hong, LU Yuan,etal. An 18-mW 1.175-2-GHz frequency synthesizer with constant bandwidth for DVB-Tuners [J]. IEEE Transactions on Microwave Theory and Technique, 2009, 57(4): 928-937.

[8]WOHLMUTH H D, KEHRER D. A high sensitivity static 2:1 frequency divider up to 27 GHz in 120 nm CMOS[C]//Proceedings of the 28th European Solid-State Circuits Conference. New York:IEEE,2002: 823-826.

[9]HUANG Q T, ROGENMOSER R. Speed optimization of edge-triggered CMOS circuits for gigahertz single-phase clocks[J]. IEEE Journal of Solid-State Circuits, 1996, 31(3): 461-465.

[10]PARK P, PARK D, CHO S. A 14.2 mW 2.55-to-3 GHz cascaded PLL with reference injection and 800 MHz delta-sigma modulator in 0.13 μm CMOS [J]. IEEE Journal of Solid-State Circuits, 2012, 47(12): 2989-2998.

Design and Realization of 10 GHz Low Phase Noise Spread Spectrum Clock Generator

ZENG Yun†, QIU Yu-song, ZHANG Feng,XIA Yu

(School of Physics and Microelectronics, Hunan Univ, Changsha, Hunan410082, China)

Abstract:A 10 GHz low phase noise spread spectrum clock generator(SSCG) based on a fractional PLL in a 55 nm CMOS process was developed. The clock generator adopts a LC tank voltage-controlled oscillator (VCO) with switched capacitors array to obtain the wide-band frequency range and low gain, and the multi-stage noise shaping(MASH) modulating technology was utilized to shape and degrade in-band phase noise. The SSCG changes the division ratio with triangular modulation to achieve the goal of 5 000×10(-6) spread spectrum clock. The measurements show that the clock generator operates at a 10 GHz, the peak reduction of electromagnetic interference (EMI) is 16.46 dB and the phase noise is -106.93 dBc/Hz@1 MHz in Spread Spectrum Clocking (SSC) Mode. The chip core area is less than 0.28 mm2 and the core power consumption is 17.4 mW at a supply of 1.2 V.

Key words:spread spectrum clock generator (SSCG); phase-locked loop (PLL); ΔΣ modulator; phase noise

中图分类号:TN432, TN74

文献标识码:A

作者简介:曾云(1957-),男,湖南长沙人,湖南大学教授,博士生导师†通讯联系人,E-mail:yunzeng@hnu.edu.cn

基金项目:国家自然科学基金资助项目(61350007),National Natural Science Foundation of China(61350007) ;国家高技术研究发展计划(863计划)项目(2011AA010403)

*收稿日期:2015-01-27

文章编号:1674-2974(2016)02-0109-06