改进中值滤波算法及其FPGA硬件实现

彭 俊,魏 琼, 王 君, 童明浩

(湖北工业大学机械工程学院, 湖北 武汉 430068)

改进中值滤波算法及其FPGA硬件实现

彭俊,魏琼, 王君, 童明浩

(湖北工业大学机械工程学院, 湖北 武汉 430068)

[摘要]为了有效抑制数字图像在其获取和传输过程中受到的噪声污染,基于中值滤波,提出一种具有噪声检测模块的改进中值滤波算法,并在FPGA硬件平台上实现,改善了传统中值滤波会模糊图像的缺点。由实验结果分析可知,该算法不仅能有效抑制噪声,而且还能保存更多的图像细节,从而提高图像处理质量。

[关键词]现场可编程门阵列;领域相关性;噪声检测;中值滤波

数字图像在获取和传输过程中很容易受到噪声污染。噪声是模糊真实原始数据的一系列不相关数据,通常是独立的,与图像像素不相关,并且随机分布在图像中,会严重降低图像质量,引起图像信息的大量丢失,给图像识别和分析造成困难。脉冲噪声污染普遍发生在数字图像中。脉冲噪声分为椒盐噪声和随机噪声。被椒盐噪声污染的图像,噪声像素点只会取图像动态范围的最大值和最小值。尖锐而突然的干扰是图像产生椒盐噪声的主要原因。随机脉冲噪声是图像原始数据被图像动态范围内任何值代替。线性滤波是减少噪声的一种方法,但是它就算是在低密度噪声中也会严重模糊图像。基于统计排序理论的中值滤波,是因为其具备出色的抑制噪声鲁棒性和图像边缘信息保存能力而被广泛应用于航空航天、生物医学和通信工程等领域。中值滤波是将图像每一像素点的灰度值用采样窗口内排序后所有像素灰度值中值代替。传统中值滤波计算量大,耗费大量逻辑资源和时间资源。已不适用于对图像处理实时性要求越来越高的当下。经过王宇新[1]、李新春[2]等人对算法的不断改进,中值滤波算法图像处理速度有了一定提高。但是,由于它会对图像原始信息产生不必要的代替,在一定程度上会使图像变模糊。李飞飞[3]在中值滤波中加入阈比较环节,使得所处理的图像更加清晰。

本文在李双全滤波算法[4]的基础上,提出了基于FPGA硬件平台的具有噪声检测模块的改进滤波算法。即先通过阈值比较来检测可能出现的噪声点,然后用采样窗口中心像素点同周围领域像素相关性来再次深入检测噪声点。对于图像原值保留,噪声点用除窗口中心像素点外相邻像素中值代替。经过Quartus11.0SP1编程和Modelsim6.6d仿真实验,将本文算法与文献[1—3]算法的性能进行比较,结果表明该改进滤波算法不仅能有效去除噪声,还能保存更多图像细节,从而提高图像质量。

1改进滤波算法

与传统中值滤波算法不同的是,本文滤波算法加入了噪声检测模块。首先通过阈值比较来对噪声进行初步检测。然后,用窗口中心像素点同周围领域像素点相关性的比较分析来深入检测噪声。若检测为信号点,则保留原值;若检测为噪声点,则用除窗口中心像素点外领域像素中值代替。

本文采用3×3的采样滤波窗口,窗口范围内对应中心像素为x22,窗口内除中心像素外其他8个像素设为集合P,则P={x11,x12,x13,x21,x23,x31,x32,x33},其中值Pmed。通过设定阈值Ta,来判断白盐噪声灰度值范围[255-Ta,255]和黑椒噪声灰度值范围[0,Ta]。设定比较误差阈值Tb。

噪声检测模块原理:

1)初步判断:用|x22-xk|>Tb,xk∈P不等式来对噪声进行初步检测。如果对于任意xk∈P该式都成立,则可判断该点为噪声点;如果只对于部分xk该式成立,则需要深入判断。

“初步判断”用比较误差阈值Tb来对椒盐噪声进行初步检测和滤除;而“深入判断”则是通过考虑领域像素相关性来区分噪声点和信号点。经上述噪声检测模块处理后,能有效检测并滤除噪声。

2FPGA硬件实现

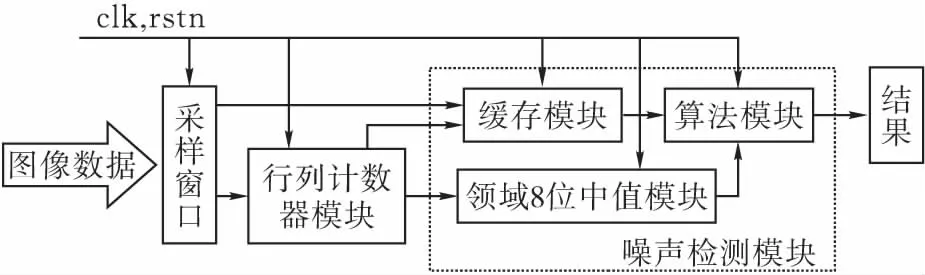

本文滤波算法采用3×3采样窗口,处理的图像数据是256×256像素大小,8bit。图像数据由Matlab软件读取并转换成16进制“.txt”文本,再用Modelsim仿真波形。将16进制“.txt”文本内容作为激励信号串行读入FPGA。仿真后产生的输出信号保存为“.txt”文本,由Matlab转换成图片显示。其中,FPGA电路结构如图1所示。

图 1 FPGA电路结构框图

由图1可知,本文滤波算法分为采样窗口模块、行列计数器模块和噪声检测模块等3个模块。3个模块分别在同一时钟信号clk和复位信号rstn下工作。

2.1采样窗口模块

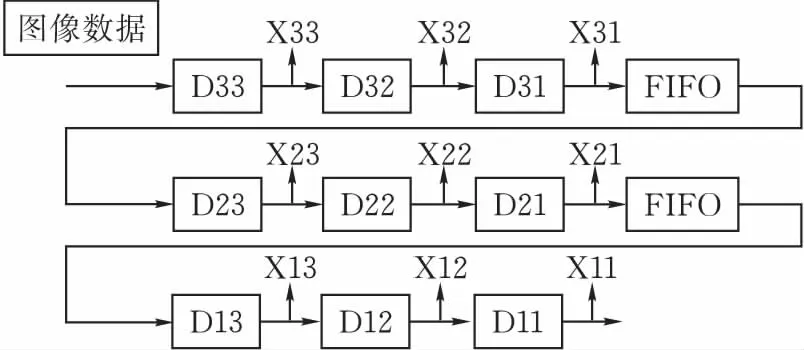

如图2所示,采样窗口模块由9个寄存器和2个FIFO组成。每次FPGA对图像进行噪声检测,必须先缓存256×2+3个数据,采样模块才能开始获得3×3窗口内的图像数据。3个寄存器和1个FIFO缓存1行256个像素。所以每个寄存器存储1个像素,FIFO存储253个像素。通过采样窗口模块,可将图像数据由串行输入转变为并行3×3窗口输出,加快图像处理速度。本文使用的是Altera公司的FPGA芯片,可在Quartus软件中使用IP核,通过MegaWizard Plug-In Manager直接生成FIFO。

图2 采样窗口生成电路图

2.2行列计数器模块

在对一副灰度图像进行噪声检测和滤波处理的过程中,3×3的采样窗口不断向右滑动。采样窗口每当到达该行末端,采样窗口跳到下行始端。行列计数器模块通过行列计数功能来判断图像处理是否到达边缘或者处理完毕[5]。当采样窗口中心元素x22位于每行第一列和最后一列时,噪声检测模块失效。本文滤波算法对图像边界处的图像数据采取保留处理,即输出原值x22。

2.3噪声检测模块

噪声检测模块又分为求8位数中值模块、缓存模块和算法模块。为了算法模块中的噪声检测,要向算法模块中输入领域8位像素中值和采样窗口模块9个元素。

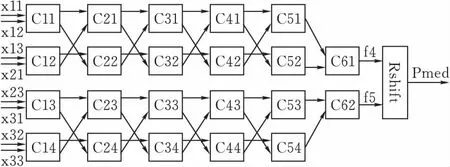

2.3.1领域8位中值模块运用文献[6]中排序网络理论 。如图3所示,首先将8位数分成两组,每组通过6个比较器生成有序序列,将所生成的两组有序序列利用合并网络,通过合并排序算法,可得到该8位数的按升序排列的有序序列。最后,将序列第4位和第5位数取平均值,即可得到该8位数中间值。为了节省FPGA资源,利用两位数之和右移一位操作完成两位数取平均。

图 3 领域8位中值模块

2.3.2缓存模块由图2可见,采样窗口输入像素与中值Pmed有7个时钟周期的延时。为了保证采样窗口输入像素与领域中值Pmed能在同一个周期中输入算法模块,采取对采样窗口输入像素缓存7个时钟周期输出到改进中值滤波算法模块中。

2.3.3算法模块将缓存模块缓存后的像素和领域8位中值模块的中值Pmed按本文改进滤波算法进行处理。利用改进滤波算法,对采样窗口的中心像素x22进行噪声检测。如果是噪声,则输出中值Pmed,否则输出原值x22。

3仿真实验

用Quartus11.0SP1在ALTERA的EP4CE15F23C8芯片里实现。布局布线仿真后,最高工作频率可达148 MHz。

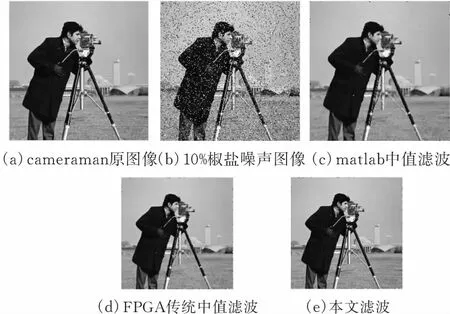

先用Matlab将分辨率为256×256 、8bit的图像转成256×256的灰度值矩阵。以16进制格式保存在“.txt”文档中。然后以灰度值矩阵为图像数据输入信号转化成Modelsim 6.6d的激励文件。经Modelsim 6.6d仿真测试结果保存为“.txt”格式,通过Matlab转换为图像显示。在256×256的cameraman图像中加入10%的椒盐噪声,经Matlab中值滤波,FPGA传统中值滤波和本文算法滤波处理后输出如图4所示。由实验结果比较分析知,Matlab中值滤波和FPGA传统中值滤波虽然可以滤波全部噪声,但是由于图像部分原值被中值代替,使图像变模糊。本文滤波算法处理后的图像,不但噪声已经全部滤除,而且图像细节保护得较好。

图 4 滤波算法仿真结果图片显示

4性能指标分析

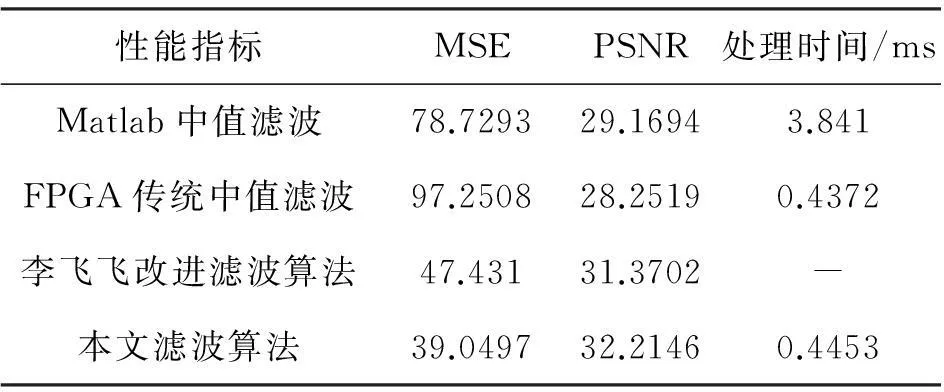

本文采用最小均方差MSE和峰值信噪比PSNR作为对椒盐噪声图像处理的性能指标。MSE值越小,PSNR值越大,图像处理的质量越高。

图像分辨率为M×N的最小均方误差的计算公式:

(1)

峰值信噪比的计算公式为:

(2)

式中,n为图像的深度。

对分辨率为256×256的Lena添加10%噪声密度,将本文滤波算法与Matlab中值滤波,FPGA传统中值滤波和李飞飞[3]改进滤波算法的性能比较(表1),本文滤波不但拥有最高的图像质量,而且保持着FPGA传统中值滤波的高效图像处理速度,约为Matlab中值滤波处理一帧图像速度的83倍。

表1 4种滤波算法性能比较

本文所用PC机为Intel Pentium G640 2.80 GHz 双核处理器

首先用Matlab对Lena图像添加不同密度的椒盐噪声;然后,分别用Matlab中值滤波、FPGA传统中值滤波和本文滤波算法,处理含不同密度噪声的Lena图像;最后用Matlab计算各个算法PSNR值。将这些数据用Word制作成折线图(图5)。对比分析知,在同一噪声密度的情况下,本文滤波算法图像处理后得到的PSNR值最大。

图 5 处理不同噪声密度Lena下各个滤波算法PSNR值比较

[1]王宇新,贺圆圆,郭禾,等.基于FPGA的快速中值滤波算法[J].计算机应用研究,2009,26(1):224-226.

[2]李新春,赵璐.基于中值滤波算法滤波器的FPGA实现[J].计算机系统应用,2011,20(9):82-85.

[3]李飞飞,刘伟宁,王艳华.改进的中值滤波算法及其FPGA快速实现[J].计算机工程,2009,34(14):175-177.

[4]李双全,张宇,孙广明.消除椒盐噪声的改进滤波算法[J].计算机工程,2008,34(10):171-175.

[5]张杰.基于FPGA的数字图像处理[D].武汉:武汉科技大学,2009.

[6]潘金贵,顾铁成,李成法,等.算法导论(第二版)[M].北京:机械工业出版社,2006,433-445.

[责任编校: 张众]

Improved Median Filtering Algorithm and Its Hardware Implementation of FPGA

PENG Jun, WEI Qiong, WANG Jun, TONG Minghao

(SchoolofMechanicalEngin.,HubeiUniv.ofTech.,Wuhan430068,China)

Abstract:In order to effectively suppress the noise pollution in the process of image acquisition and transmission, this paper presents an improved median filtering algorithm with noise detection module based on the median filtering. And it is implemented successfully in the FPGA hardware platform. It has improved the shortcoming that the traditional median filter will blur the image. The experimental results show that the proposed algorithm can not only suppress the noise effectively, but also save more details of the image, so as to improve the quality of image processing.

Keywords:FPGA; correlation of domain; noise pixel detection;median filtering

[收稿日期]2016-01-25

[作者简介]彭俊(1990-), 男, 湖北鄂州人,湖北工业大学硕士研究生,研究方向FPGA图像处理,机器人学

[通讯作者]王君(1977- ),男,湖北蕲春人,湖北工业大学教授,研究方向机器人学、先进制造技术与装备、新能源技术

[文章编号]1003-4684(2016)02-0042-03

[中图分类号]TP391

[文献标识码]:A