一种-100 dB电源抑制比的非带隙基准电压源

黄国城 尹 韬 朱渊明 许晓冬 张亚朝 杨海钢*(中国科学院电子学研究所北京100190)(中国科学院大学北京100049)

一种-100 dB电源抑制比的非带隙基准电压源

黄国城①②尹韬①朱渊明①②许晓冬①张亚朝①②杨海钢*①①

①(中国科学院电子学研究所北京100190)

②(中国科学院大学北京100049)

该文提出一种非带隙基准电路,通过一个带超级源极跟随器的预调制电路提供一个稳定的电压,为基准核心电路供电。超级源极跟随器通过降低基准核心电路电源端的对地阻抗,有效提高了基准电路的电源抑制能力。该基准电路采用0.35μm CMOS工艺设计并流片,测试结果表明,该电路的工作电源电压为1.8~5 V,静态电流约为13μA。低频处电源抑制比(PSRR)约等于-100 dB,在小于1 kHz频率范围内PSRR均优于-93 dB。并且其片上面积仅为0.013mm2。

CMOS基准电路;非带隙基准电路;预调制电路;超级源极跟随器;电源抑制比

1 引言

近年来,智能手机、掌上电脑、便携式影音设备以及医疗设备等消费类电子呈现不断增长的趋势。在为这些设备供电时,不论是开关电源还是线性电源,都必须经过电源管理模块输出稳定的供电电压,才能保证设备的功能和性能达到预期指标。基准电压源是电源管理以及一些数模混合电路中的关键模块,它的电源抑制比(Power Supply Rejection Ratio,PSRR)和温漂特性都将直接影响整体电路的性能。

传统的基准电压源采用由双极型晶体管实现的带隙基准电路,在集成电路工艺中,双极型晶体管可以直接采用双极型工艺产生[1],也可以由标准CMOS工艺中的寄生三极管产生[27]-。相对于双极型工艺,CMOS工艺具有静态功耗低、电源电压适用范围广以及掩膜层数少等优点,因此在集成电路领域得到了广泛应用。为了兼容CMOS工艺以及降低制造成本,无三极管的非带隙基准电压电路得到了广泛的研究[816]-。文献[2]提出一种提高PSRR的自调制电路,但是由于采用了三极管产生带隙基准,整体电路的电源电压以及静态功耗都相对较大,同时耗费的面积也较大。文献[9]提出了一种基于饱和区的PMOS管和NMOS管的栅源电压权重差的基准电压,电路结构简单,但是PSRR只有-47 dB。在电源管理芯片如低压差线性稳压器(LDO)中,输出电压的PSRR是一个重要的参数。由于LDO的输出电压与基准电压是比例关系,意味着LDO的输出电压的PSRR比基准电压PSRR少几个dB。一般来说LDO的输出电压PSRR也将受到限制[17]。因此,基准电压的PSRR会影响LDO输出电压的PSRR能达到的上限。本文针对以上所述问题,提出一种高电源抑制比的非带隙基准电路,并采用G lobal Found ry 0.35μm CMOS工艺进行流片以及测试,测试结果表明,该电路在扩大电源电压适用范围(1.8~5 V)、减少静态功耗(13μA)的同时,低频处PSRR达到了约-100 dB,在小于1 kHz频率范围内PSRR均优于-93 dB,30MHz频率范围内的PSRR优于-40 dB。在0ºC~100ºC范围内温漂为160 ppm/ºC,片上有效面积仅为0.013mm2。

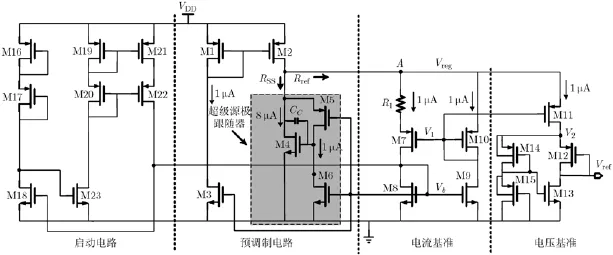

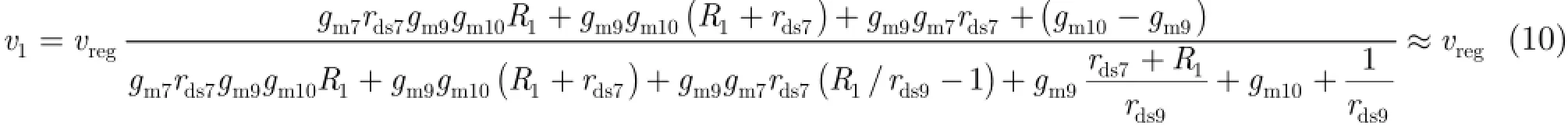

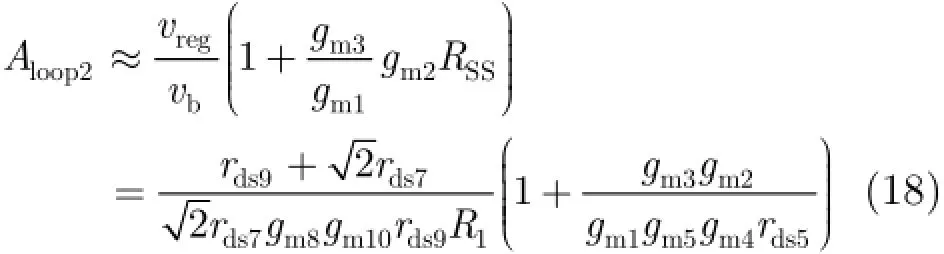

图1 非带隙电压基准电路图

2 电路结构与分析

图1为整体电路图,包括启动电路、预调制电路、电流基准以及电压基准电路;整个电路结构不包含运放和三极管,因此能有效减少静态功耗。采用包含超级源极跟随器的预调制电路模块,其目的是为了有效提高电源抑制比。

2.1非带隙基准电压源电路结构

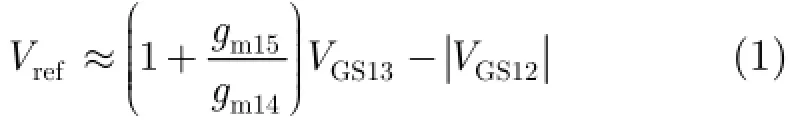

电压基准电路由M 12~M 15构成,M 14和M 15采用二极管连接的形式,M 13的栅极电压由M 14和M 15的分压产生,通过M 12~M 15的连接关系,基准电压Vref可用式(1)表示。其中,GS12V和GS13V分别为M 12和M 13的栅源电压,和分别为M 14和M 15的跨导。由于M 14和M 15的电流相等,可以调整M 14和M 15的宽长比,达到控制m14g和m15g的值。之所以采用二极管连接的形式,而没有采用电阻分压的方式,是为了减少面积的开销。流过M 14和M 12的电流分别为200 nA和800 nA,如果采用电阻分压的方式,大约需要7.5 MΩ的片上电阻(V2结点电压为2VGSP,约等于1.5 V)。

M 12和M 13都工作在饱和区,由MOS管平方律公式[1]可以得出,其中为阈值电压,μ为载流子迁移率,OXC为栅极氧化层电容密度。假设漏极电流I一定,栅源电压与阈值电压成正比的关系,M 12和M 13分别为PMOS管和NMOS管,如果二者的阈值电压和载流子迁移率的温度特性呈现一定的关系,则将有可能在某温度下获得零温度系数。

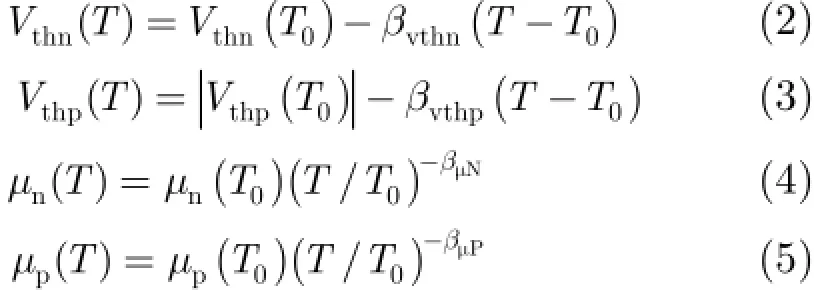

NMOS管和PMOS的阈值电压与温度成线性关系,载流子迁移率则是温度的指数函数,这两个参数分别可分别表示为[18]

其中,thnV,thpV,nμ,pμ,vthnβ,vthpβ,Nβμ,Pβμ分别为NMOS和PMOS管的阈值电压和迁移率以及它们的温度系数,0T为参考温度。

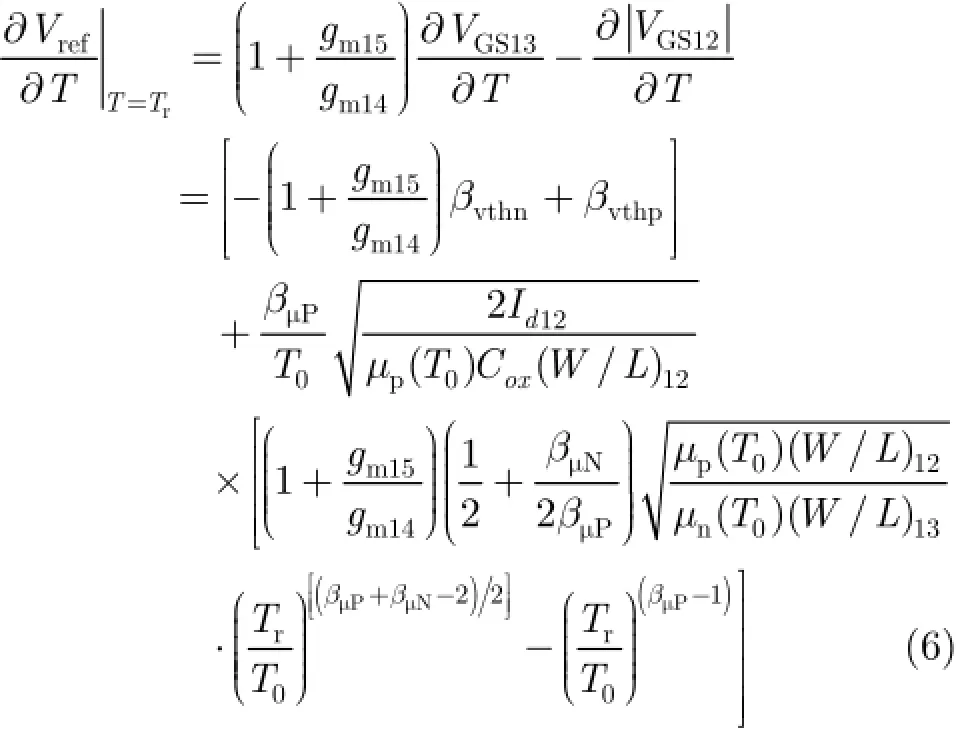

将式(1)对温度T求导并令其在室温rT下等于0,并代入式(2)~式(5),得到式(6)[9]:

令相加的两项各等于0,得到在室温下取得零温度系数的条件为

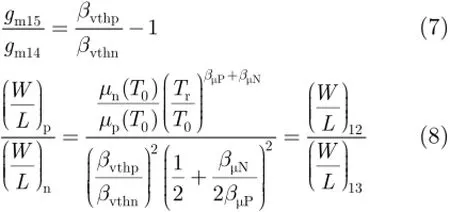

对于G lobal Found ry 0.35μm CMOS工艺来说,NMOS管和PMOS管的阈值电压和迁移率的温度特性仿真如图2所示。

图2 Global Found ry 0.35μm CMOS工艺下阈值电压和迁移率的温度特性

2.2预调制电路以及PSRR分析

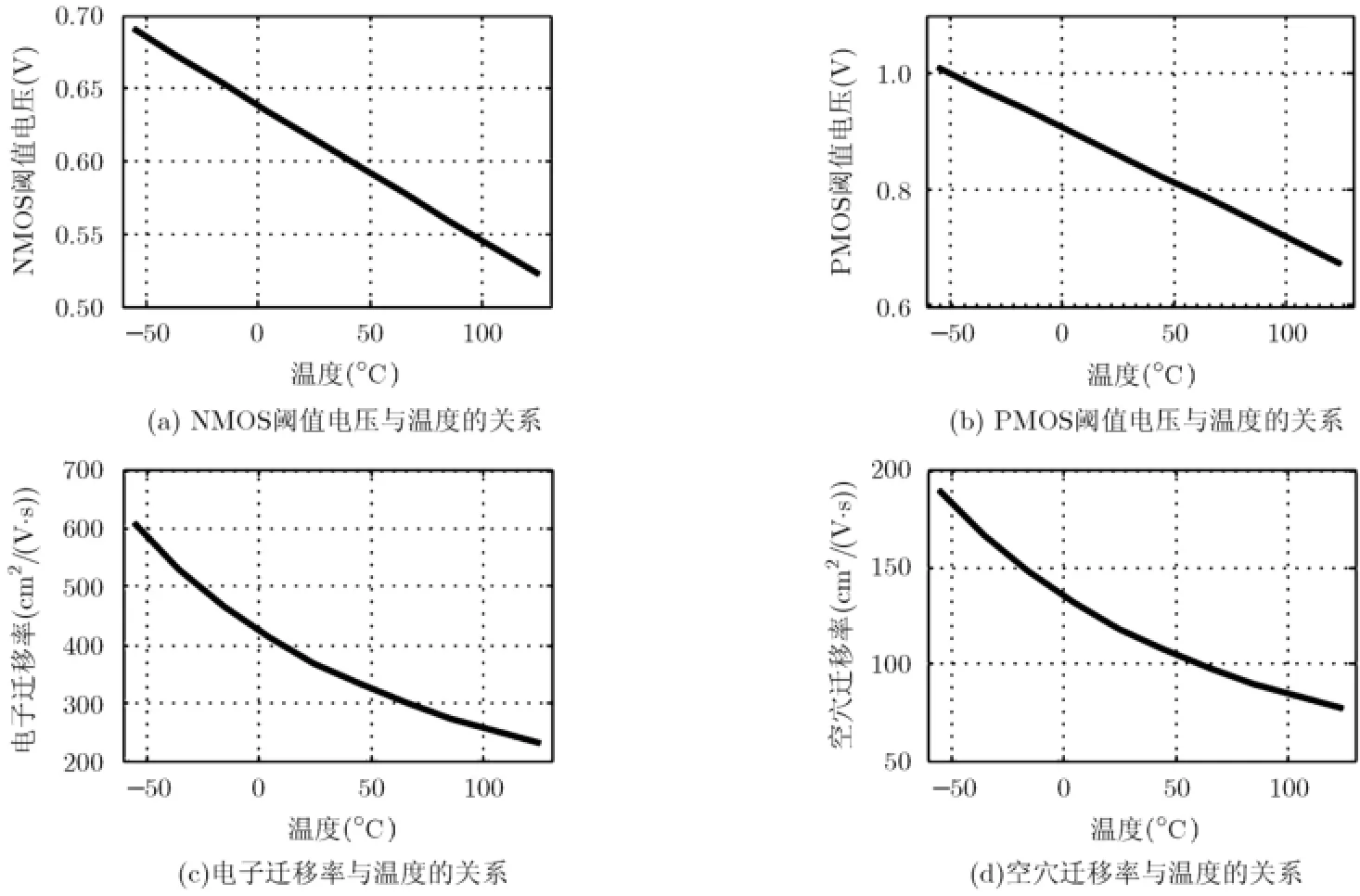

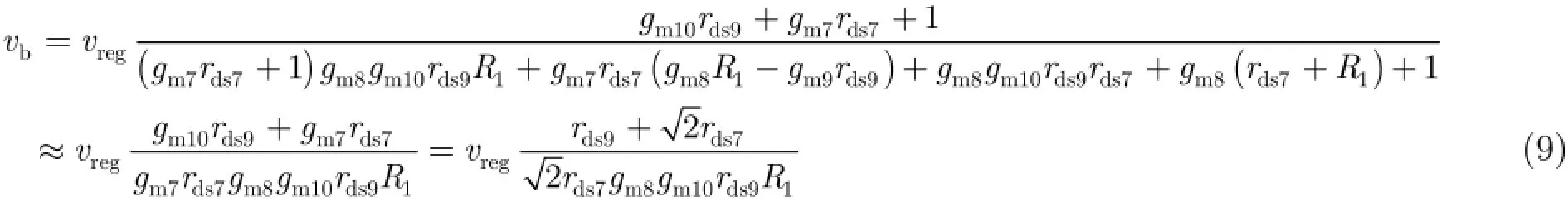

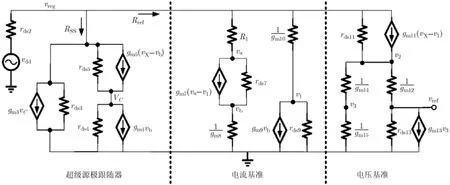

为了增强电源抑制能力,电路中增加了预调制电路[2,5],给基准电路提供一个较稳定的供电电压,如图1中的A结点电压Vreg。本文采用的预调制电路由一对电流镜和一个超级源极跟随器(super source follower)模块[1]组成。超级源极跟随器由M 4~M 6组成,其在普通源极跟随器(M 5和M 6)的基础上加了一个内部负反馈(M 4),通过M 4的负反馈作用,使得从M 5源极往GND看的阻抗RSS下降,从而减少了由M 2漏极看向基准核心电路的阻抗。从直观上理解,由于电阻分压原理,预调制电压Vreg具备了一定的电源抑制能力,从而提高了基准输出电压Vref的PSRR。基准核心电路的小信号分析模型如图3所示,其中v表示小信号电压,V表示大信号电压。通过基尔霍夫定律,并忽略体效应,可以求得bv和1v的表达式为

其中,gm7~gm15和rds7~rds15分别为M 7~M 15的跨导值和小信号漏源电阻。电流基准电路的M 7和M 10的尺寸之比为2:1,由于两者电流相等,其跨导之比为在式(9)和式(10)的分母中,远大于其它项时,等式约成立。可以看出,在M 7~M 10的栅长取值较大时,v1约等于vreg。

图3 非带隙基准电路的小信号分析模型

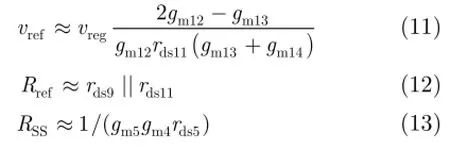

从预调制点(Vreg)看向电流和电压基准电路的输入阻抗为Rref,看向超级源极跟随器的输入阻抗为RSS。将式(9)和式(10)代入图3的小信号模型重新计算,可得Vref,Rref以及RSS可表示为

其中gm4和gm5为M 4和M 5的跨导值,rds5为M 5的漏源电阻,在没有M 4的情况下,RSS的值为1/gm5。式(13)表明,M 4的反馈作用,使得RSS的值减少为原来的gm4rds5倍。对比式(12)和式(13)可以看出,RSS的数值远小于Rref,即VDD对Vreg的波动影响大部分被超级源极跟随器吸收了。Vreg处的PSRR表达式为

其中,为减小沟道长度调制效应,预调制电路中的电流镜M 1~M 2的栅长取值也较大,使得M 1的栅极小信号电压接近ddv,从而M 1和M 2的电流就受VDD的影响就更小。将式(14)代入式(11)可得Vref的 PSRR表达式:

从式(11),式(14)和式(15)可以看出,加了预调制电路之后,基准电压的PSRR优化了约倍,而最小电压取值只在原来的基础上增加了一个晶体管的漏源电压(Vds2)。

为了避免基准电路进入“简并”的偏置状态,需要给基准电路加入启动电路。启动电路由M 16~M 22组成,如图1所示。在刚上电时,电流基准电路的M 8的栅极电压Vb还处于0电位,M 18为截止状态,M 16和M 17导通。从而M 23也处于导通状态,M 19~M 22构成的cascode电流镜流过电流向Vb点充电。当Vb点电压高于M 3的阈值电压时,M 1和M 2开始流过电流为预调制点Vreg充电,电流基准电路也开始启动。由于M 18的宽长比设置较大,当启动稳定之后,Vb处于NMOS管阈值电压的状态,使得M 18进入线性区。M 18的漏极接近0电位,从而M 23截止。M 19~M 22的电流消失,启动电路停止动作,不影响基准电路的正常工作。

2.3环路稳定性分析

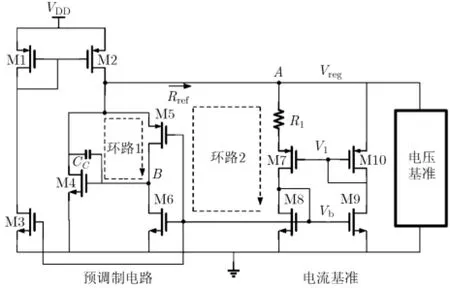

图1电路的环路分析如图4所示,主要有两个主要的环路,环路1是超级源极跟随器引入M 4形成的环路,环路2是预调制电路与电流基准电路形成的环路。

首先分析环路1的稳定性。环路1可以分为两级,第1级为从M 5源极到M 4的栅极。从M 5源极到M 4栅极有两条支路,一条是“M 5源极-B点”,另一条是“A点-R1-M 7-Vb-M 6-B点”这条支路,但是从式(9)可以看出从A点(Vreg)到Vb的增益远小于1,因此只考虑M 5的作用。环路1的第2级为从M 4的栅极到M 5的源极。由于M 4和M 5流过电流分别为8μA和1μA,并且M 4的栅长取值比M 5和M 6的栅长小,M 5和M 6的漏极(B点)相对M 4的漏极为高阻结点,因此取B点为主极点。采用CC跨接在第2级上,作用密勒补偿,提高环路的稳定性。CC采用poly电容实现,大小约为750 fF(20×30 μm2)。结合图4以及图3的小信号分析图,忽略体效应,可以求得环路1的环路增益和主极点为

接下来分析环路2的稳定性。环路2也存在两条支路,第1条支路为“Vb-M 5-A点”,第2支路为“Vb-M 3-M 2-A点”,第1条支路为超级源极跟随器,Vb到A点的增益约等于1;第2条支路中Vb到A点的增益约为通过式(9)可以计算出环路2的环路增益为

假设ds9r和ds7r为同一量级,且于是有,意味着从两条支路去推断环路2为正反馈,但是由于其环路增益远小于1,不会对稳定性造成影响。

图4 基准电路的环路分析

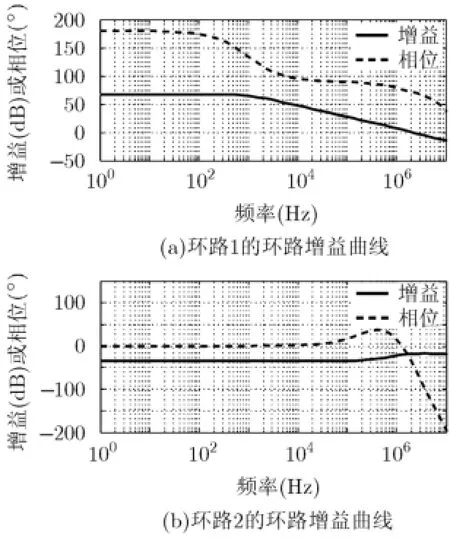

图4中的两个环路的环路增益的仿真曲线如图5所示,图5(a)表示环路1的环路增益,从图中可以看出,环路1的直流增益约为67 dB,相位裕度约为72º。图5(b)表示环路2的环路增益,虽然是正反馈,但是其增益总是远小于1,因此不会产生稳定性的问题。从图5的仿真可以看出,整个电路系统中包含的两个主要环路均为稳定状态,因此整个系统也是稳定的。

图5 基准电路中两个环路的环路增益曲线

3 测试结果与分析

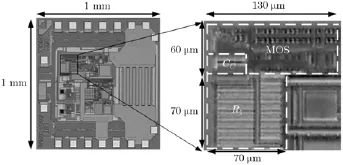

本文所设计的非带隙基准电路采用G lobal Foundry 0.35μm CMOS工艺设计实现并流片验证。图6为基准电路的显微照片,已应用于一款LDO电路当中。基准电路的有效面积为0.013mm2。实验采用Agilent E3661A电源、E34401A数字万用表以及E5061B矢量网络分析仪等仪器对芯片进行测试。

图6 应用于LDO中的非带隙基准电路显微照片

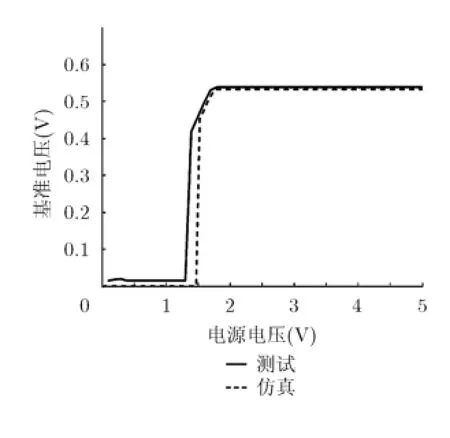

基准电压输出特性的仿真与测试曲线如图7所示,实线和虚线分别为测试和仿真曲线,输出特性的仿真和测试曲线比较吻合。从图中可以看出基准电路正常工作的最小电压约为1.8 V。电源电压VDD从2~5V变化时,输出电压变化约40μV。线性调整率(Line Regulation)约为13μV/V,即24.2 ppm /V。室温条件下,基准电路的静态电流约为13μA。

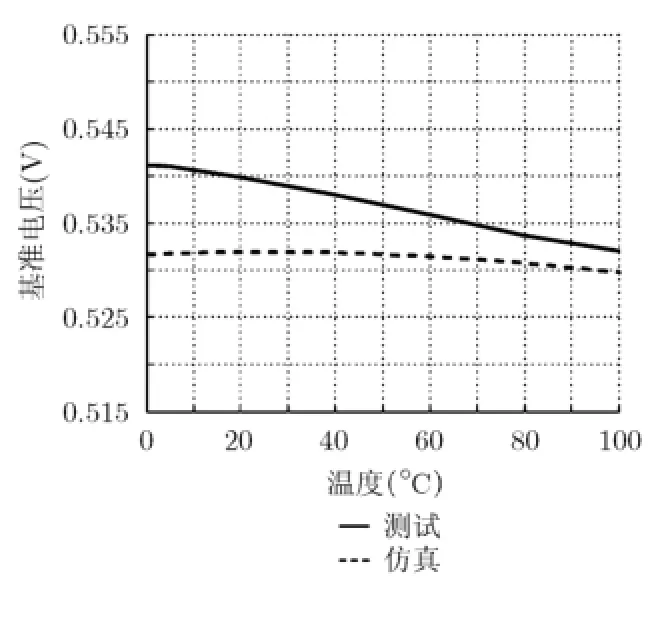

图8为基准电路温度特性的典型工艺角(Typical NMOS and Typical PMOS Corner,TT corner)仿真与实际测试曲线比较图,在0ºC~100ºC范围内,测试的输出变化值约为8.25 m V,温漂系数约为160 ppm/ºC,由于实际芯片制造工艺误差,尤其是掺杂浓度和晶体管尺寸的不匹配,由于设计的经验不足,芯片没有采用片外的补偿(trimm ing),但是TT corner的仿真结果是不错的,温漂系数为39.4 ppm/ºC。

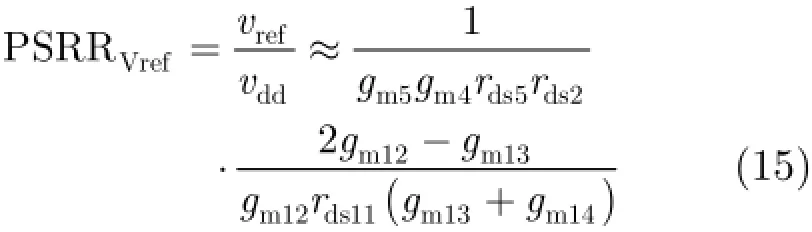

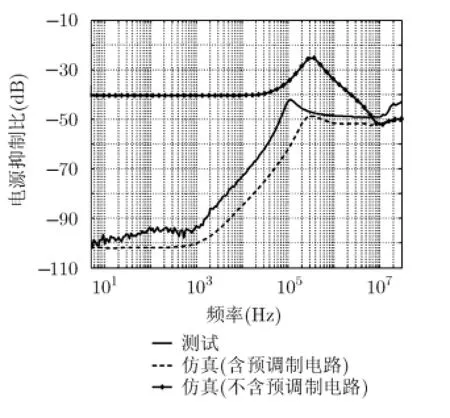

PSRR的仿真和测试曲线如图9所示。图9的仿真曲线有两条,其中一条为不包含预调制电路的仿真曲线,另一条是包含预调制电路的仿真曲线。从仿真的结果可以看出,加入本文提出的带超级源极跟随器的预调制电路之后,低频处的PSRR提高了接近62 dB。

图7 基准电压输出仿真与测试结果对比

图8 电压基准的温度特性测试与仿真结果对比

图9 电源抑制比的测试和仿真结果对比

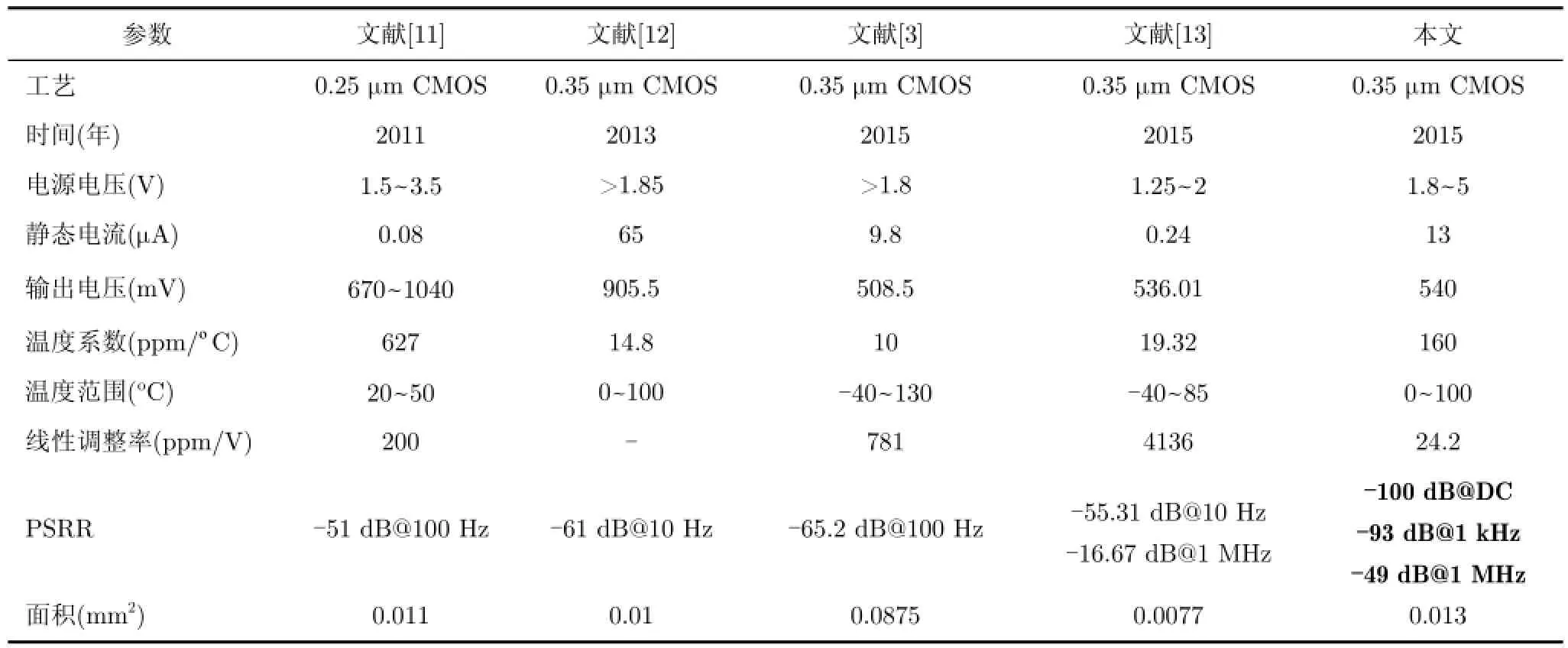

表1 芯片测试结果对比

同时,对比图9中的测试和仿真曲线可以看出,在低频处仿真和测试的PSRR非常接近,约为-100 dB。在小于1 kHz的频率范围内,PSRR优于-93 dB;并且,在仪器可测的的频率范围内,PSRR均优于-40 dB。在1~100 kHz的频率范围,测试的PSRR比仿真结果要差10 dB左右,这可能是由于在实际的芯片中,从VDD到预调制点的寄生电容大于仿真值,导致从电源的高频噪声更容易耦合到预调制点。在100 kHz以上的频率范围,基准电路的内部环路失效,此范围的PSRR取决于VDD到输出端的寄生电容与输出端到地的寄生电容的电抗之比,受频率变化的影响较小。表1为本文的基准源电路与近年文献的对比,本文电路在PSRR以及线性调整率等方面具备一定优势。

4 结论

本文提出一种非带隙基准电路,包含一种新颖的带超级源极跟随器的预调制电路,为核心基准电路提供稳定的供电电压,有效提高了输出电压的电源抑制比。该基准电路已经通过0.35μm CMOS工艺流片验证,室温下,整个基准电路的静态电流仅13 μA。测试结果显示,在低频处的PSRR达到了-100 dB,在小于30 MHz的频率范围内,PSRR均优于-40 dB。并且,电源电压在2~5 V变化时,线性调整率约为24.2 ppm/V。该基准电路已经应用于一款LDO芯片当中,为其提供高PSRR的基准电压。

[1]GRAY P R,HURST P,MEYER R G,et al.Analysis and Design of Analog Integrated Circuits[M].New Jersey,USA. W iley,1990:201-300.

[2]ZHU Y,LIU F,YANG Y,et al.A-115 dB PSRR CMOS bandgap reference with a novel voltage self-regulating technique[C].2014 IEEE Proceedingsof theCustom Integrated Circuits Conference(CICC),San Jose,CA,USA,2014:1-4. doi:10.1109/CICC.2014.6946006.

[3]BASYURT P B and AKSIN D Y.A com pact curvature corrected bandgap reference in 0.35μm CMOS process[J]. Analog Integrated Circuits and Signal Processing,2015,83(1): 65-73.doi:10.1007/s10470-015-0503-5.

[4]WANG B,LAW M K,and BERMAK A.A precision CMOS voltage referenceexploiting silicon bandgap narrowing effect[J]. IEEE Transactions on Electron Devices,2015,62(7): 2128-2135.doi:10.1109/TED.2015.2434495.

[5]CHAHARDORIM,ATAROD IM,and SHARIFKHANIM.A sub 1V high PSRR CMOS bandgap voltage reference[J]. M icroelectronics Journal,2011,42(9):1057-1065.doi: 10.1016/j.mejo.2011.06.010.

[6]CAIC,SONG SX,LUO Y,et al.A high accuracy low-power bandgap voltage referencew ith trimm ing[C].2014 12th IEEE International Conference on Solid-State and Integrated Circuit Technology(ICSICT),Guilin,China.2014:1-4.doi: 10.1109/ICSICT.2014.7021565.

[7]LAM Y H and KIW H.CMOS bandgap referencesw ith selfbiased symmetrically m atched cu rrent-voltage m irror and extension of sub-1-V design[J].IEEE Transactions on Very Large Scale In tegration(VLSI)System s,2010,18(6):857-865. doi:10.1109/TVLSI.2009.2016204.

[8]COLOMBO D M,W IRTH G,and BAMPI S.Sub-1 V band-gap based and MOS threshold-voltage based voltage references in 0.13μm CMOS[J].Analog Integrated Circuitsand Signal Processing,2015,82(1):25-37.doi:10.1007/ s10470-014-0343-8.

[9]LEUNG K N and MOK P K T.A CMOS voltage reference based on weighted VGSfor CMOS low-dropout linear regulators[J].IEEE JournalofSolid-State Circuits,2003,38(1): 146-150.doi:10.1109/JSSC.2002.806265.

[10]CAJUEIRO JP C.Tracking-Vgs:a temperature com pensation technique to imp lem ent all-MOS reference voltages[C]. Proceedings of the 6th International Caribbean Conference on Devices,Circuits and System s,Playa del Carm en,México,2006:287-291.doi:10.1109/ICCDCS.2006.250875.

[11]CHANG S I,ALASHMOUNY K,and YOON E.A 1.5 V 120 nW CMOS programmablemonolithic reference generator for w ireless im plantable system[C].2011 Annual International Conference of the Engineering in Medicine and Biology Society(EMBC),Boston,MA,USA,2011:2981-2984.doi: 10.1109/IEMBS.2011.6090818.

[12]ZHOU Z,ZHU P,SHIY,et al.A resistorless CMOS voltage reference based on mutual com pensation of VTand VTH[J]. IEEE Transactions on Circuitsand System s II:Express Briefs,2013,60(9):582-586.doi:10.1109/TCSII.2013.2268639.

[13]CHOUHAN S S and HALONEN K.Design and im p lementation of a m icro-power CMOS voltage reference circuit based on therm al compensation of Vgs[J]. M icroelectronics Journal,2015,46(1):36-42.doi: 10.1016/j.mejo.2014.09.015.

[14]CHOUHAN S S and HALONEN K.Design and im plementation of all MOS m icro-power voltage reference circuit[J].Analog Integrated Circuits and Signal Processing,2014,80(3):399-406.doi:10.1007/s10470-014-0361-6.

[15]CHOUHAN SSand HALONEN K.A simple allMOS voltage reference for RFID applications[C].2013 IEEE NORCHIP Conference,Vilnius,Lithuania,2013:1-3.doi: 10.1109/NORCHIP.2013.6702027.

[16]ROH H D,ROH J,and DUAN D Q Z.A ll mos transistors bandgap reference using chopper stabilization technique[C]. 2010 International SoC Design Conference(ISOCC),Incheon,South Korea,2010:353-357.doi:10.1109/SOCDC.2010. 5682897.

[17]TAN X L,CHONG SS,CHAN P K,et al.A LDO regulator w ith weighted current feedback technique for 0.47 nF-10 nF capacitive load[J].IEEE Journal of Solid-State Circuits,2014,49(11):2658-2672.doi:10.1109/JSSC.2014.2346762.

[18]FILANOVSKY IM and ALLAM A.Mutual compensation of mobility and threshold voltage tem perature effects w ith app lication in CMOS circuits[J].IEEE Journal of So lid-State Circuits,2001,48(7):876-884.doi:10.1109/81.933328.

黄国城:男,1989年生,博士生,研究方向为低功耗低噪声模拟集成电路设计.

尹韬:男,1980年生,副研究员,主要研究方向为微弱信号检测集成电路设计、高速接口集成电路设计.

朱渊明:男,1989年生,硕士,主要研究方向为高速模数转换、可编程逻辑芯片设计.

许晓冬:男,1985年生,助理研究员,主要研究方向为CMOS射频电路、高速接口芯片设计.

张亚朝:男,1988年生,硕士生,研究方向为微弱信号检测、可编程模拟阵列芯片设计.

杨海钢:男,1960年生,研究员,主要研究方向为大规模可编程逻辑芯片设计和智能信息获取、处理与传输集成化芯片系统.

A-100 dB Power Supply Rejection Ratio Non-bandgap Voltage Reference

HUANG Guocheng①②YIN Tao①ZHU Yuanm ing①②XU Xiaodong①ZHANG Yachao①②YANG Haigang①①

①(Institute of Electronics,Chinese Academ y of Sciences,Beijing 100190,China)

②(University of the Chinese Academy ofSciences,Beijing 100049,China)

Thispaper p resents a non-bandgap voltage reference,which contains a pre-regulated circuit with a super source follower.The p re-regulated circuit includes a super source follower,which attenuates the im pedance from the supply of the core reference circuit to ground.In thisway,the p re-regu lated circuit provides a relative stab le voltage for the core reference circuit,im proving the Power Supp ly Rejection Ratio(PSRR)of the ou tpu t voltage of the reference.The proposed reference circuit is im plemented in standard 0.35μm CMOS p rocess.Measured results show that the supply range is from 1.8 to 5 V and the quiescent current is on ly about 13μA at room tem perature. The PSRR at low frequency achieves-100 dB and the PSRR below 1 kHz is better than-93 dB.The active area of the p roposed reference is only 0.013mm2.

CMOS reference circuit;Non-bandgap reference circuit;Pre-regu lated circuit;Super source follower;Power Supp ly Rejection Ratio(PSRR)

s:The National Natural Science Foundation of China(61474120),The National Key Basic Research P rogram of China(2014CB 744600)

TN 402

A

1009-5896(2016)08-2122-07

10.11999/JEIT 151256

2015-11-09;改回日期:2016-03-25;网络出版:2016-05-09

杨海钢yanghg@m ail.ie.ac.cn

国家自然科学基金(61474120),国家重点基础研究发展计划(2014CB 744600)