厚膜混合微电子芯片共晶焊工艺研究

李 波,夏俊生,李寿胜

(北方通用电子集团有限公司214所 微电子部,安徽 蚌埠 233042)

厚膜混合微电子芯片共晶焊工艺研究

李波,夏俊生,李寿胜

(北方通用电子集团有限公司214所 微电子部,安徽 蚌埠 233042)

为满足散热和封装内部气氛控制要求,厚膜混合微电子多采用芯片共晶焊工艺。采用分组试验的方法,通过内部气氛检测、X射线照相等试验手段,得到了共晶焊工艺中的关键工艺方案。

厚膜混合微电子;共晶焊;内部气氛检测;X射线照相;工艺方案

高功率和高可靠性是厚膜混合微电子电路的2个重要发展方向,高功率电路要求功率器件粘接达到较低热阻,而以某“航天专项工程电子元器件标准要求”为代表的高可靠标准,则要求在125 ℃、1 000 h的稳态寿命试验后,空腔内部主要气氛指标要达到氮气含量≥98%、水汽含量≤3 000 mg/L、氧气含量≤2 000 mg/L以及二氧化碳含量≤2 000 mg/L。这2个方向决定了应采用共晶焊工艺替代传统的环氧树脂粘接工艺。

对于2种或2种以上金属构成的二元或多元合金(通常是二元或三元),其单种金属的熔点可能很高,但不同金属按一定比例配比所形成合金的熔点却可以明显降低,这时的合金则称为共晶合金[1],利用共晶合金将多个裸芯片焊接到同一个厚膜混合电路基板上,称为多芯片共晶。对共晶焊可靠性验证最常见的方式是通过X射线照相检查,检查芯片底部未焊接面积与芯片面积的比值,称为空洞率检查,常规电路空洞率一般要求<50%,某“航天专项工程电子元器件标准要求”则要求<25%。

共晶焊一般按照助焊剂的添加,分为有助焊剂共晶焊和无助焊剂共晶焊,下述将对这2方面进行工艺可靠性研究。

1 有助焊剂共晶焊工艺研究

1.1有助焊剂共晶焊试验

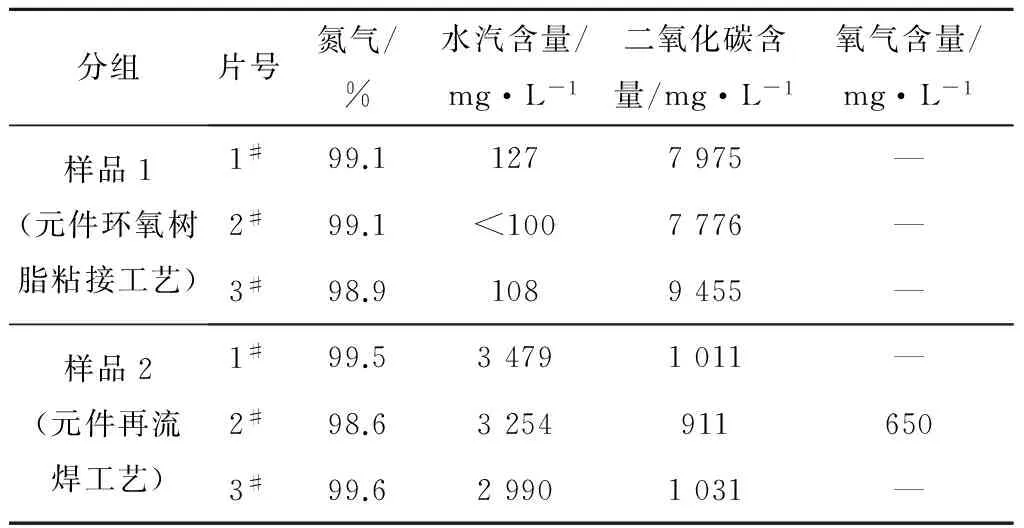

有助焊剂方式共晶焊的工艺特点是在厚膜基板焊接区加上带有助焊剂的焊料片后,贴放电路芯片,通过回流或再流等方法完成焊接,最后完成助焊剂清洗。组装电路在经过125 ℃、1 000 h的稳态寿命试验后,内部气氛检测,二氧化碳含量较同结构、筛选和试验条件下的环氧树脂粘接工艺有显著下降,满足二氧化碳含量≤2 000 mg/L的要求,但水汽含量不满足3 000 mg/L的要求(针对某电路主要气氛检测指标对比见表1)。

表1 环氧粘接、有助焊剂共晶芯片空腔内部水汽含量对比表

1.2有助焊剂共晶焊试验分析

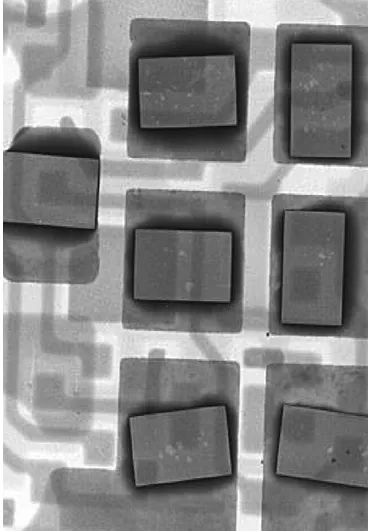

金属焊接替代环氧树脂粘接有效地降低了二氧化碳的含量,主要得益于禁用了含碳有机高分子材料,焊接电路内部气氛水汽含量较高,主要缘于空洞率高及焊接致密度低,通过X射线照相检查,此工艺空洞率一般>50%(见图1a),通过机械方法剥离芯片,高倍放大,可见焊接面有较大的焊接空洞及孔洞(见图1b),电路内部的空洞及孔洞残留了较多水汽,并在长时间高温老炼、寿命试验等过程中缓慢释放出来。焊接空洞或孔洞与助焊剂有直接关系,为保证低水汽含量、低空洞率的高可靠焊接要求,应采用无助焊剂共晶焊工艺。

图1 芯片有助焊剂共晶空洞或孔洞情况

2 无助焊剂共晶焊工艺研究

无助焊剂的共晶焊方法主要分为两大类:1)加压法共晶,一般采用石墨夹具定位厚膜基板和元件,金属压块实现焊接压力,有效控制真空/气氛炉内气氛,通过预热、排气、真空、加温、降温和进气等过程,实现共晶全过程;2)擦动法共晶,采用镊子或吸刀夹持元件,在焊接温度下,使芯片在基板表面焊区(已加焊料片)做相对摩擦,实现气氛和氧化物排出,达到低空洞率焊接。无论是哪种焊接方式,下述几个方面的工艺控制都极为重要:1)芯片背面金属化层;2)基板焊区金属化层;3)焊接压力(主要针对加压法共晶);4)焊接气氛、焊接温度及焊接时间。

2.1芯片背面金属化层影响研究

2.1.1芯片背金共晶试验

采用焊料共晶时,裸芯片背面需要金属化(简称背金)。金属化层分为单层金和多层金,单层金一般是在芯片背面溅射一层金或银,单层金因在焊接时很容易被含金或银焊料融蚀(俗称“吃金”),而导致芯片脱落,单层金芯片一般只适合环氧树脂粘接工艺。而焊接芯片背面一般溅射多层金,常见的镀层有(从内到外)钛镍银(TiNiAg)、钛镍金(TiNiAu)等,钛起到过渡作用,镍层起焊接作用,而金或银层则起防止镍层氧化的保护作用。作为焊接层的镍层有着至关重要的作用,其厚度直接影响着焊接空洞率,随着焊接芯片的尺寸大小,对镍层的厚度要求也不相同,一般芯片越大,镀层要求越厚,芯片越小,则镀层要求越薄。以常规尺寸2 mm×1 mm的芯片为例,在焊接工艺过程条件相同情况下,分组进行芯片镀层(TiNiAg)厚度与空洞率的对比试验研究,结果见表2,X射线照相图片如图2所示。

2.1.2芯片背金共晶试验分析

在共晶时,熔融焊料首先熔掉芯片背面薄银层或薄金层,后与焊接层镍层焊接到一起。通过上述对比可知,当镍层厚度较小时,熔融焊料易从芯片边缘开始“吃”掉芯片镍层,形成从外到内的焊接空洞,之所以从外到内部,是由于共晶时芯片四周界的焊料量要远多于芯片底部,熔融能力要比芯片底部中心更强。

表2 不同镍层厚度共晶焊对比试验

a)镍层厚度0.1 μm b)镍层厚度0.15 μm

c)镍层厚度0.2 μm

2.1.3工艺参数选用

通过上述试验及分析可知,对于混合电路常规尺寸的多芯片共晶,最可靠的镍层厚度不应<0.2 μm。反之,也可通过芯片空洞大小及分布情况,来判断背金工艺中镍层的厚度是否满足共晶可靠性要求。

2.2基板焊区金属化层影响研究

2.2.1基板焊区金属化层共晶试验

相对于裸芯片溅射方式背金不同,厚膜混合电路一般采用丝网印刷的方式在陶瓷、氮化铝等基板表面沉积一层金属化层焊区,常见的焊区金属层有金、银和铂银等,一般单纯的金属层不适合焊接,因焊接过程中很容易被焊料熔融掉,因而基板焊区常选择掺杂阻焊金属,如铂银,但这类金属层的焊区厚度也至关重要。以不同厚度的铂银焊区为例,在共晶工艺过程条件相同情况下,进行金属层厚度与空洞率对比试验研究,结果见表3,X射线照相图片如图3所示。

表3 不同铂银厚度共晶焊对比试验

a)铂银厚度6 μm b)铂银厚度10 μm

c)铂银厚度15 μm

2.2.2基板焊区金属化共晶试验分析

通过机械方法剥离芯片,可见基片焊区空洞区域的铂银金属层已被熔融掉。由焊前焊区膜厚测量曲线(见图4),可见其近似于盆型曲线,说明焊区周界厚度最高,中心厚度最薄(这也是丝网印刷的特点),因此,共晶时熔融焊料容易从焊区中心最薄的地方熔掉铂银层,形成上述空洞,其特点是在焊接区中心区域,近似圆形,随着焊接时间或温度的增加,有向周界扩大的趋势。

图4 基板焊区膜厚测量曲线图

2.2.3工艺参数选用

通过上述对比分析可知,芯片共晶焊时基板焊区应选择带有阻焊的金属层,同时焊区最小膜层厚应>15 μm。

2.3共晶焊压力影响研究

2.3.1焊接压力共晶试验

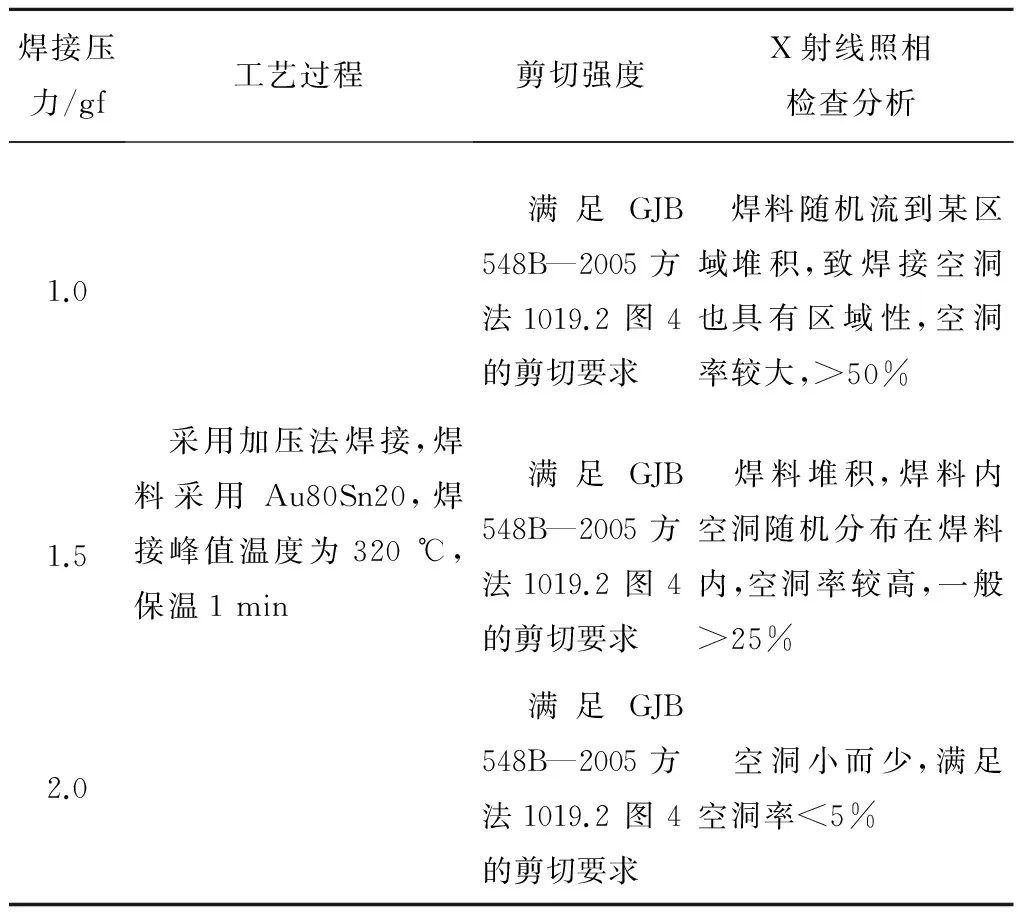

共晶过程焊接压力控制也非常重要,适当的压力施加到芯片背面、焊料片及基板焊接区,能增加焊料浸润性、减少焊接空洞及保证焊接平整度。本文对2 mm×2 mm芯片进行共晶,考察不同焊接压力下的焊接空洞率,结果见表4,X射线照相图片如图5所示。

表4 不同共晶压力条件下对比试验

a)焊接压力1.0 gf b)焊接压力1.5 gf

c)焊接压力2.0 gf

2.3.2焊接压力共晶试验分析

在压力不足时,共晶时熔融焊料随机停留在某个区域,随着压力逐渐增加,焊料受压后基本均匀分布到芯片底部,并通过挤压逐渐排除随机分布的空洞。

2.3.3工艺参数选用

通过对比试验研究可知,共晶焊接要达到理想的焊接效果,一般被焊接物体每平方毫米需施加0.5 gf以上的压力,同时应注意,施加的压力不应损伤芯片本身。

2.4焊接气氛、焊接温度及焊接时间研究

对于无助焊剂共晶焊,气氛保护尤为重要。在共晶时,如果惰性气氛不纯,混入氧气,当焊料熔融后,很快在其表面形成氧化膜,使焊料由于表面张力而缩成球状,严重影响焊料与焊接体的浸润效果,并大量增加焊接空洞率,甚至无法焊接。

对于焊接温度及焊接时间,焊接温度过高,焊接时间过长均可加速上述焊接空洞出现。一般而言,共晶炉设定的焊接温度比焊料合金的共融温度要高30~50 ℃,但在满足焊接可靠性的情况下,焊接温度越低越好,焊接时间则越短越好。对于擦动法多芯片共晶,应依次完成所有芯片共晶,焊接总时间应控制好,避免当最后一个芯片完成后,第1个芯片因焊料长时间熔融芯片镀层或基片金属层而脱落.时间控制是多芯片共晶的难点,根据测试,采用Au80Sn20焊料共晶,总峰值焊接时间应严格控制在3 min以内。

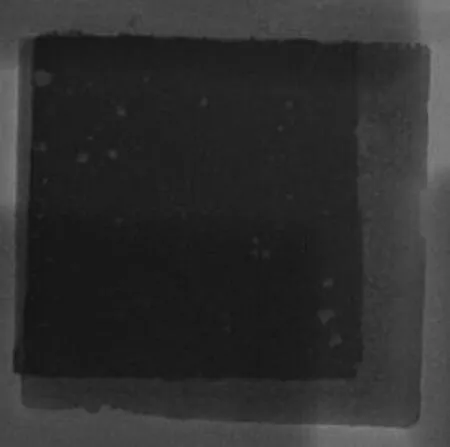

3 工艺方案实施

在上述结构的电路中,根据其特点,采用无助焊剂、加压法共晶焊方案。工艺参数为芯片背金镍层为2.0 μm,基板焊区最小铂银膜层为18 μm,每平方毫米共晶焊接压力达到0.5 gf以上。经过X光照相检测,多芯片共晶空洞率<25%,机械剥离芯片,目检焊料无细小孔洞(见图6)。电路经125 ℃、1 000 h的稳态寿命试验后,内部气氛各项指标均满足高可靠标准(结果见表5)。将图6、表5和图1、表1分别进行对比,说明上述工艺参数研究具有高可靠性。

Research on the HIC Cirucit Dies Eutectic Soldering Technicque

LI Bo, XIA Junsheng, LI Shousheng

(North General Electronic Corporration, Microelectronics Research Division, Bengbu 233042, China)

To meet thermal radiation and in-package atmospheric control requirement, the eutectic soldering technique has been mostly applied in HIC processing. Introduce the research work through grouping experiments, IPA inspection, X-ray inspection and other methods. Finally, conclude a key processing plan of eutectic soldering.

HIC, eutectic soldering, IPA inspection, X-ray inspection, processing plan

图6 芯片无助焊剂共晶空洞或孔洞情况

TN 452

A