数字短波阵列天线的时钟同步算法

段彦亮,李思敏,2,唐智灵,2

(1.桂林电子科技大学 信息与通信学院,广西 桂林 541004;2.桂林电子科技大学 认知无线电与信息处理教育部重点实验室,广西 桂林 541004)

数字短波阵列天线的时钟同步算法

段彦亮1,李思敏1,2,唐智灵1,2

(1.桂林电子科技大学 信息与通信学院,广西 桂林541004;2.桂林电子科技大学 认知无线电与信息处理教育部重点实验室,广西 桂林541004)

针对阵列天线端数字采样时钟的同步问题,提出一种高精度的时钟同步算法。在PTP同步协议的基础上,通过对时钟脉冲的上升沿和下降沿检测提高时间戳精度。基于FPGA设计了以双边沿检测算法为核心的时钟同步电路,并搭建仿真平台对算法进行验证。仿真结果表明,该算法能对短波阵列天线输出的阵列信号进行高精度的同步采样。

阵列天线;同步;波束形成;采样;数字电路

在短波通信中采用阵列天线能够提高接收信号的信噪比以及抑制干扰。若直接对阵列天线单元的信号进行采样再传输数字采样信号,能够避免模拟信号在馈线中传输所产生的衰减,从而进一步提高天线系统的性能。然而,短波阵列天线中阵元之间的距离较远,使得提供给各阵元的采样时钟之间存在相位误差,会影响后续的信号个数估计、波达角估计以及波束形成的运算。因此,需要一种能够对各个天线阵元信号的采样时钟进行误差估计以及校准的分布式采样时钟同步算法。现有的时钟同步算法中,针对不同精度的时钟同步需求,通信网的同步主要有IRIG-B、GPS、NTP和PTP等同步方式。

IRIG-B码是为了实现靶场间的信息交换而制定的一种时间标准码,其综合了脉冲对时和串口报文对时的优点[1]。IRIG-B码携带的信息经过译码后可获得即时的日、时、分、秒等时间信息。该编码已经具有国际通用性,可以达到微秒级别对时精度,但IRIG-B码的产生和接收相对比较复杂。GPS时钟同步技术利用GPS卫星与地面GPS接收设备进行数据通信,然后计算出GPS接收设备与对应卫星的距离、卫星信号发送至接收设备产生的时延参数等信息,通过这些参数信息修正GPS接收设备输出的秒脉冲频率和含有地理位置及时间信息的GPS报文[1]。虽然GPS的精度可以达到微秒级且技术成熟,但存在卫星天馈系统施工困难、成本高的问题[2]。NTP和PTP是基于数据链路层和网络层的时钟同步技术,主要应用于网络上的节点同步,二者的时钟同步原理基本相同,网络中的设备节点通过发送和接收带有时间戳的数据包使自身的时钟与标准时钟同步[3],主要区别在于时间标记生成与测量位置的不同:NTP标记时间与完成同步在应用层实现,精度仅为毫秒级别,而PTP是在物理层加盖时间标记,可达到优于微秒级的精度。

应用在数字短波阵列天线中的时钟同步算法需要同时具备高精度时钟同步、高速数据传输、高可靠性以及较高的集成度。为此,提出一种高精度的时钟同步算法,为数字短波阵列天线的阵列提供低相位误差的信号采样时钟。该算法在PTP时钟同步原理的基础上,通过双边沿测量法对时钟脉冲的上升沿和下降沿进行检测,以提高时间戳精度。

1 PTP时钟同步

PTP时钟同步技术被IEEE-1588标准采用,是一种高精度时钟同步技术。它将分布式系统内不同精度的时钟信号同步到统一的、具有高性能的主时钟,时钟精度可达亚微秒级别[4]。PTP多用于分布式网络结构系统,这些网络中不同节点设备间采用主从时钟同步结构,主时钟由网络中时钟质量较好或逻辑指定的节点提供。此外,PTP网络中的每个设备具有多个时钟同步端口,对于上层设备而言,其时钟端口为主端口,对于下层设备而言,其时钟端口为从端口。在系统的最高层存在一个根节点时钟,网络中所有节点的时钟同步于根节点时钟。

分布式系统的大规模应用对各控制节点间的时钟同步精度要求越来越高,同步精度的高低已成为时钟同步算法与实现最为关键的问题。与同为网络时钟同步协议的NTP协议相比,PTP协议在更接近网络物理链路的物理层进行时间戳的加盖与测量,从而避免了操作系统线程切换以及软件协议栈引入的不确定时延,显著提高了时钟同步精度。

PTP协议基于同步数据包传播和接收时的最精确的匹配时间,每个从时钟通过与主时钟交换同步报文而与主时钟达到同步[5]。在系统同步过程中,主时钟周期性发布PTP时钟同步协议及时间信息,当从时钟端口接收到主时钟端口发来的时间戳信息后,系统据此计算出主从线路时延及主从时间差,并利用该时间差调整本地时间,使从设备时间保持与主设备时间一致。

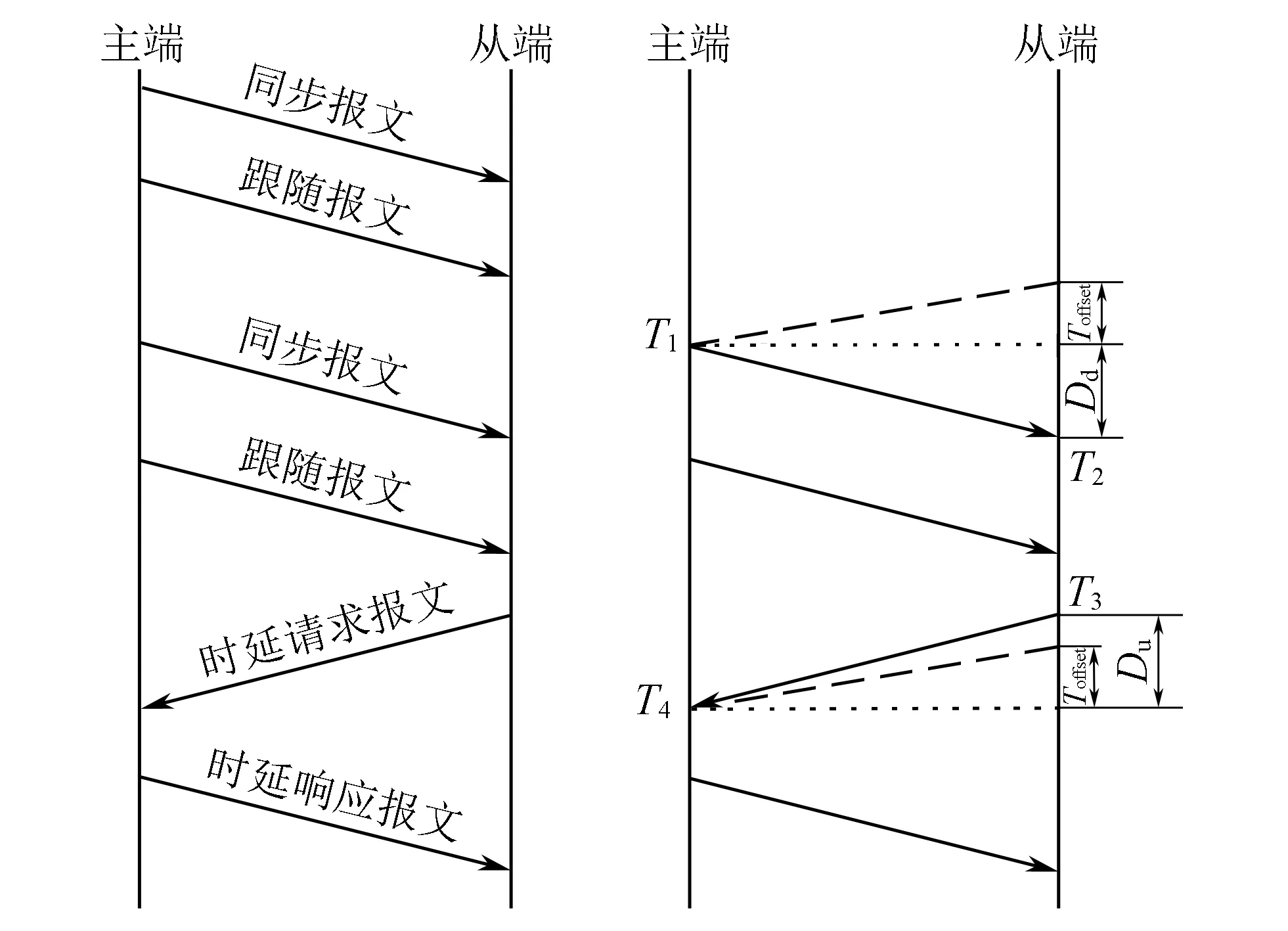

PTP协议用数据报文进行时间信息传输与交换,同步流程主要用同步报文(Sync)、跟随报文(Folow_Up)、时延请求报文(Delay_Req)和时延响应报文(Delay_Resq)[6]四种报文。PTP时钟同步的流程如图1所示。

图1 PTP时钟同步流程Fig.1 PTP clock synchronization

PTP时钟同步最简单的应用是点对点同步,报文通信过程为:

1)主时钟周期性地向从时钟发送同步报文,随后发送跟随报文,该报文包含同步报文的发出时间T1;

2)从时钟收到同步报文后计算其精确到达时间T2,并由收到的跟随报文得到同步报文的发出时间T1;

3)从时钟发送时延请求报文,并计算其发送时间T3;

4)主时钟收到时延请求报文后,计算其到达时间T4;

5)主时钟发送时延响应报文,将T4回发给从时钟。

如图1所示,由主端至从端时延为下行时延并记作Dd,由从端至主端时延为上行时延并记作Du,主端与从端时钟偏差为Toffset,则各时间量关系为:

(1)

(2)

设中间变量Tdelay为上下行链路平均时延,则有

(3)

由式(1)~(3)可得主端与从端时钟偏差:

(4)

假设上下行链路时延相等,

(5)

从时钟根据Toffset调整本地时钟,则

(6)

其中:Tcur为从时钟当前值,TS为调整后的本地时钟。经过以上过程完成一次时钟同步。

2 双边沿测量法

2.1双边沿检测法原理

由式(4)可知,同步过程中Toffset需要通过时间戳T1、T2、T3、T4计算得到,时间戳的误差会直接产生时钟偏差Toffset而影响时钟同步精度。设精确时间戳为TR,测量时间戳与精确时间戳偏差为δ,则

(7)

时钟偏移量误差为:

(8)

设δ在时钟周期内均匀分布,时间戳计数器时钟频率翻倍,则有

(9)

由式(9)可知,时钟偏移量误差会减半。因此PTP时间戳计数器计数周期越短,其时间戳精度越高,同步精度越高。但在实际硬件中,时钟频率越高对器件的要求也越高,因此用时钟的上升沿和下降沿对时间戳计数器操作,其功能等同于运用原时钟二倍频信号来驱动电路。这看似将时间戳计数器精度提高,但实际上,使用混合时钟沿将使静态时序分析复杂,使得时序时延折半,并导致电路工作频率降低[7]。

通过以上分析可知,为提高时间戳精度,分别用双时钟沿对协议报文收/发进行时间测量,相当于将时间戳计数器时钟频率翻倍,其工作时序如图2所示。

图2 双边沿时间戳检测时序Fig.2 Time sequence of dual-edge time stamp detection

时间戳计数器在主时钟驱动下输出上升沿计数值CNTR_R以及上升沿计数值相移180°的CNTR_F,检测器对协议报文收/发完成信号XEN分别在主时钟上升沿与下降沿边沿采样,由获得的边沿检测信号驱动D触发器分别对CNTR_R和CNTR_F采样并比较,由比较器比较2个输入值,若相等,则将CNTR_R加0.5后作为时间戳输出,否则将CNTR_R直接输出。

2.2双边沿检测法的功能实现结构

图3为双边沿时间戳检测,使用时序电路设计,让EOF(End-Of-Frame)信号分别通过工作于2个反相时钟域的下降沿检测电路,产生触发器D1与触发器D2的门阀信号,最终输出处理后的时间戳。

图3 双边沿时间戳检测Fig.3 Dual-edge time stamp detection

双边沿检测模块可采用2路双D触发器串联下降沿检测电路(路径a与路径b),分别工作于时钟上升沿、下降沿。对于每个到达的EOF信号脉冲,边沿检测电路产生2个相位相差半个时钟周期的脉冲信号,分别驱动后级触发器D1、D2的使能端,并在下一个周期对上升沿计数器和下降沿计数器的值进行采样,将所得到的采样数值送入比较器,则比较器所得到的时间戳更接近EOF信号实际到达的时间点。

3 基于双边沿检测的PTP同步网络的FPGA实现

图4为基于FPGA的PTP时钟同步方案,用于实现高精度PTP时钟同步与基于光纤链路的高速数据传输。每个模块的主要功能如下:

1)Aurora模块。调用Xilinx公司的Aurora的IP核,例化高速串行收发器,完成比特流的透明传输,速率达1.25 Gbit/s。

2)PTP报文打包模块。负责PTP协议同步报文的封装。

3)PTP报文解析模块。负责解析发送端的PTP同步报文,并根据接收到的不同PTP报文置位对应的标志位。在同步主端,当同步报文发送成功时,置位m_sy_done标志位;当跟随报文发送成功时,置位m_fu_done标志位;当时延请求报文接收成功时,置位m_dp_done标志位。在同步从端,当时延请求报文发送成功时,置位s_dq_done标志位。

4)双边沿检测器和计数器模块。采用双边沿检测法,告知状态机PTP同步报文收/发时间戳T1、T2、T3、T4。

5)PTP报文解包模块。负责解析接收端的PTP同步报文,并根据接收到的不同PTP报文,置位对应的标志位。在同步主端,当时延请求报文接收成功时,置位m_dq_done标志位。在同步从端,当同步报文接收成功时,置位s_sy_done标志位;当跟随报文接收成功时,置位s_fu_done标志位;当时延应答报文接收成功时,置位s_dp_done标志位。

6)数据发送/接收缓冲模块。用于缓冲除PTP报文外的数据帧。

7)复用器模块。将数据发送缓冲模块和PTP报文打包模块复用接入Aurora模块。

8)状态机模块。完成PTP协议的通信流程,并协调PTP同步报文与普通数据的传输。

图4 PTP时钟同步方案Fig.4 PTP clock synchronization scheme

整个硬件系统在状态机的协调下进行工作,其在主端的状态流程如图5所示。

1)当主端的状态机收到上层PTP同步报文发送请求时,各模块的标志位清零,选通复用器的PTP报文打包模块,状态机由M_idle状态转换为M_sync状态。

2)进入M_sync状态后,使能内部计数器K,并判断标志位m_sy_done是否为1及当前计数器K所用时间是否小于2 s,若均为真,则进入M_followUp状态,并立即读取当前计数器模块的时间戳,记录为T1,同时停止计数器K,清除标志位m_sy_done及内部计数器K,否则同步报文发送失败,返回到M_idle状态。

3)进入M_followUp状态后,将时间戳T1送入PTP报文打包模块进行PTP协议报文封装,直到标志位m_fu_done为1,进入M_dlyReq状态,同时将复用器切换为数据发送缓冲端,并清除标志位m_fu_done。

4)进入M_dlyReq状态后,使能内部计数器K,并判断标志位m_dq_done是否为1及计数器K所用时间是否小于2 s,若均为真,则进入M_dlyResp状态,并立即读取计数器模块当前的时间戳,记录为T4,同时停止计数器K,清零标志位m_dq_done及计数器K,否则返回到M_idle状态。

5)进入M_dlyResp状态后,选通复用器的PTP报文打包模块,将时间戳T4送入PTP报文打包模块进行PTP报文封装,直到标志位m_dq_done为1,返回到M_idle状态,同时将标志位m_ptp_done置1,完成一次PTP同步。

图5 主端状态流程Fig.5 Flow chart of master end state

相应地,从端的状态流程如图6所示。

1)状态机上电后一直处于S_idle状态,直到标志位s_sy_done为1,跳转至S_sync状态。

2)进入S_sync状态后,立即读取计数器模块的当前时间戳,记录为T2,跳转至S_followUp状态。

3)进入S_followUp状态后,使能内部计数器H,并判断标志位s_fu_done是否为1及计数器H所用时间是否小于2 s,若均为真,则进入S_dlyReq状态,并提取从PTP报文解包模块解析出来的时间戳信息,记录为T3,同时停止计数器H,标志位s_fu_done及计数器H清零,否则返回到S_idle状态,同步失败。

4)进入S_dlyReq状态后,选通复用器的PTP报文打包模块,并发送Delay_Req报文,直到标志位s_dq_done为1时,立即读取计数器模块当前的时间戳,记录为T3,同时跳转至S_dlyResp状态,标志位s_dq_done清零,并将复用器切换为PTP报文打包模块。

5)进入S_dlyResp状态后,使能内部计数器H,并判断标志位s_dp_done是否为1及计算器H所用时间是否小于2 s,若均为真,则立即读取计数器模块当前的时间戳,记录为T4,同时停止计数器H,清零标志位s_dp_done及计数器H,并跳转到S_offset状态,将标志位s_ptp_done置1,完成一次PTP时钟同步。否则,返回到S_idle状态,同步失败。

6)进入S_offset状态后,根据T1、T2、T3、T4计算Toffset,以调整当前计数器的值,最后跳转至S_idle状态,并将标志位s_offset_done置1,完成时钟同步。

图6 从端状态流程Fig.6 Flow chart of slave end state

4 时钟同步误差分析与仿真

在通信网络中影响时钟同步精度的因素主要有时钟源频率偏差、时间戳的产生与测量误差、通信路径及通信介质偏差、同步协议报文在设备内拥塞导致的误差[8]。

时钟源频率偏差受时钟芯片的制造工艺以及外界环境影响,可采用更高精度的时钟源来降低次偏差;通信路径及通信介质偏差主要是由于通信链路的不对称性所造成的;时间戳的产生与测量误差、同步协议报文在设备内拥塞导致的误差是在处理同步报文的过程中引入的误差[7]。因此,提高时钟同步精度应着重于减小时间戳和同步协议报文在设备内拥塞所导致的误差。

基于图4的PTP时钟同步设计方案,采用双边沿检测法来提高时间戳精度。该方案采用全硬件实现,使得同步协议报文不会出现拥塞,进而降低了时钟同步误差。根据PTP时钟同步协议原理编写Matlab仿真程序,仿真结果如图7所示。一般PTP实现方式的同步误差平均值为171.630主时钟周期,明显高于基于双边沿的PTP实现方式的64.240主时钟周期。

图7 PTP同步误差Fig.7 PTP synchronization error

5 结束语

通过分析PTP时钟同步协议在同步过程中引入的误差因素,提出一种PTP协议的硬件设计方案,采用双边沿检测的时间戳增强测量法,在同步过程中提高了时间戳的精度,降低了时间戳的测量误差;采用专用硬件收/发同步报文,消除了报文生成/解析引入的误差。仿真结果表明,该方案相较于传统的软件实现方案,时钟同步误差控制在较低的水平。

[1]朱建华.分布式数据采集系统的设计与实现[D].合肥:安徽大学,2014:9-10.

[2]楚鹰军.高精度时间同步设备在移动通信网络上的应用[J].现代传输,2012(4):58-62.

[3]李红亮.基于PTP协议的高精度网络时间同步系统的设计与实现[D].天津:天津大学,2012:10-11.

[4]阮大同.PTP技术及其应用分析[J].中国新通信,2013(19):67.

[5]邱芬,陈孝良,马龙华,等.PTP精密时钟同步原理分析[J].微计算机应用,2009(10):18-22.

[6]李晓珍.基于IEEE 1588的网络时间同步系统研究[D].西安:中国科学院研究生院(国家授时中心),2011:15-16.

[7]云创工作室.Verilog HDL程序设计与实践[M].北京:人民邮电出版社,2009:248-250.

[8]王薇.一种自动对称补偿的网络IP时钟误差消除算法[J].软件,2014(10):67-71.

编辑:张所滨

A clock synchronization algorithm for digital HF antenna array

DUAN Yanliang1, LI Simin1,2, TANG Zhiling1,2

(1.School of Information and Communication Engineering, Guilin University of Electronic Technology, Guilin 541004, China;2.Key Laboratory of Cognitive Radio and Information Processing, Guilin University of Electronic Technology, Guilin 541004, China)

Aiming at the sampling clock synchronization in HF antenna array, a high-precision clock synchronization algorithm is proposed. Based on the analysis of PTP, the accuracy of the time stamp is improved by detecting the rising and falling edges of the clock pulse. Then a clock synchronization circuit is designed based on FPGA, and a simulation platform is built for verification. The simulation results show that the algorithm leads to high-precision synchronous sampling for HF antenna array.

antenna array; synchronization; beamforming; sampling; digital circuit

2016-03-07

国家自然科学基金(61461013)

李思敏(1963-),男,江苏苏州人,教授,博士,研究方向为电磁场与电磁波、认知无线电。E-mail:siminl@guet.edu.cn

TN911.72

A

1673-808X(2016)04-0259-06

引文格式:段彦亮,李思敏,唐智灵.数字短波阵列天线的时钟同步算法[J].桂林电子科技大学学报,2016,36(4):259-264.