一种基于PCI总线的数字图形发生器设计

芦 俊,张国良,曹 菁,陈 仑

一种基于PCI总线的数字图形发生器设计

芦俊1,张国良2,曹菁1,陈仑1

(1.江苏信息职业技术学院,江苏无锡 214000;2.扬州捷科科技有限公司,江苏 扬州 225000)

数字功能卡(PE)是集成电路测试设备的核心部件,也是SOC测试系统的必需部件,它可以完成数字IC的逻辑功能测试。成功开发好PE板是研发数字集成电路测试系统的必经过程,也是开发SOC集成电路测试系统的必经过程。介绍了一种基于PCI总线的数字图形发生器的设计方法。建立基于PCI总线、以DDR3作为存储器、以FPGA作为专用定制逻辑处理器这一架构的数字图形发生器电路系统模型,以产生任意测试矢量图形,满足高中低端数字类芯片的测试需求。重点介绍了采录模块发送模块、缓存模块、逻辑控制模块、PCI接口模块的设计方法。

PCI总线;数字图形发生器;DDR3;FPGA

1 引言

随着数字集成电路的应用日趋广泛和国家对半导体行业发展的支持,国内CMOS数字集成电路设计能力得到了长足的发展。但是目前国内IC生产线中的中、高档测试系统仍以国外进口为主,基本上没有国产中、高档的半导体测试设备或测试生产线。

本文介绍的数字图形发生器的设计方法拟采用高性能FPGA和DDR3作为图形发生器的核心器件,该设计预计能大幅度提升最高测试频率,从而解决国内数字测试系统多用单片机或者FPGA/ARM软核实现逻辑处理模块导致核心处理器速度相对较慢、极大影响测试板最高工作频率的问题。

2 测试系统工作原理介绍

不管数字集成电路功能有多复杂,工作在多高的电压,都可以将其看作一个二值逻辑器件。因此现在的大多数测试方法,不管是故障定位还是功能测试,都需要测试向量的输入,而数字集成电路测试系统实际上就是一个用于向量产生和比较的硬件平台[1~2]。

所谓测试向量,就是一串连续的“0”和“1”组成的数字序列。在测试数字IC之前,通过对测试要求和芯片功能的分配,利用向量编程器先写好测试所需的向量,定义好向量的时序要求,并将其下载到测试系统的存储器中,然后启动测试系统的控制模块。控制模块按照事先写好的测试程序语句,以一定顺序将测试向量从存储器中读出并送到向量调制模块。向量调制模块对向量序列进行波形调制电压调制,最后送出与待测IC(DUT)工作电压匹配的波形序列。同时测试系统还监测DUT的输出滤形,通过向量调制模块将其转换成与测试系统工作电平匹配的数字信号,测试系统将回送数字信号与预先设定的向量进行比较,并将比较结果送给控制模块进行处理。测试系统原理如图1所示[3]。

图1 测试系统原理框图

3 数字图形发生器的设计方法

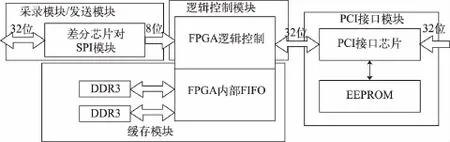

本文所介绍的数字图形发生器的硬件开发是基于PCI总线的板卡实现的,主要由采录模块/发送模块、缓存、PCI接口和逻辑控制4部分组成。其中,PCI接口和逻辑控制是设计的难点和重点[4~5]。

图2 系统硬件框图

4部分模块的基本组成为:

·采录模块/发送模块:包括SPI模块、差分芯片对。

·缓存模块:包括DDR3和FPGA内部FIFO资源。

·逻辑控制模块:包括FPGA和外围电路。

·PCI接口模块:包括PCI接口芯片和配置芯片EEPROM。

3.1采录模块/发送模块

该数字图形发生器硬件板卡的基本工作流程为:采录模块/发送模块把信号采录到板卡,或者把板卡上的信号发送出去,在这个过程中,通过差分芯片对,接收或发送信号后遵循SPI接口模式,即数据位宽为1位,而且长度有8个。在采录模块的硬件电路中,将8个1位数字信号在FPGA内部集中后转换为8位的数据,达到4个这样的数据后再转换为32位的数据,然后经过FPGA内部生成的异步FIFO,并在FPGA的控制下以32位的数据宽度送入DDR3中缓存起来。

DDR3起缓存作用,在DDR3中存满一定数据后,在FPGA的控制下,这些缓存数据以32位的数据宽度通过PCI桥接芯片,以DMA方式传输到计算机内存,并生成数据文件,留给后续信号处理用。同时,FPGA向DDR3下个定值地址写入下一数据。在发送模块的时候情况正好相反。

在采录模块和发送模块的时候都遵循SPI的发送方式,在采录模块的时候采用的是主SPI模式,在发送模块的时候采用的是从SPI模式。

SPI接口在CPU和外围低速器件之间进行同步串行数据传输,在主器件的移位脉冲下,数据按位传输,高位在前,低位在后,为全双工通信,数据传输速度总体来说比I2C总线要快。

在系统设计中,对外部信号传输采用差分芯片对。使用差分芯片对的优点有差分方式传输距离远及抗干扰能力强等。

3.2缓存模块

该数字图形发生器的缓存模块主要由DDR3和FPGA内部的FIFO资源构成,起到数据缓存的作用,数据采录具有数据吞吐率高的特点,因此采用DDR3和FPGA内部的FIFO资源来满足大容量的数据存储需求。

3.3逻辑控制模块设计

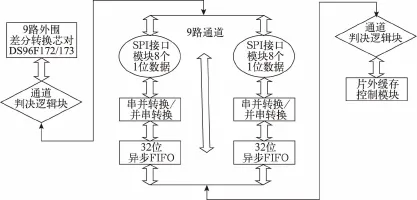

该数字图形发生器逻辑模块包含了控制传输模块/采录模块的逻辑部分、控制缓存的逻辑部分和控制PCI接口的逻辑部分,它们之间的关系是通过FPGA内部异步FIFO来连接的,如图3所示。

图3 FPGA逻辑控制模块结构图

在FPGA逻辑控制模块中,采用异步FIFO解决各个控制模块之间因为时钟频率不一致而产生的数据不同步,这样有助于数据的稳定传输以及数据的缓存。

数字图形发生器板卡的传输模块和采录模块的主要功能相同,都是采用SPI接口进行数据传输,只不过这里要考虑是主SPI还是从SPI。表1是它们的对应关系。

表1 采录模块/传输模块和主/从SPI对应关系表

在传输模块和采录模块中,除了含有SPI接口外,还有判断哪条通道有效的判决模块,具体的流程框图如图4所示。

图4 流程框图

图4中,由于有9个通道,而片外缓存只有一条数据线,这样就需要判断是哪个通道在起作用,然后才能把相对应通道的数据放到相对应地址处。在这个过程中,各个通道的数据在没有选通的时候是保持不变的,保证了数据的稳定和完整性。

在系统中使用轮循方式进行,9个通道中各个通道的选通不会是同时的,也不会出现任意两个通道同时选通的情况,为防止万一系统出现尖峰脉冲而造成数据紊乱的情况,在设计的时候加入了异常处理模块。

在SPI接口模块设计的过程中,定义传输的方式为对一个8 bit的数据采用先传输低位、然后再传输高位数据的做法。

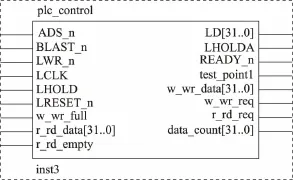

3.4PCI接口模块

该数字图形发生器的接口模块选用PCI接口芯片,并设计PCI接口芯片Local端的传输逻辑。图5给出了PCI接口芯片PCI9054模块图。

图5 PCI接口芯片PCI9054模块图

在PCI接口芯片中写入参数的过程如下:PCI接口在PCI接口芯片的Local端信号(ADS#等)控制下,将数字信号写入异步FIFO中,缓存模块根据FIFO的空满状态以及FIFO的数据位数决定读取数据的控制信号。

PCI接口芯片读取采录数据的过程如下:当一定时间内采录模块数据装到DDR3并且达到传输地址以后,置LINT中断信号有效并且传给主机,主机发出读PCI接口芯片的命令。PCI接口接收到LWR_n低有效,开始读数据,当数据读完以后,主机产生USERo信号,FPGA逻辑置LINT无效。

PCI接口芯片的Target传输和DMA传输在时序上都是一样的,分为读、写逻辑。具体细分又分为:单周期读、突发周期读、单周期写、突发周期写。拟以同步状态机设计其时序,如图6所示。

系统上电或复位后进入空闲状态,当ADS#信号有效以后,进入读/写状态,LW/R#为0表示读操作,LW/R#为1为写操作。进入读/写状态后,判断BLAST#是否有效,有效进入单周期状态,无效进入突发周期状态。在数据传输有效时,需要置READY#为0。

4 结论

数字图形发生器是集成电路ATE测试系统中的关键部件,本文主要介绍了一种基于PCI总线的数字图形发生器的设计方法,该方法采用高性能的FPGA和DDR3作为图形发生器的核心器件,能产生任意测试矢量图形,并大幅度提升系统的最高测试频率。

[1]布什内尔(美).超大规模集成电路测试:数字、存储器和混合信号系统[M].北京:电子工业出版社,2005.

[2]靳鸿.测试系统设计原理及应用[M].北京:电子工业出版社,2013.

[3]楼冬明,陈波.数字集成电路测试系统的研制[J].电子技术应用,2001(4).

[4]郭军.测试系统技术 [M].西安:西安电子科技大学出版社,2006.

[5]王良军.基于FPGA的数字信号发生器[D].成都:电子科技大学,2008.

A Design Method of PCI-bus-based Digital Pattern Generator

LU Jun1,ZHANG Guoliang2,CAO Jing1,CHEN Lun1

(1.Jiangsu Vocational College of Information Technology,Wuxi 214000,China;2.Yangzhou JK Technology co.,Ltd,Yangzhou 225000,China)

Pin Electronics(PE),one of the core components of digital IC and SOC test systems,is usually used in testing logic functions of digital ICs.An excellent PE card is pivotal in developing digital IC and SOC test systems.The paper introduces a design method of digital pattern generator based on PCI bus.The digital pattern generator model generates diversified test patterns to meets the test demands of high-,medium-and low-end digital ICs with DDR3 as memory and FPGA as customized logic processor.In the paper,the design method of collect and record module/sending module,cache module,logic control module and PCI interface moduleare highlighted.

PCI bus;digital pattern generator;DDR3;FPGA

TN402

A

1681-1070(2016)09-0024-04

芦俊(1974—),男,湖北荆门人,研究生,高级工程师,主要研究方向为机电一体化、检测与自动化装备。

2016-5-14