一种适用于FPGA系统中的变速箱电路设计

罗 旸,何光旭,雷淑岚

(中国电子科技集团公司第58研究所,江苏无锡214072)

一种适用于FPGA系统中的变速箱电路设计

罗旸,何光旭,雷淑岚

(中国电子科技集团公司第58研究所,江苏无锡214072)

设计了一种新型变速箱电路,变速箱两边采用同一时钟,不需要额外的时钟输入,使用计数器来控制位宽转变的整个过程,并产生标志位来控制变速箱数据的输入和输出。在不改变数据传输波特率的情况下,解决在传输过程中数据的重复或丢失问题,实现两边不同数据位宽的正确转换。电路适用于在FPGA系统中,模块之间或者各IP之间的数据位宽不匹配的情况下调整模块之间的数据位宽,从而实现各内部模块之间的数据位宽匹配。仿真结果表明,以66位数据转64位数据为例,在不影响有效数据传输速率的情况下,可以在32个时钟周期内完成数据的无损转换。

变速箱;标志位控制;高速串行通信;Serdes;FPGA系统

1 引言

随着FPGA芯片的不断升级换代,FPGA系统电路的规模越来越大,在系统电路中集成了各种模块和IP,比如高速端口收发器,FPGA接口的数据宽度大多为2n字节,一般为16位或者32位。

图1为在FPGA中实现10 GBase-R协议规定的64 B/66 B编码[1~2],经过扰码器后的66位信息分为两部分,一部分是64位有效数据负载信息,还有一部分是2位的同步信息,FPGA接口数据线宽度为32位,其中64位的数据有效负载信息通过FPGA接口的32位数据信号发送,2位同步信息通过2位的控制信号线发送,在发送到Serdes模块之前,要把数据负载信息和同步信息整合,再进行位宽由多到少的转换,因为在10 GBase-R的物理层收发器设计过程中,Serdes的并行端数据输入的位宽数一般不会是66位,且一般都不超过20位,如8位、10位、16位等[3],同样数据从Serdes模块发送到FPGA时,也需要进行数据位宽由少到多的转变[4]。变速箱电路就是实现任意数据位宽之间的转换,来保证FPGA系统内各模块之间的无缝连接与正常的数据传输功能。

图1 FPGA实现10 Gbps以太网收发器结构

如果直接根据变速箱两侧的数据输出和输入的数据率相等的原理,利用两个频率的时钟对数据位宽直接进行转换,而不对两侧时钟或者数据进行任何的控制或者处理,则会出现下面两种情况:

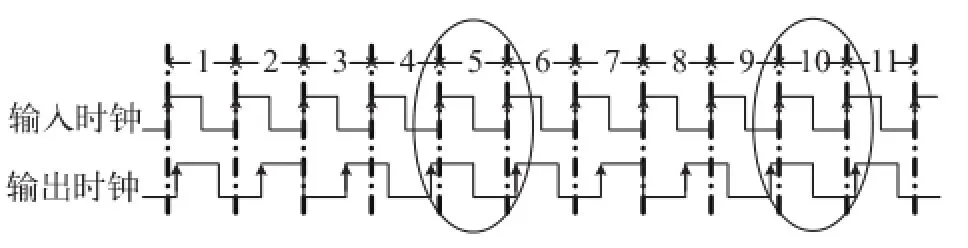

当变速箱数据输出的时钟频率大于变速箱数据输入的时钟频率,即输出数据所用的时钟周期小于输入数据的宽度时,在数据位宽转换过程中,在某个时钟周期下,输出数据的时钟会将当前周期下的数据采样2次,如图2中的第3和第8时钟周期,从而造成输出数据的重复[5~6]。

图2 同一数据采样2次

当变速箱数据输出的时钟频率小于变速箱数据输入的时钟频率,即输出数据所用的时钟周期大于输入数据的宽度时,在数据位宽转换过程中,在某个时钟周期下,如图3中的第5和第10个时钟周期,输出数据的时钟会漏采当前周期下的数据,从而影响数据传输的正确性。

图3 数据漏采

针对上述问题,可以通过产生不均等时钟的办法来解决:使用电路中固定时钟源产生两个基础时钟,再通过这两个基础时钟组合成变速箱的输入时钟和输出时钟,其中组合后的时钟周期是不均等的,但是其平均周期值是定值,确保变速箱两边的传输比特率相等。但是这种办法会需要额外的输入时钟,增加整个系统电路设计的额外开销。在FPGA系统中,由于FPGA用户可以自己来设计控制逻辑,本文提出一种新的应用于FPGA系统的方法,利用计数器控制位宽转换的过程,并产生标志位控制变速箱数据的输入和输出,可以很好地解决上述问题。在数据位宽由多向少转变的过程中,通过在某个时钟周期暂停给变速箱输入数据,但不停止变速箱的数据输出;在数据位宽由少向多转变的过程中,通过在某个时钟周期暂停给变速箱输出数据,但不停止变速箱的数据输入。

2 标志位控制输出变速箱的设计思路

在FPGA系统中,变速箱电路主要实现不同数据位宽之间的转换,变速箱两端的数据位宽和时钟频率在某一实际电路中是确定值。在本设计中,使用计数器电路来控制数据位宽转换的整个过程,并产生标志位来控制变速箱数据的输入输出,在不改变数据传输波特率的情况下,实现对数据位宽的无损增加,从而达到系统内部各模块间的位宽匹配。

为方便阐述,定义变速箱输入端时钟周期为T,输入端位宽为m,输出端时钟周期与输入时钟相同,输出端位宽为n,在实际电路中,输入时钟和输出时钟都是由系统中的固定时钟源产生,时钟源的频率是固定的,变速箱两端的位宽m、n的值根据具体电路的值确定。一般分为m<n和m>n两种情况。

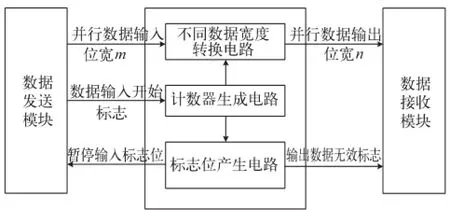

图4 变速箱结构

如图4所示,当变速箱并行数据输入位宽m小于输出位宽n时,在数据位宽转换的过程中,如果待转换的数据位宽积累到大于n,就进行数据位宽的转换,在当前时钟周期输出n位宽的数据,否则标志位产生模块产生输出数据无效标志位,数据接收模块通过此标志位确定当前数据无效,等待输入的并行数据积累到大于n位时再进行数据的转换。

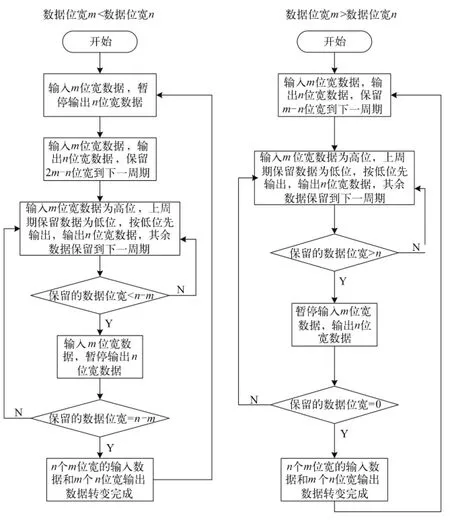

当变速箱并行数据输入位宽m大于输出位宽n时,在数据位宽转换的过程中,如果在当前时钟周期,转换后的数据位宽积累到大于n,就停止进行m位并行数据的输入,但是在下一个时钟周期继续输出n位宽的数据,并且标志位产生模块产生输入数据无效标志位,位宽转换电路会通过此标志位确定当前输入数据无效,不将此输入数据进行数据位宽的转换。具体的转换流程如图5所示。

图5 变速箱位宽转变流程图

3 标志位控制变速箱的实现

接下来具体说明变速箱的实现过程,在FPGA系统中,数据总线的位宽为32位,以10 GBASE-R物理层为例,Serdes的位宽要求为 16 bit,PCS采用64B/66B的编解码方式,在与Serdes模块进行数据传输过程中,需要通过变速箱模块实现66 bit到32 bit或者32 bit到66 bit两种位宽的转换。

输入数据的位宽m为66(32+32+2)bit,输出数据的位宽n为64(32+32)bit。

如图6所示,位宽转换前,66位宽的数据由两个32位数据信息和2位的同步信息组成,转换后64位宽的数据由两个32位数据组成。计数器控制着每完成一次数据位宽转换后累积下来的信息位宽,当计数器计数到31时,当前累积的数据位宽为30位,加上第32个时钟周期输入的32位宽的数据信息和2位宽的同步信息,此时正好有64位宽的信息;如果下一个时钟周期32位宽的数据信息继续输入的话,就会造成这32位宽数据信息的丢失;所以在计数器为31时,信息正常输入,在当前时钟周期,正常输出32位宽的信息,并产生低有效的输入控制信号;在计数器值为32时,在此时钟周期暂停输入标志位有效,暂停数据的输入,正常输出32位宽的信息数据。

图6 66位宽转换为64位宽

同理,当64位宽转换为66位宽时,当累计的信息位宽和新输入的数据位宽总和小于66时,此时输出无效标志位有效,暂停新的信息输出,等到下一个时钟周期再正常输入和输出信息。

4 变速箱的仿真与性能分析

使用verilog HDL语言对上述变速箱的功能进行描述,搭建验证平台,并使用VCS软件进行仿真,仿真示意图如图7所示。

图7 验证平台示意图

仿真结构图如图7所示,pattern_gen模块产生66 bit的数据,gearbox_1和gearbox_2是例化本变速箱模块,其中变速箱gearbox_1模块的输入数据位宽为32 bit,同步信息位宽为2 bit,输出数据位宽为32 bit;变速箱gearbox_2模块的输入数据位宽为32 bit,输出数据位宽为66 bit,同步信息位宽为2 bit。在pattern_chk模块中把pattern_gen模块产生的66 bit数据延时几个时钟周期后和该数据经过变速箱位宽转变后的66 bit数据相比较。仿真波形见图8。

如图8所示,仿真分为两部分:数据宽度66 bit到64 bit的转换和64 bit到66 bit的转换。

clk是固定的时钟源,其周期8 ns,在每一个clk时钟周期下,传输32 bit的数据。在gearbox_1中,66 bit的信息由 32 bit的 gbx_data_in和 2 bit的gbx_header_in组成,64 bit的输出信息由32 bit信号线gbx_out输出,gearbox_1中输出的32 bit信息作为gearbox_2中的输入,在gearbox_2中经过位宽转换后由gbx_data_out和gbx_header_out输出。

图8 仿真波形图

在gearbox_1中,可以看到计数器的值为31时,暂停输入标志位txgearboxready有效,在计数器的值为32时,暂停输入,此时的输入保持为上一时钟周期的值32’h79f和2’b00,在gearbox_2中,当输出无效标志位rx_data_valid有效时,暂停gbx_data_out的输出,保持为上一时钟周期的值32’h79f,由于输出的2 bit的gbx_header_out只是在高的32位输出时有效,通过rx_header_valid标志位来控制。

把gearbox_1的66 bit输入数据延时7个clk时钟周期后和gearbox_2的66 bit输出数据一一比较,在result中equal_32b信号为高电平,表明这两个数据完全相同,说明变速箱在66 bit位宽转变为64 bit位宽、再由64 bit位宽转变为66 bit位宽的过程中正确,没有丢失或重复采样。

5 结论

在变速箱电路中,通过标志位控制变速箱两边的信息输入和输出,可以保持变速箱两边的数据波特率不变,并且保证在传输过程中没有数据的丢失或重复采样,可以用于高速的FPGA系统中。

[1]Zhou Qinglun,Li Chunyan,Wang Yong.Hardware Implementationof64B/66BEncoder/Decoderfor10-Gigabit Ethernet[EB/OL].

[2]IEEE Std 802.3ae-2002[S/OL].New Jersey:IEEE,2002[2002-8-30].http://standards.ieee.org.

[3]H-R Lee,M-S Hwang,B-J Lee,Y-D Kim,D Oh,J Kim,S-H Lee,D-K Jeong,and W Kim.A fully integrated 0.13μm CMOS 10Gb Ethernet transceiver with XAUI interface[J].IEEE ISSCC Dig.Tech.Papers,2004,2:170-171.

[4]Virtex-II Pro Platform FPGA User Guide[EB/OL].San Jose:Xilinx,2005[2005-3-23].http://www.xilinx.com.

[5]黄安君,罗旸,雷淑岚.适用于10 Gbps以太网物理层收发器的变速箱电路设计 [J].电子与封装,2015,15(1):31-35.

[6]Yongsam Moon,Member,Sang-Hyun Lee,and Daeyun Shim.ADivide-by-16.5Circuitfor10GbEthernet Transceiver in 0.13 μm CMOS[C].IEEE.1175-1179.

Design of Gearbox Circuits for FPGA System

LUO Yang,HE Guangxu,LEI Shulan

(China Electronics Technology Group Corporation No.58 Research Institute,Wuxi 214072,China)

In the paper,a new design of gearbox that adapts the same clock at the both sides instead of involving an extra clock input is presented.It controls the whole process of bit width conversion by counters and produces flag bit to determine the input and output of the gearbox data.The design solves the problem of data repetition and loss during the transmission under fixed baud rate and consequently realizes the perfect conversion between the different bit-wide data.Under the situations when the data bit width are different among modules or IPs,the design is effective in adjusting and matching the data bit widths among modules. The simulation results show that the gearbox completes the data conversion from 66 bits to 64 bits within 32 clock cycles without loss of data rate.

gearbox;flag bit control;high-speed serial communication;Serdes;FPGA

TN402

A

1681-1070(2016)10-0019-04

2016-3-30

罗旸(1982—),男,福建长汀人,毕业于电子科技大学自动化专业,现在中国电子科技集团公司第58研究所从事科研项目技术与管理工作。