一种双采样1.2 V 7位125 MS/s流水线ADC的设计

王晓飞,郝 跃

(西安电子科技大学宽带隙半导体国家重点学科实验室,陕西西安 710071)

一种双采样1.2 V 7位125 MS/s流水线ADC的设计

王晓飞,郝 跃

(西安电子科技大学宽带隙半导体国家重点学科实验室,陕西西安 710071)

为了满足片上系统对模数转换器的低功耗和高性能的要求,设计并实现了一种1.2 V 7位125 MS/s双采样流水线模数转换器.该模数转换器采用了一种新的运算放大器共享技术以及相应的时序关系,从而消除了采样时序失配问题,并减小了整个模数转换器的功耗和面积.该模数转换器采用0.13μm CMOS工艺实现,测试结果表明,该模数转换器的最大信噪失真比为43.38 dB,有效位数为6.8位.在电源电压为1.2 V、采样速率为125 MS/s时,该模数转换器的功耗仅为10.8 m W.

双采样;运放共享;时间交织;流水线型模数转换器

流水线模数转换器(Analog to Digital Converter,ADC)是一种高速、高精度的奈奎斯特采样率模数转换器,它可以在高速、高精度和功耗三者之间很好地进行性能折中[1].因此,流水线模数转换器在多种技术领域得到广泛应用,例如,移动系统、光电耦合器件(Charge-Coupled Device,CCD)成像、超声波医疗成像、数字接收机、基站、数字电视、蜂窝基站以及以太网等[2-5].在上述应用中,一项关键技术是将低功耗、高信噪失真比的模数转换器与数字信号处理器集成在一个芯片中.典型的流水线模数转换器结构在实现高速、高精度时功耗较大,而时间交织型流水线模数转换器不仅具有高速和高精度的优点,同时还具有较高的功耗效率,可很好地满足上述系统应用[3,6].

典型结构的双采样时间交织模数转换器性能受到诸多非理想因素的影响,例如失调、增益失配、采样时间失配以及共享运算放大器造成的记忆效应等[7-8].为了消除这些非理想因素的影响,文献[9]将一个时间交织采样保持电路应用在每个通道中,从而将时序失配最小化,但是模数转换器的线性性能受到采样保持电路的限制.文献[10]在时间交织采样保持电路中采用一种特别的时钟方案来减小时序失配,但与信号相关的电荷注入会降低模数转换器的线性度,而且该方法采用的双采样技术会引起记忆效应,从而降低模数转换器的性能.笔者提出一种新的余量增益数模转换器(Multiplying Digital-to-Analog Converter,MDAC)运放共享技术,并设计实现了一种双采样7位125 MS/s的流水线模数转换器.

1 系统结构

系统设计要求为:125 MHz带宽,7位精度低压(1.2 V),双采样时间交织流水线模数转换器.

在本设计中,7位125 Mbit/s双采样流水线模数转换器是通过两个通道时间交织实现的,每个通道的采样速率为62.5 MS/s.为了避免不同通道之间的采样时序及物理失配,这两个通道共用一个采样保持电路.从文献[11]中可知,对于8位流水线模数转换器而言,若要求功耗最低,则每级MDAC精度安排为2.5-2.5-2.5-2.0,即3级2.5位的MDAC和1级2.0位的Flash模数转换器;若要求精度最优,则每级MDAC精度安排为1.5-1.5-1.5-1.5-1.5-1.5-2.0,即6级1.5位MDAC和1级2.0位Flash模数转换器.在本设计中,通过采用运放共享技术,已大幅降低了电路的面积和功耗(电路面积为0.3 mm2,电路整体功耗仅10.8 m W).在缓解了功耗和面积压力的情况下,选择后一种分段(每级1.5位结构)以满足其精度要求.因此,在本设计中每个通道是由5级1.5位的MDAC电路和1级2.0位Flash模数转换器组成的,具体电路结构如图1所示.

图1 双采样流水线模数转换器结构图

2 电路分析与设计

2.1采样保持电路

为了配合时钟交织结构的实现,采样保持电路采用电容翻转结构.电容翻转结构的优点是仅由一个采样电容实现,无电容之间失配问题且电路结构简单.为了分析方便,以单端电路为例,具体的双采样采样保持电路结构如图2(a)所示,但在实际电路中电路结构均为全差分结构.

笔者提出的双采样采保电路有两对采样电容Csa、Csb,分别为A、B两个通道所用.这两对采样电容共用一个全差分运算放大器来实现双采样保持功能,这样就能有效地避免失调和增益失配等非理想因素的影响,从而提高了整个模数转换器的线性度.两个通道的采样时钟采用两相非交叠时钟,分别为Φ1和Φ2.这两个采样时钟频率为62.5 MHz,整个模数转换器的采样频率为125 MHz.为了减小开关电荷共享,采用了底板采样技术,因此,每路通道的采样时钟需要一个辅助时钟,即时钟Φ1d和Φ2d,其中Φ1、Φ2为如图2(b)所示的早关断时钟.两个通道根据时钟Φ1和Φ2交替工作,当一个通道处于采样状态时,另一个通道处于保持状态.为了减小导通电阻的影响,在采样通路中采用了自举开关.采用自举开关也有助于减小与信号相关的电荷注入问题[12],从而提高了采样电路的线性度.

图2 采样保持电路结构和工作时序图

2.2MDAC电路

MDAC模块是流水线模数转换器中的关键模块,它的作用是在一定时间内完成量化、数模转换以及得到残余量.传统的双采样MDAC电路采用两个独立的子模数转换器,这种结构存在两个缺陷:一是这两个子模数转换器存在物理的失配,从而使整个模数转换器的动态特性降低;二是两个子模数转换器会使整个模数转换器的功耗和面积增加.

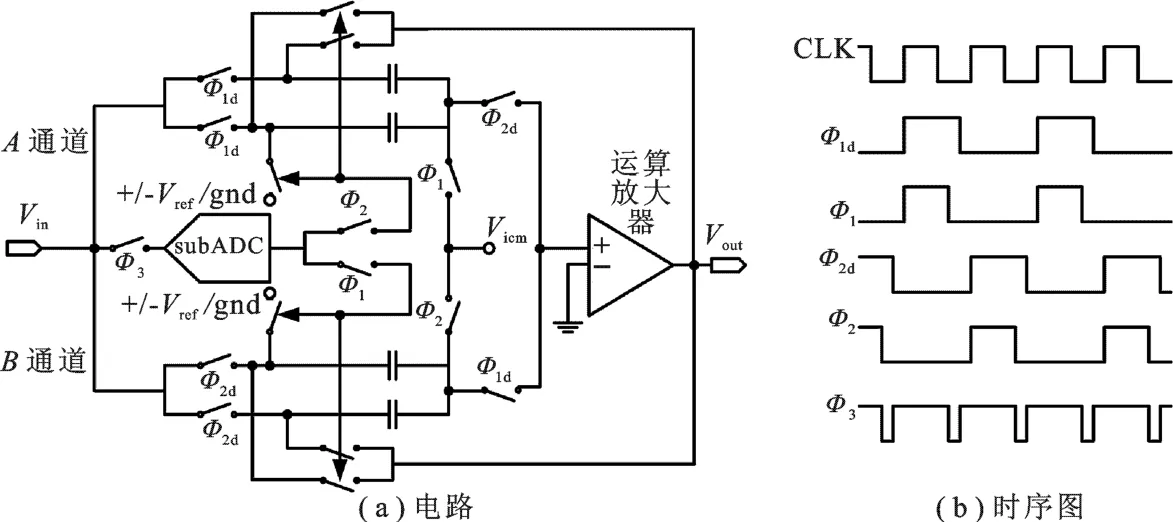

笔者提出的双采样MDAC结构是由两个通道共用一个1.5位/级子模数转换器和一个运算放大器,从而有效地克服了传统双采样结构的缺点.具体电路结构如图3(a)所示.

图3 双采样MDAC模块电路和时序图

该双采样MDAC电路在正常工作时需要3相时钟,分别为Φ1(Φ1d)、Φ2(Φ2d)和Φ3,其时序关系如图3 (b)所示.其中,时钟Φ1d、Φ2d为两相不交叠时钟.当Φ1d为高时,控制A通道采样电容的下极板对输入电压进行采样,同时控制运算放大器的同相输入端接B通道采样电容的上极板,使本级流水线输出B通道前次采样转换的量化余差;当Φ2d为高时,原理类似.Φ3作为子模数转换器的采样时钟,当Φ3为高电平时,进行上述的A、B通道交替采样及余差输出,实现了运放共享,节省了电路面积和功耗;在Φ3为低电平时,对采样电容的下极板及运算放大器的输出进行复位操作,泄放了上次采样转换的残留电荷,消除了传统运放共享引入的记忆效应.

此外,Φ1、Φ2分别为Φ1d、Φ2d的早关断时钟.先关断时钟Φ1(Φ2)使采样电容的上极板先断开,使电容器的一端处于“悬空”状态;然后再由正常时钟Φ1d(Φ2d)断开采样电容的下极板,由于此时无电荷充放通路,采样电容上的总电荷将保持为常数,避免了Φ1d(Φ2d)开关过程中开关管沟道电荷注入对输出电压的影响,从而降低了转换误差.

其时钟产生电路如图4所示,输入时钟信号CLK的频率为125 MHz.

2.3运算放大器

采样保持电路和MDAC电路中所采用的运算放大器如图5所示.为了满足直流增益和单位增益带宽要求,运算放大器采用两级结构.运算放大器的第1级采用折叠式共源共栅结构以提高运算放大器的增益和输入信号范围,第2级采用共源结构.由于该运算放大器为两级结构,且主极点在第1级输出,所以在设计时需考虑频率补偿.为了保证环路稳定性的同时不减少运算放大器的带宽,该运算放大器采用共源共栅补偿结构,即将米勒电容跨接在输出端与共栅管M4的源极之间,流过补偿电容的电流经过M4的源极和漏极反馈到差分放大器的输出端,M4的漏源电阻起到了传统米勒补偿中调零电阻的作用.该运算放大器的频率仿真结果如图5(b)所示.

图4 时钟产生电路

图5 运算放大器的电路图及仿真结果

3 实现及仿真结果

笔者提出的7位125 MS/s流水线模数转换器采用0.13μm互补金属氧化物半导体(Complementary Metal-Oxide-Semiconductor transistor,CMOS)工艺实现,版图设计及芯片照片如图6所示,模数转换器面积为320μm×940μm.该双采样模数转换器的性能仿真采用Cadence公司的Spectre工具.芯片测试得到的微分非线性(Differential Non Linearity,DNL)误差曲线和积分非线性(Integral Non Linearity,INL)误差曲线分别如图7所示,所有非线性误差均小于±0.5最低有效位(Least Significant Bit,LSB).在进行瞬态测试时,模数转换器的输入端加满幅度的差分正弦信号进行量化转换,然后将模数转换器的数字输出结果进行快速傅里叶变换分析,得到的频谱图如图8所示.

输入信号频率为3.025 MHz,采样频率为125 MHz的频谱分析结果如图8(a)所示;输入信号频率为33.875 MHz,采样频率为125 MHz的频谱分析结果如图8(b)所示.根据测试结果,该双采样流水线模数转换器的信噪失真比为43.38 dB,无杂散动态范围大于53 dB,有效位数为6.8位.在1.2 V电源电压下,整个模数转换器的功耗为10.8 m W.表1对笔者设计的和其他参考文献中设计的模数转换器进行了比较.由表1可以看出,在相同或相近工艺条件下,笔者设计的双采样流水线模数转换器具有明显的功耗优势,在125 MHz采样频率下仅为10.8 m W,其能耗效率品质因素(Figure Of Merit,FOM)[3]也优于其他文献,仅为0.75.

图6 双采样模数转换器版图及芯片照片

图7 微分非线性误差及积分非线性误差的测试结果

图8 输出信号快速傅里叶变换频谱分析图

表1 模数转换器性能对比

4 总 结

笔者设计了一种7位125 MS/s双采样流水线模数转换器结构,并在0.13μm CMOS工艺上实现.该模数转换器采用了一种新的子模数转换器和运算放大器共享技术以及相应的时序关系,从而有效地减小了传统双采样结构的物理失配,并减小了整个模数转换器的功耗和面积.根据仿真结果,该双采样流水线模数转换器的信噪失真比大于42 dB,无杂散动态范围大于53 dB,有效位数达6.8 bit.在1.2 V电源电压、125 MHz采样频率下的功耗仅为10.8 m W.该双采样流水线模数转换器在面积和功耗方面具有较大的优势,可广泛应用于有线、无线收发器的接收端以及SoC系统中.

[1]SUMANEN L,WALTARI M,HALONEN K A I,et al.A 10bit 200MS/s CMOS Parallel Pipeline A/D Converter[J]. IEEE Journal of Solid-State Circuits,2001,36(7):1048-1055.

[2]XUE F F,WEI X M,HU Y C,et al.Design of a 10bit 50 MSPS Pipeline ADC for CMOS Image Sensor[C]//2014 IEEE 9th Conference on Industrial Electronics and Applications.Piscataway:IEEE,2014:891-895.

[3]KIM H J,AN T J,MYUNG S M.Time-interleaved and Circuit-shared Dual-channel 10 200 MS/s 0.18μm CMOS Analog to Digital Converter[J].IEEE Transations on Very Large Scale Integration Systems,2013,21(12):2206-2213.

[4]曹超,马瑞,朱樟明,等.高精度SAR ADC非理想因素分析及校准方法[J].西安电子科技大学学报,2015,42(6): 71-77. CAO Chao,MA Rui,ZHU Zhangming,et al.Analysis on Non-ideal Factors and Digital Calibration for High-resolution SAR ADCs[J].Journal of Xidian University,2015,42(6):71-77.

[5]杨银堂,袁俊,张钊锋.256 MHz采样71 dB动态范围连续时间Σ-ΔADC设计[J].西安电子科技大学学报,2015,42 (1):10-15. YANG Yintang,YUAN Jun,ZHANG Zhaofeng.Continuous TimeΣ-ΔADC Design with 256 MHz Sampling and 71 dB DR[J].Journal of Xidian University,2015,42(1):10-15.

[6]MAXIM A,POORFARD P,CHENNAM M.A 0.13μm CMOS DBS Demodulator Front-end Using a 250 MS/s 8 bit Time Interleaved Pipeline ADC and a Sampled Loop Filter PLL[C]//IEEE Radio and Wireless Symposium.Orlando: IEEE,2008:53-56.

[7]VERMA A,RAZAVI B,FATTARUSO J,et al.A 10 bit 500 MS/s 55 m W CMOS ADC[J].IEEE Journal of Solid-State Circuits,2009,44(11):3039-3050.

[8]MIKI T,MORIE T,OZEKI T,et al.An 11 bit 300 MS/s 0.24 pJ/conversion-step Double-sampling Pipelined ADC with On-chipfull Digital Calibration for All Nonidealities Including Memory Effects[C]//IEEE Symposium on VLSI Circuits. Piscataway:IEEE,2011:122-123.

[9]LOUWSMA S M,TUIJL A J M,VERTREGT M,et al.A 1.35 GS/s,10 b,175 m W Time-interleaved AD Converter in 0.13μm CMOS[J].IEEE Journal of Solid-State Circuits,2008,43(4):778-785.

[10]GUPTA S K,INERFIELD M A,WANG J.A 1 GS/s 11 bit ADC with 55 dB SNDR,250 m W Power Realized by a High Bandwidth Scalable Time Interleaved Architecture[J].IEEE Journal of Solid-State Circuits,2006,41(12):2550-2657. [11]HATI M K,BHATTACHARYYA T K.An 8-b 250-M Samples/s Power Optimized Pipelined A/D Converter in 0.18-μm CMOS[C]//2015 International Conference on VLSI Systems,Architecture,Technology and Applications. Piscataway:IEEE,2015:1-6.

[12]景鑫,庄奕琪,汤华莲,等.一种新型双通道MOS开关栅压自举电路[J].西安电子科技大学学报,2014,41(3): 138-144. JING Xin,ZHUANG Yiqi,TANG Hualian,et al.Novel Dual-channel MOS Bootstrapped Switch Circuit[J].Journal of Xidian University,2014,41(3):138-144.

(编辑:郭 华)

Design of double sample 1.2 V 7 bit 125 MS/s pipelined ADC

WANG Xiaofei,H AO Yue

(State Key Lab.of Wide Bandgap Semiconductor Technology Disciplines, Xidian Univ.,Xi’an 710071,China)

A 7 bit 125 MS/s double sample pipelined ADC which can achieve a low power and a high performance for the SoC system is presented.The presented ADC with op-amp sharing between two channels and a new timing scheme can not only eliminate sampling timing skew,but also has a low power and a small area.Test results show that the ADC designed in a 0.13μm CMOS process achieves a maximum SNDR of 43.38 dB,and that ENOBis 6.8 bits.The ADC consumes 10.8 mW at 125 MS/s under a 1.2 V supply voltage.

double sample;op-amp sharing;time-interleaved;pipelined analog to digital converter

TN4

A

1001-2400(2016)04-0023-06

10.3969/j.issn.1001-2400.2016.04.005

2015-06-02 网络出版时间:2015-10-21

国家自然科学基金资助项目(61204085,61334002)

王晓飞(1979-),男,西安电子科技大学博士研究生,E-mail:xjtuwxf@126.com.

网络出版地址:http://www.cnki.net/kcms/detail/61.1076.TN.20151021.1046.010.html