模块化多电平变流器控制系统设计

李硕,张卓阳,杨立滨,凌志斌

(1.上海交通大学电气工程系 上海 200240;2.国网青海省电力公司电力科学研究院,青海 西宁 810000)

模块化多电平变流器控制系统设计

李硕1,张卓阳1,杨立滨2,凌志斌1

(1.上海交通大学电气工程系 上海 200240;2.国网青海省电力公司电力科学研究院,青海 西宁 810000)

分析了模块化多电平变流器控制系统的特点及其要求,并设计了满足实时性和一致性要求的控制系统。控制系统采取两级架构,主控制器采取DSP+FPGA构架,子模块控制器采取FPGA控制,两者之间采用高速工业光纤进行控制指令和数据的传输。设计实现了载波移相调制功能,并对控制系统的实时性与一致性进行分析和实验验证。

模块化多电平换流器;控制系统;实时性

当前,无功发生器(SVG)、高压变频器和高压链式储能系统采用的级联H桥结构,以及在柔性高压直流输电应用的MMC-HVDC结构,均属于模块化多电平变流器。其共性的一点在于不同模块之间电位不同,不同子模块控制系统之间以及主控制器与子模块控制器之间电气上相互隔离,隔离电压达到10~35 kV。模块化多电平换流器的正常工作需要主控制器与子模块控制器的协调配合,控制器发送的控制指令能否始终及时被子控制器接受并产生所需的严格的控制、驱动和反馈时序决定着整个系统能否可靠运行。为此,必须保证主控制器与子模块控制器通信的实时性,以及各个子模块通信的一致性,即上位机从发送控制指令到每个子模块接收并产生驱动信号的延迟时间尽可能短且接近一致。

当前,模块化多电平控制系统构架有两级和三级两大类。两级控制系统架构由主控制器和从控制器两级组成,主控制器负责系统采样、控制运算以及PWM调制和生成,从控制器主要负责子模块开关信号的输出。三级控制系统架构相对于两级控制系统架构增加了中间层——辅助控制器,每个辅助控制器控制一相或1个桥臂上的若干个子模块控制器[1]。

1 模块化多电平变流器控制系统特点

模块化多电平变流器的主电路拓扑结构决定了其控制系统具有如下特点:1)控制系统为分布式主从结构,主从之间和从从之间在电气上均相互隔离;2)对上层控制器运算处理,对于模块数量较多的情况采用两级控制架构,对于模块数量众多的情况采用三级控制架构,以此分担控制处理任务;3)子模块控制器功能和结构相同,可相互替换;4)控制系统的时序控制能力要求高,需要采用高精度高频的数字电路来实现;5)控制系统具有软件和硬件的扩展能力[2]。

2 控制系统设计

2.1 控制系统架构

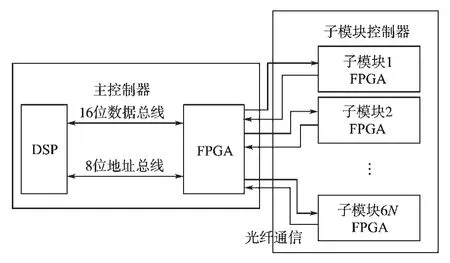

本文设计的模块化多电平变流器模块数量在100左右,因此采用了两级控制系统架构,其结构和主控制器与子模块控制器功能分工如图1所示。

图1 MMC系统控制框架Fig.1 Controller architecture of MMC system

主控制器采用DSP+FPGA的硬件构架,除利用DSP的高速数据处理能力实现变流器功能控制算法,DSP还实现对电网电压、桥臂电流的采样,对采样得到的电压模拟量,转换成16位的调制信息。FPGA则发挥其高速时序处理能力和资源丰富的优势,将来自DSP的调制数据量作为载波移相参考值,通过载波移相得到各个子模块开关控制信号,然后将控制信号编码通过光纤通信发送给下位机各个子模块。DSP和FPGA之间采用双口RAM进行数据的交互。

子模块控制器采用FPGA为核心辅以相关硬件电路组成。每一个子模块由1个控制器控制,实现对上位机控制信息的接收;子模块上、下2个开关管的驱动信号及其死区的生成、过流保护;子模块电池电压信息及子模块故障信息(过流故障、通讯故障)的实时监测和信息上传[3]。

图2以1个子模块为例,显示了各个控制器之间信息交互的方式与具体内容,主控制器DSP与FPGA之间通过FPGA内部的双口RAM进行并行通信,主控制器FPGA与子模块FPGA之间采用光纤以串行通信的方式进行信息交互。

图2 控制器间的信息交互Fig.2 Data exchange between controllers

2.2 载波移相设计

主控制器产生并发送给各个子模块控制器的PWM控制信号采用载波移相调制技术实现。以每相4个子模块级联的拓扑结构为例进行分析,主控制器FPGA产生4个幅值和频率完全相同的三角波作为载波且任意2个相邻载波的相移为90°。

实际设计中,为保证响应速度和时序的精度,计数器的频率设计为130 MHz,计数位数设计为16位,如此可保证控制时序的分辨率达到7.7 ns。主控制器FPGA定义4个计数器,相邻2个计数器延时四分之一载波周期,每个计数器从零逐一加到计数峰值然后再逐一减到零。三角波作为载波的频率为1 kHz,主控制器DSP以6 kHz的频率更新调制信息,将16位的调制信息发送给主控制器FPGA,作为FPGA内载波移相的比较值。通过载波与调制波的比较,即计数器值与调制数据值比较,产生控制子模块的PWM。

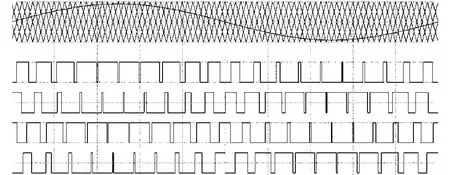

图3 载波移相原理图Fig.3 Diagram of carrier phase-shifting

图3所示为三角载波与调制波比较得到的PWM信号波形图。图3中从上到下依次为上桥臂子模块1,下桥臂子模块1,上桥臂子模块2,下桥臂子模块2的PWM波形,其中上桥臂和下桥臂中子模块的控制信号互补。

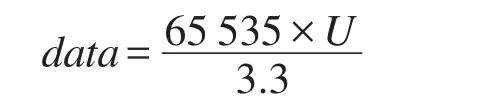

调制信息为16位的数据,设DSP采样得到的电压值为U(其中U经过抬升,范围0~3.2 V),则调制信息:

16位的调制信息为data取整并转换成16位2进制数。

2.3 控制器间的通讯设计

2.3.1 主控制器DSP与FPGA信息交互

主控制器DSP和FPGA作为核心部件,向子模块控制器发送控制信号,处理子模块控制器上传的子模块信息,协调控制模块化多电平变流器的正常运行。

主控制器FPGA与DSP的数据交互不多,但实时性要求高,因此通过FPGA内双口RAM实现。在FPGA内定义1块容量为256,字长为16的双口RAM。主控制器DSP与FPGA之间通过并行总线的形式通讯,地址总线宽度为8位,数据总线宽度为16位。如此满足数据交换速度、数据数量和数据精度3方面的要求。

根据RAM由DSP写入还是FPGA写入,双口RAM的存储地址分为两部分。

DSP向RAM写入的数据信息包括标志数据,控制数据以及调制信息。标志数据指示DSP是否已经向RAM写入新数据。控制数据,指示调制信息是否考虑电池电压均衡以及是否停机。

FPGA向RAM写入的数据信息包括标志数据、子模块状态信息(是否有通信故障或者过流故障)、子模块电池电压信息及总状态信息。

2.3.2 主控制器FPGA与子模块FPGA串行通信

主控制器FPGA内产生一系列固定相位差的三角载波,与从DSP读到的调制信息比较,产生控制每个子模块的PWM,向下位机发送控制信号,控制下位机上、下开关管的开闭。

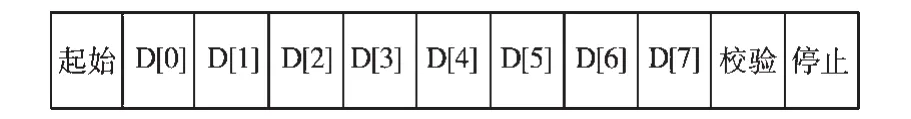

上位机主FPGA与下位机子模块FPGA的信息交互,采用自定义的串行通信协议,如图4所示。

图4 串行通信协议图Fig.4 Diagram of serial communication protocol

主FPGA与子模块FPGA通讯以11位/帧的格式进行传输,波特率为1 Mb/s,无论上位机向下位机发送信号还是下位机向上位机发送信息都是以相同的通讯格式,包括1个起始位、8个数据位、1个校验位和1个停止位。上位机主FPGA与子模块FPGA通讯的时钟周期为88 M,1位包含8个时钟周期,一帧有11位,传输1帧所需时间1 μs。

主控制器FPGA向子模块FPGA发送信息包括2个过程。首先主控制器FPGA与子模块FPGA建立同步。主控制器FPGA上电后,立即向子模块FPGA发送自定义的同步PWM,子模块FPGA上电后立即开始检测,如果接收到符合定义要求的PWM信号,子模块FPGA向主控制器FPGA返回1个同步确认信号,此时子模块FPGA同步完成,等待接收上位机发来的控制信号。当主控制器FPGA接收到子模块FPGA返回的同步信号时,主控制器与子模块控制器完成了启动同步过程。

同步完成后即可发送控制指令,数据位第1位,为闭锁信号位,当其为1时,上下开关管均关断;为0时,开关管处于控制状态。数据位第2位,为控制位,为1时,上管导通下管关闭;为0时,上管关闭下管导通。其余数据位为保留位。

若在系统正常工作过程中,主控制器或者子模块控制器在一定时间内没有收到来自对方的信号,则认为通讯中断(如光纤连接断开),此时主控制器与子模块控制器重新启动同步校验,回到初始检验同步的状态,即主控制器FPGA不断发送同步信号,子模块FPGA处于等待接收同步信号的状态,待通讯线路恢复正常后,子模块检测到主控制器发送的同步信号后向主控制器返回同步确认信号,双方均确认同步后,恢复正常数据发送状态。

子模块FPGA接收完来自主控制器的控制指令后,就产生1个发送使能信号,向主控制器发送当前子模块的状态信息及电池电压信息。发送的信息为连续的4帧11位数据,前2帧为子模块状态信息,包括是否通信故障及是否过流故障;后2帧为电池电压信息。

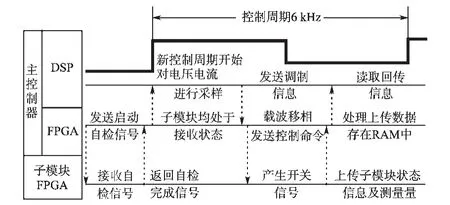

整个MMC系统控制器的控制时序,如图5所示,刚启动时,主控制器FPGA和各子模块FPGA存在一个“握手”的过程,等子模块都处于准备就绪的状态时,主控制器DSP开始采样,采样频率是6 kHz。DSP将16位的调制信息发送给主控制器FPGA,FPGA通过载波移相形成各个子模块的控制信号,发送给各个子模块,子模块FPGA对控制命令进行解码,生成开关管的控制信号。接收到主控制器信号的同时,各个子模块上传状态信息及测量量,保存到主控制器FPGA的RAM内,等待DSP读取相应地址的信息。

图5 MMC系统控制器的控制时序Fig.5 Control timing of MMC system controllers

在上述时序的情况下工作,保证通信的实时性非常重要,通信的实时性直接影响到控制的效果,同时还必须保证子模块通信的一致性,即在保证通信实时性的同时,各个子模块通信过程产生的延迟要大致相同。

2.4 控制系统的实时性保障和分析

为了保障控制系统的实时性与一致性,主控制器采用FPGA,实现6 N个子模块控制信号的产生与发送,FPGA使用硬件电路完成相应逻辑与时序的处理,具有硬实时的并行处理能力,硬实时保障了控制信号下发的实时性,并行处理能力保障了不同子模块控制信号的产生与发送具有一致性,保证有效的控制[4]。

主控制器FPGA与子模块FPGA通信采用自定义的串行通信协议,波特率为1 Mb/s,上位机与子模块通信在1 μs时间完成,同时主控制器编码以及子模块解码得到开关管控制信号需消耗5个左右系统时钟周期即50 ns左右。主PFGA与子模块FPGA间采用光纤进行通信,保障长距离通信的实时性,光纤接收器采用AVAGO公司的R-2624Z型号,发射器采用T-1624Z型号,查其数据手册,发射与接收各有30 ns的延时,即共有60 ns的延时。

从上位机主FPGA产生控制信号到下位机接收并产生相应的开关信号约有1.11 μs的延时,根据分析,延时主要来自串行通信1 μs,信息处理50 ns,光纤发射及接收延迟60 ns。1.11 μs的延时满足系统实时性的要求,不影响系统的控制。不同子模块与主FPGA通信的延迟,其中串行通信与信息处理的1.05 μs延迟理论上一致,光纤发射及接收的延迟在理论值60 ns附近波动,不会有较大的误差。不同子模块与主FPGA通信延迟均保证在1.11 μs左右,具有良好的一致性。

3 实验验证

3.1 实验平台

基于上述控制系统架构及控制器间通讯的设计,研制了模块化多电平换流器(MMC)样机。主控制器中的DSP采用TI公司的F28M35H52C1,FPGA采用Altera公司CycloneⅣ系列型号为EP4CE30F23C7的芯片,子模块控制器中的FPGA采用Actel公司的ProASIC3 A3P060芯片。主控制器与子模块控制器之间采用光纤进行通讯,光纤接收器采用AVAGO公司的R-2624Z型号,发射器采用T-1624Z型号。

3.2 实验结果及分析

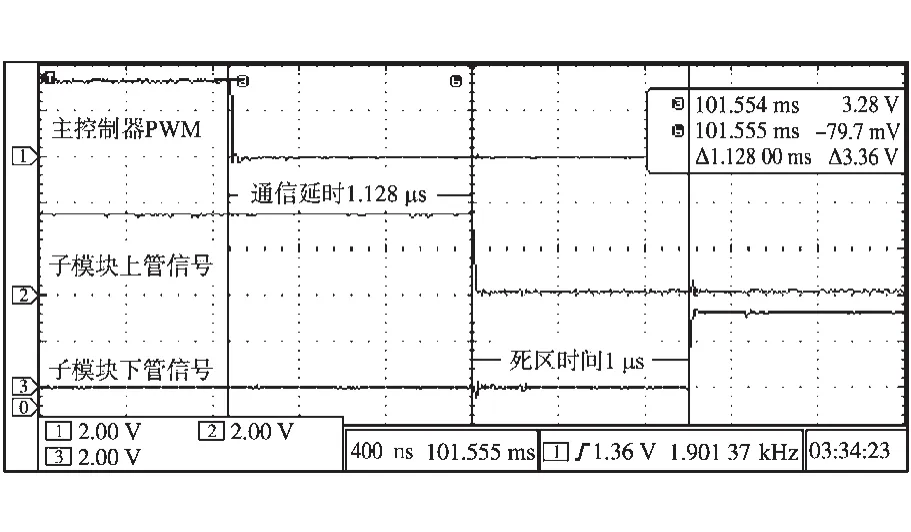

正常工作时,主控制器DSP采样处理后得到的16位调制信息,通过总线的形式发送给主控制器FPGA作为载波移相的比较值;主控制器FPGA通过载波移相得到多路PWM,每一路均通过光纤与子模块控制器进行通讯。每个子模块FPGA对接收的信息进行解码,产生2路死区为1μs的PWM开关信号,控制MOSFET的开合。

如图6所示,波形1为主控制器载波比较得到的PWM,波形2为子模块产生的上管控制信号,波形3为子模块产生的下管控制信号。比较图中波形1与波形2可知,子模块产生的PWM控制信号比主控制器载波比较得到的PWM延迟约1.128 μs;比较图中波形2和波形3可知,子模块产生的上、下管PWM开关信号,有1个约1 μs的死区。

图6 主控制器PWM及子模块上、下开关管信号波形Fig.6 PWM of host-controller and signal waveforms of upper and lower switches of sub-module

由上述实验结果知,从主控制器载波比较得到PWM控制信号到下位机处理接收数据产生相应PWM开关信号,大约有1.128 μs延时,与理论上得到的1.11 μs延时相近,在允许误差内,保证了实时性,不影响控制。同时,上、下2个开关管控制信号之间有1个1 μs的死区,和程序设定值一致,符合要求。

实验测试中选取载波信号为1 kHz,调制波信号为50 Hz,载波比为20。使用示波器观测载波移相得到PWM信号波形。图7所示为控制一相4个子模块的PWM波形,4个PWM波形通过载波移相得到,其中波形1、波形2分别为上桥臂2个子模块的控制信号,波形3、波形4为下桥臂2个子模块的控制信息,波形之间间隔一定的相位差,且上桥臂与下桥臂子模块的控制信号互补,符合设计要求。

图7 载波移相波形Fig.7 Waveforms of carrier phase-shifting

4 结论

模块化多电平变流器控制系统具有分布式、实效性、时序精确和高度电气隔离的特点。本文设计并实现了模块化多电平变流器控制系统,并通过样机对主控制器与子模块控制器通信的实时性和载波移相调制功能进行了验证。主控制器中FPGA的硬实时并行处理能力,高速光纤和自定义的高速通讯协议,从硬件和软件方面保障了通信的实时性。另外,在通讯过程中,还实现了开机自检,通讯异常解除后重连的功能,保证了通讯的准确性和抗干扰性,保证了系统的正常安全运行。

[1]王莹.基于光纤复用技术的模块化多电平变换器控制系统研究[D].杭州:浙江大学,2015.

[2]翟晓萌.MMC-HVDC物理模拟系统子模块控制器的研制[D].保定:华北电力大学,2014.

[3]罗程,赵成勇,张宝顺,等.基于MMC的柔性直流输电站级控制器的设计及其动模实验[J].现代电力,2015,32(2):64-69.

[4]郭敏.基于FPGA的MMC-HVDC系统物理控制器设计与RTDS仿真验证[D].保定:华北电力大学,2012.

修改稿日期:2016-04-19

Design of Modular Multilevel Converter Control System

LI Shuo1,ZHANG Zhuoyang1,YANG Libin2,LING Zhibin1

(1.Dept.of Electrical,Shanghai Jiaotong University,Shanghai 200240 China;2.Electric Power Research Institute of State Grid Qinghai Electric Power Corporation,Xining 810000,Qinghai,China)

Analyzed the characteristics of MMC(modular multilevel converter)control system and its requirements and designed a control system which met the requirements of real-time and consistency.Control system took two-stage structure of host-controller and sub-module controllers.Host-controller used DSP and FPGA architecture,sub-module controllers used FPGA,and between them high-speed industrial optical fibers were used to transmit control instruction and data.The design implemented the function of carrier phase-shifting,analyzed and verified the real-time and consistency of control system.

modular multilevel converter(MMC);control system;real-time

TM464

A

10.19457/j.1001-2095.20161111

青海省光伏发电并网技术重点实验室(2014-Z-Y34A)

李硕(1993-),硕士研究生,Email:shuiher@163.com

2015-09-23