基于PCIe总线的双路1394B接口模块设计与实现

范祥辉,闫海明,史 岩,吴 娇

(中航工业计算所,西安 710119)

基于PCIe总线的双路1394B接口模块设计与实现

范祥辉,闫海明,史 岩,吴 娇

(中航工业计算所,西安 710119)

为了满足航电系统中前端传感器捕获的图形图像数据实时传输的需求,设计并实现了基于PCIe总线的双路1394B接口模块;该模块通过PCIe接口与主机交互,采用S400β传输模式,软件设计符合标准OHCI规范,支持AS5643协议,异步流包数据收发采用链式队列管理,主机与1394B控制器之间通过DMA操作,实现大数据块的并行处理,两路1394B相互独立,显著提升数据传输性能;测试验证结果表明,该模块具备带宽高、可靠性高、CPU资源占用率低等特点,已在某项目获得成功应用,实现了图形图像数据的实时传输,满足系统设计要求,表现出了良好的稳定性和适应性,具有实践应用价值。

1394B总线;异步流消息;链式队列

0 引言

IEEE 1394是为了增强外部多媒体设备与电脑连接性能而设计的高速串行总线,传输速率可以达到400 Mbps,利用IEEE 1394技术可以轻易地把电脑和摄像机、高速硬盘、音响设备等多种多媒体设备连接。IEEE1394具有高带宽、低成本、拓扑灵活、支持热插拔等特点[1-2]。SAE对IEEE1394B-2002协议进行了扩展和约束,并制定了包括AS5643、AS5643/1、AS5657、AS5706、AS5654、AS5708等多个标准,规定了应用协议、测试规范、电缆特性等,用于指导1394B总线在航空领域的应用。军用航空领域1394B总线应用模式大致分为两类,第一类应用于数据传输要求高可靠、低延迟、确定性、完整性的环境,如美国JSF战机飞控系统用1394B作为各子系统互联的主总线,第二类应用于航电系统中,利用其高带宽和实时性高的特点,完成图形图像数据的实时传输。

本文设计了一种基于PCIe总线的双路1394B接口模块,该模块通过PCIe接口与主机交互,采用S400β传输模式,具备带宽高、成本低、可靠性高、CPU资源占用率低等特点,已在某型航电系统中得到应用,体现了良好的可靠性和适应性,实现了图形图像数据的实时传输。

1 硬件设计

为了满足项目需求,总线接口模块需要提供两路独立的1394B总线数据收发功能,且两路数据传输需要并行处理,因此,总线接口模块与主机之间采用PCIe接口进行信息交互,满足高速数据传输要求,其硬件架构如图1所示。PCIe转PCI桥实现主机PCIe接口与两路1394B总线控制器PCI接口的转换,单路1394B总线电路由数据链路层、物理层及变压器组成。消费领域内1394B信号最长传输距离为4.5 m,航空应用条件下通过变压器延长1394B信号传输距离,并保证数据传输的质量。

1.1 电源电路

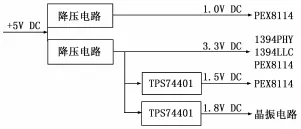

1394B接口模块由5V DC单电源供电,模块内部需要的电源有3.3 V、1.8 V、1.5 V、1.0 V。3.3 V和1.0 V电压微型降压式DC/DC电路实现,供电关系如图2所示。用于PCIe-to-PCI桥片供电的1.0 V和3.3 V电压有上电顺序要求,要求1.0 V先上电,通过降压电路RUN/SS管脚上RC电路中的电容来实现调节。

图11394 B接口模块硬件架构框图

图21394 B接口模块供电指示框图

1.2 时钟电路

1394B接口模块的PCIe接口需要100MHz差分时钟信号,该时钟是由主机提供,并通过XMC高速连接器输入给模块内部的PCIe-to-PCI桥片。PCIe-to-PCI桥片经过内部分频电路输出33 MHz PCI接口时钟,供给两路1394B链路层芯片的PCI接口作为PCI时钟源。

两路1394物理层PHY芯片分别需要一个外部的1.8 V的49.152 MHz晶振,来生成1394B基准时钟,该时钟驱动物理层芯片内部锁相环,以生成所需的基准时钟,用以控制输出编码信息的传输。本设计中需要实现S400β传输模式,物理层芯片的BMODE引脚配置为高电平,物理层芯片的PCLK引脚上生成98.304 MHz的时钟,并提供给链路层芯片,以实现两个器件之间的同步。为了保证时钟精度,设计中选用的49.152 MHz晶振的精度小于75ppm,布局时应尽量靠近物理层芯片,对于物理层芯片的PCLK引脚添加20~30欧姆的串联电阻来增加阻抗并减少信号的放射。

1.3 链路层电路

1394B链路层的功能为1394B同步和异步模式提供数据包接收、数据包传送、周期收发控制功能,实现了数据包接收确认、定址、数据校验以及数据分帧等[4]。链路层功能由硬件实现。对于异步传输事务,链路层提供了事务层和物理层之间的接口,还提供了基于与事务层相同的请求/响应模型的各种服务;对于等时传输事务,链路层提供等时软件驱动程序和物理层间的接口。

1394链路层芯片支持PCI、1394B及1394OHCI规范,它实现了1394B协议的链路层功能,支持S400β传输模式。本设计中,采用该芯片组成总线节点时,一端通过PCIe-to-PCI桥芯片实现主机PCIe接口到1394B链路层芯片PCI接口的协议转换,通过采用33 MHz/64bit的PCI接口,最大程度地满足主机接口的高速数据存取要求。另一端同1394节点的物理层芯片连接,将链路层信号转变为物理层与链路层的接口信号。1394B数据链路层与物理层之间的信号连接方式如图3所示。

图3 链路层-物理层接口信号示意图

1.4 物理层电路

1394B物理层电路为1394B总线收发提供数据编码、译码、总线仲裁、数据流控制、线缆电源管理等功能。1394B接口模块设计中,物理层芯片需保持与同系列其他物理层芯片的兼容性。设计中通过端口速度和模式配置端口S[5:0]将节点配置为S400β传输模式。该芯片的组成如图4所示,主要信号的连接关系如下:物理层晶振输入引脚连接1.8V供电的49.152 MHz晶振;将芯片的VREG_PD引脚设置为低电平,以使得物理层芯片外部只需要提供3.3 V单电源供电,芯片所需的1.8 V供电由芯片内部的电压变换电路生成,不需要外部提供;物理层和链路层接口信号与链路层芯片的相应管脚相连;在3个电缆端口信号和相应的偏置终端需要连接RC终端网络,以实现与线缆阻抗匹配,减小信号放射,终端网络的布局应该与TP引脚尽量接近;在1394B物理层端口和模块连接器之间选用PULSE生产的1394B专用有源变压器实现隔离耦合,以保证总线的信号品质,增强传输距离。

图4 物理层芯片组成框图

1.5 主机接口电路

主机通过XMC结构的高速连接器与1394B接口模块进行物理连接,通过PCIe总线接口实现对接口模块内部资源的访问。主机接口的设计主要是选用PCIe-to-PCI桥芯片实现主机PCIe接口到1394B链路层芯片PCI接口的协议转换。PCIe接口链路采用X1模式,PCIe-to-PCI桥芯片所需的100 MHz差分时钟是由主机提供并通过XMC高速连接器输入到模块内部。PCIe-to-PCI桥芯片的PCI信号端配置成33 MHz/64bit模式与1394链路层芯片的PCI接口连接,最大程度地满足主机接口的高速数据存取要求。设计中按照PCIe信号的电气信号设计要求,在靠近桥芯片PCIe的发送引脚上添加AC耦合电容,以消除链路两端两个设备之间的DC共模电压共享需求,使得每个设备可以使用自己的电源和地来运行,与链路另一端的设备无关。主机的复位信号PERST#通过XMC结构的高速连接器与桥芯片的PCIe端的复位管脚相连,两路1394B设备(包括物理层和链路层芯片)的复位信号都与桥芯片的PCI端的复位信号PCIRST#相连。当主机发出复位信号时,会触发桥芯片的PCI端的复位信号,从而实现两路1394B设备的复位。

2 软件设计

1394B接口模块驱动软件基于标准OHCI接口开发[5],驻留于主机,运行于Vxworks操作系统之上,为子系统主机提供两路1394B总线设备管理、通信管理和中断处理功能。驱动软件为应用层提供访问控制接口,协同硬件共同完成1394B总线的通信、管理等流程,为系统提供可靠、高速、实时的1394B异步流数据通信能力。

2.1 资源初始化

在使用1394B总线接口模块前,应对资源进行初始化,主要包括PCIe接口初始化,完成PCIe接口资源配置;工作模式初始化,用于设定节点的工作模式,接口可以工作在控制计算机(CC)和远程节点(RN)条件下;存储空间初始化,用于分配主机缓存空间,用于消息环形缓冲区资源分配。

2.2 数据收发接口

提供1394B设备数据的发送和接收功能,能够根据主机的实际情况,为用户提供方便、易用的数据传输接口,灵活有效的进行数据传输的控制和配置,满足系统在飞行、地面调试等多种的应用要求,主要包括以下子功能:1)异步流发送,发送数据应在尽量短的时间内上总线,降低发送延迟;2)异步流接收,接收数据应采用环形缓冲方式进行管理,避免发送时间抖动引起的消息丢失;3)DMA缓冲区管理,为了降低CPU资源占用率,减少数据发送时主机的干预时间,采用链式队列发送方式对缓冲区进行管理,实现1394B异步流包的自动发送。

2.3 中断处理接口

1394B通信软件提供应用中断例程处理功能,以提供应用处理部分中断事件的能力,包括:挂接中断处理回调函数及注销中断处理回调函数,对数据传输过程中产生的发送结束中断和总线复位中断信号进行处理。在中断处理函数中,首先对中断原因进行判断,包括消息结束中断、复位中断、异常中断等,需要对每一种中断情况均进行单独处理。在处理复位中断时,需要考虑复位风暴导致的主机死机问题。同时,由于复位函数的执行会打断CPU正常操作,为了尽可能少地干预CPU正常的处理流程,软件设计时,仅在中断服务程序中置位中断标志,进行必要的操作,让中断服务程序执行时间最短,另起任务进行中断事项的后续处理。

3 测试验证

搭建如图5所示的测试平台,对1394B总线接口模块两路独立的1394B总线功能、性能进行全面测试,主要包括1394B信号端口测试、物理层寄存器测试、链路层寄存器测试、通信测试、功耗测试、总线带宽测试及CPU负载率测试。

图5 测试平台示意图

为了更真实地模拟实际应用场景,主机将视频源按照1394B格式分包传输,每包有效载荷不大于2048Byte,并将DAP F3810监控设备及视频采集设备接入总线,测试结果见表1所示。测试结果表明,基于PCIe总线的双路1394B接口模块功能和性能均满足应用要求。

表1 测试结果统计表

4 结束语

基于PCIe总线设计的双路1394B接口模块支持S400β工作模式,具有带宽高、成本低、可靠性高、主机资源占用率低等特点,已成功应用于某型航电系统中,完成图形图像信息的实时传输,具有良好的实用价值。

[1]刘宝明,苏培培.基于CPCI总线的IEEE1394接口模块设计与应用[J].计算机测量与控制,2011,19(10):2504-2506.

[2]辛永利,田 泽.机载UMS系统二余度1394B总线网络设计[J].计算技术与发展,2015,3(26):197-201.

[3]1394b OHCI-Lynx Controller Data Manual[Z].2006,11.

[4]李世平等编,IEEE-1394(FireWire)系统原理与应用技术[M].西安:西安电子科技大学出版社,2004.

[5]1394Open Host Controller Interface Specification[Z].2000.6.

Design and Implementation of Dual Channel 1394B Interface Module Based on PCIe Bus

Fan Xianghui,Yan Haiming,Shi Yan,Wu Jiao

(AVIC Xi′an Aeronautics Computing Technique Research Institute,Xi′an 710119,China)

In order to meet the needs of the avionics system front-end graphical image sensor to capture real-time data transmission,designed and implemented Dual 1394B bus interface module based on PCIe.The module interacts with the host PCIe interface,using S400β transmission mode,the software design specification standard OHCI support AS5643 protocol to send and receive data using asynchronous stream packet queue management chain between the host controller and 1394B through the DMA operation,and big data parallel processing block,two 1394B independently,significantly improve data transfer performance.Verification test results show that the module has high bandwidth,high reliability,CPU resource consumption rate and other characteristics,have been successfully used in a project,to achieve real-time transmission of graphic image data to meet the design requirements of the system,showing good stability and adaptability,have practical value.

1394B bus;asynchronous stream message;linked queue

1671-4598(2016)08-0165-03

10.16526/j.cnki.11-4762/tp.2016.08.044

:TP334.4

:A

2016-01-28;

:2016-03-11。

航空科学基金项目(2014ZC31002)

范祥辉(1985-),男,安徽人,工学硕士,主要从事机载网络技术等方向的研究。