基于USB2.0和FPGA的高速数据采集系统的研究

黄洪+董小龙+沈明炎

(福建省计量科学研究院 福州 350001)

摘 要:本文提出的是一种基于USB2.0和FPGA的高速数据采集系统,将USB2.0技术和FPGA技术有机的结合在一起,将模拟数据进行数字转换,并实现高速的信号传输。本系统结构灵活,适用于实时信号处理,能够被广泛的应用在各个领域中。

关键词:USB2.0;FPGA;数据采集;固件

1、引言

随着信息技术的飞速发展,人们对于数据采集系统的速度和精度的要求也在不断地提高。USB接口作为一种新型的总线接口规范,被广泛的应有在数据采集系统当中[1]。本文充分利用了USB和FPGA的优点,设计了一种基于USB2.0和FPGA相结合的高速数据采集系统[2]。

2、高速采集系统的硬件设计

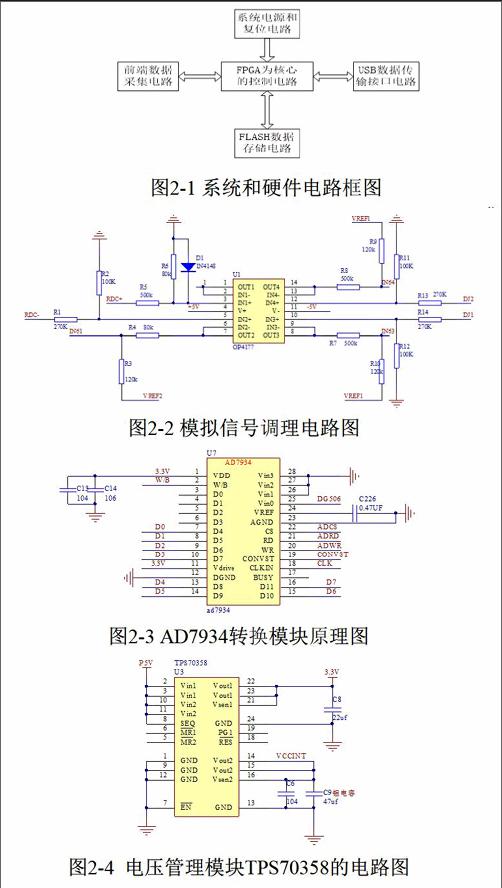

本系统是以FPGA作为核心控制器,通过ADC作为前端的模数转换采集电路,利用USB数据接口将数据传输到上位机上去[3]。FPGA控制的高速数据采集系统的形成还要包括系统电源模块、复位电路模块、FLASH数据存储模块等。系统的硬件电路框图如图2-1所示。

在信息数据采集的前端是需要对电路进行信号调理,使采集的输入信号满足系统采集输入范围,降低外界干扰信号[4]。AD7934模数转换器的电压输入范围在2.7V-5.25V,因此,需要在电路中加入基准电压VREF1。本系统采用的运算放大器OP4177,它具有极低失调电压和漂移、低输入偏置电流、低噪声及低功耗等特性,被广大电子工程师所喜爱。模拟信号调理电路如图2-2所示。

模数转换芯片AD7934具有低功耗、高吞吐率的特点,最高采样率为1.5MS每秒,内置一个精确的2.5 V片内基准电压源,可用作模数转换的基准电压源。同时,AD7934为12位数据输出端口,在本系统中采用了高8位,AD7934转换模块原理图如图2-3所示。

整个系统包含多个模块,整个电路提供的电压值为5V,但是FPGA在工作中,需要的电压值为3.3V,这就需要将5V的电压值进行转换。本系统采用的是TPS70358稳压器来进行实现,电压管理模块TPS70358的电路图如图2-4所示。其中,Vin是5V的电源输入端口,Vout是3.3V的电源输入端口,VCCINT则为1.8V的电压输出端口。

本系统采用的FPGA是Xilinx公司生產的,其工作需要与外部的FLASH来共同实现数据采集存储[5]。在数据存储电路中,采用的是K9K8G08U0M,它是一种NAND型的FLASH,存储容量是8448Mbits,包含数据寄存器和缓冲寄存器。

USB接口电路采用的核心控制芯片为CY7C68013,其传输方式有控制传输、中断传输、块传输和同步传输。CY7C68013具有三种可用的接口模式,分别是端口模式、可编程的GPIF模式和Slave FIFOs模式。为了方便FPGA控制,本系统采用的是Slave FIFO接口模式,采用异步读写的方式进行数据传输[6]。

3、高速采集系统的软件设计

基于FPGA控制的高速采集系统是根据逻辑时序来进行软件设计的。首先,要对各个参数变量进行初始化设置,检测是否与设备进行连接,读取端点数,确定数据传输端点;其次,启动AD转换,开始采样,判断数据是否读取成功;最后,保存数据,将数据利用USB接口上传到上位机中。高速采集系统的软件设计流程图如图3-1所示。

USB2.0工作的软件设计,要对其进行固件设置,将所有的寄存器都恢复到出厂状态,实现初始化。由于采用的是Slave FIFO模式进行数据的高速传输,端点FIFO在接收到FPGA控制器传输AD转换的数字信号后,等待PC读取,USB芯片只作为一个数据传输通道。USB的固件流程图如图3-2所示。

4、结论

本文提出了基于USB2.0和FPGA的高速数据采集系统,以FPGA作为核心控制器,通过ADC作为前端的模数转换采集电路,利用USB数据接口将数据传输到上位机上去。通过硬件电路和软件设计来进行实现,使信息数据能够高速的传输到上位机中。

参考文献

[1]冯新亚,蒋朝根.基于USB2.0+FPGA的高速数据采集系统的研究与设计[J]. 中国科技信息 ,2009,03:91-93.

[2]谢勇,姚远程,秦明伟. 基于USB2.0与LabVIEW的高速数据采集系统设计[J].电子设计工程,2012,20(19):5-9.

[3] 余志荣,杨莉. 基于NI-VISA与LabVIEW的USB接口应用设计[J]. 单片机与嵌入式系统应用2007,1: 66-69.

[4] 曹辉,刘波姜,秀杰. 基于USB与FPGA的多路总线通信接口的设计与实现[J]. 导弹与航天运载技术2009,302(4):18-22.

[5] 封治华,杜改丽. 基于FPGA的高速USB2.0数据采集系统主控电路设计[J].电子设计工程,2013,21(20):56-58.

[6] 关守平,尤富强,董国伟. 基于FPGA的高速数据采集系统设计[J].控制工程,2013,20(5):970-975.