开源片上系统Freedom E310调试方法研究

雷思磊,薛正

(酒泉卫星发射中心,酒泉 735000)

开源片上系统Freedom E310调试方法研究

雷思磊,薛正

(酒泉卫星发射中心,酒泉 735000)

Freedom E310是第一款基于RISC-V指令集架构的开源商业片上系统,可以依据具体应用场景对其进行深度定制,在对Freedom E310及其Debug单元简单介绍的基础上,设计通过OpenOCD、J-Link建立Freedom E310调试环境,并进行了实际测试。

RISC-V;Freedom E310;JTAG

引 言

伯克利大学于2014年发布了开源指令集架构RISC-V,其目标是成为指令集架构领域的Linux,应用覆盖IoT(Internet of Things)设备、桌面计算机、高性能计算机等众多领域[1]。RISC-V自发布以来受到多方关注与参与,围绕RISC-V的生态环境逐渐完善,并涌现了众多开源处理器及SoC(System on Chip),其采用RISC-V架构,其中Rocket-Chip就是由伯克利大学发布的基于RISC-V的可配置SoC,通过配置不同的参数可以得到不同性能、应用不同场合的SoC。RISC-V的迅速发展还激励其设计人员成立了SiFive公司,专注于定制化SoC设计,其产品线如下:

① 开源处理器核Coreplex IP系列。包括Coreplex U、Coreplex E两个系列。其中Coreplex U系列目前有U5 Coreplex子系列,其是64位RISC-V架构处理器,支持多核、多级缓存、硬件支持的单精度与双精度浮点运算;Coreplex E系列目前有E3 Coreplex子系列,其是32位的RISC-V架构处理器,依据应用环境可配置支持RV32E、乘法、除法、浮点运算等,目标是低功耗的嵌入式控制器。

② 开源SoC Freedom系列:包括Freedom Unleashed、Freedom Everywhere两个系列。其中Freedom Unleashed系列是基于U5 Coreplex的SoC,包括U500子系列,其外设控制器包括DDR3/DDR4 DRAM 控制器、PCIe 3.0控制器、1 Gb Ethernet控制器、USB 3.0控制器等,支持Unix等多种操作系统;Freedom Everywhere系列是基于E3 Coreplex的SoC,包括E300子系列,其具有片上Debug单元、平台级中断控制器等,支持FreeRTOS等多种操作系统。

③ Freedom E310。Freedom E310是Freedom Everywhere的子系列E300的一个流片实例,目标应用场合是微控制器、IoT、可穿戴设备等,其处理器核是E3 Coreplex子系列的一个实例——E31,支持RV32IMAC指令集[2]。其采用180 nm工艺流片成功,主频可以达到320 MHz以上。

④ 开源开发板HiFive1。HiFive1是第一款采用Freedom E310作为核心控制芯片的Arduino兼容开发板。作为深度开源的代表,其微控制器对应的RTL代码、电路图设计文件、PCB设计文件等完全开源。

本文首先简单分析了Freedom E310的调试模块,随后设计了使用OpenOCD(Open On-Chip Debugger)、J-Link搭建Freedom E310调试环境的方案,并进行了验证测试。

1 Freedom E310介绍

1.1 Freedom E310的组成

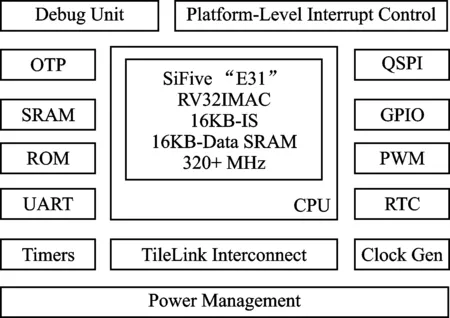

Freedom E310的组成如图1所示。处于核心的是单发射、顺序执行处理器E31,支持RV32IMAC指令集,具有16 KB的指令缓存、16 KB的数据SRAM,在满足一定工艺条件下的最高主频可达320 MHz。

图1 Freedom E310的组成

Freedom E310有多个外设,通过TileLink互连总线将这多个外设连接到处理器。主要外设包括[3]:

① AON(Always-on Domain):AON的意思就是始终在线,不受处理器核心电源管理的影响,包括实时计数器、看门狗、复位与电源管理部分。

② GPIO(General Purpose Input/Output)控制器:通用输入输出,每一个引脚都可以设置成输入或者输出,并可以设置是否能够引发中断。E31的GPIO可以复用,复用为UART、I2C、SPI、PWM等。

③ PLIC(Platform-Level Interrupt Control):平台级中断控制器,用于接收外部的中断信号,然后按照优先级送给处理器,支持52个外部中断源、7个中断优先级。

④ Debug Unit:调试单元,支持外部调试器通过标准JTAG接口进行调试,支持2个硬件断点、观察点。

⑤ QSPI(Quad-SPI):QSPI Flash控制器,用于访问Flash,可以支持eXecute-In-Place模式。

1.2 Debug单元

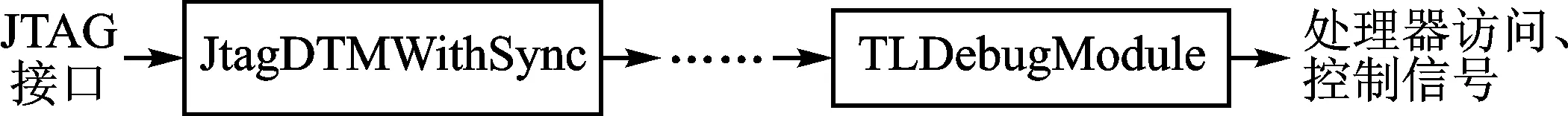

Debug单元的主要结构如图2所示。Freedom E310有一个标准的JTAG(Joint Test Action Group)接口,如表1所列。外部调试工具可以通过该接口进行调试,包括设置断点、设置观察点、单步执行、查看寄存器、访问存储器等操作,所有的外设、中断控制器也可以通过JTAG接口进行访问。外部调试工具将调试命令(如:设置断点)通过JTAG接口送入Freedom E310,后者有两个主要的模块处理该命令,首先是JtagDTMWithSync模块,该模块的作用是将按照JTAG协议的要求分析JTAG接口送入的命令,其内部有一个状态机,实现了TAP(Test Access Port)控制器,可以将其理解为一个串行转并行接口。提取出的指令经过一系列处理,最后送入TLDebugModule模块,该模块按照调试命令,对处理器发出实际的控制信号。

图2 Debug单元的主要结构

表1 Freedom E310的JTAG接口

2 OpenOCD介绍

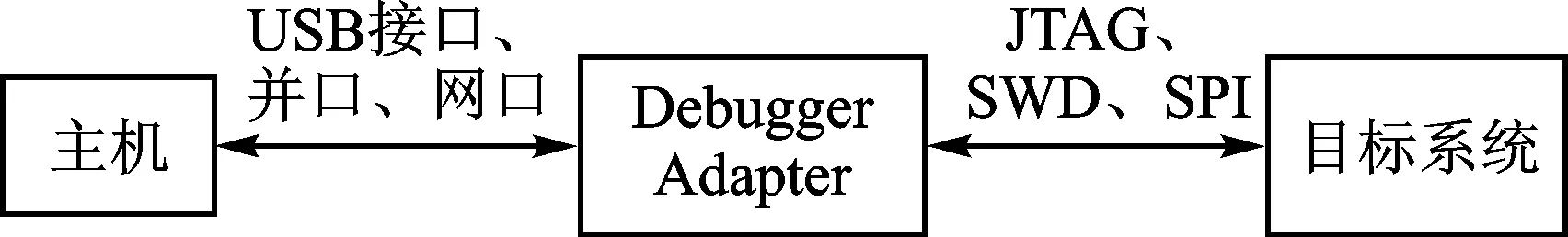

OpenOCD起源于2005年的奥格斯堡应用科学大学,并迅速发展成为一个应用广泛的开源项目,其目标是为嵌入式系统提供调试、在系统编程、边界扫描测试等功能。使用OpenOCD调试嵌入式系统的一般结构如图3所示。

图3 使用OpenOCD调试嵌入式系统的一般结构

OpenOCD运行于调试主机上,调试主机可以通过USB、并口、网口等方式连接到调试适配器,调试适配器再通过JTAG、SWD(Serial Wire Debug)、SPI(Serial Peripheral Interface)等接口连接到目标系统。此处的调试适配器的主要作用就是接口协议转换,比如:将主机通过USB接口送出的调试命令转化为JTAG信号,送入目标系统。OpenOCD支持大量的调试适配器,其中就包括J-Link。

3 J-Link调试适配器

J-Link功能十分丰富,是一款仿真器,但是本文只是将其作为一个调试适配器使用。J-Link 是 SEGGER 公司为支持仿真 ARM 内核芯片推出的 JTAG仿真器,配合 IAR EWARM、ADS、KEIL、WINARM、RealView 等集成开发环境,支持所有 ARM7/ARM9 内核芯片的仿真。其主要特性如下[4]:支持所有ARM7/ARM9内核的芯片,以及Cortex-M3,包括Thumb模式,下载速度为ARM7——600 KB/s,ARM9——550 KB/s;最高JTAG速度为12 MHz;目标板电压范围为1.2~3.3 V,兼容5 V;自动速度识别功能;监测所有JTAG信号和目标板电压;完全即插即用;使用USB电源(但不对目标板供电);带USB连接线和20芯扁平电缆;支持多JTAG器件串行连接;标准20芯JTAG仿真插头;选配14芯JTAG仿真插头;带J-Link TCP/IP server,允许通过TCP/ IP网络使用J-Link。

4 Freedom E310调试方案设计

4.1 整体结构

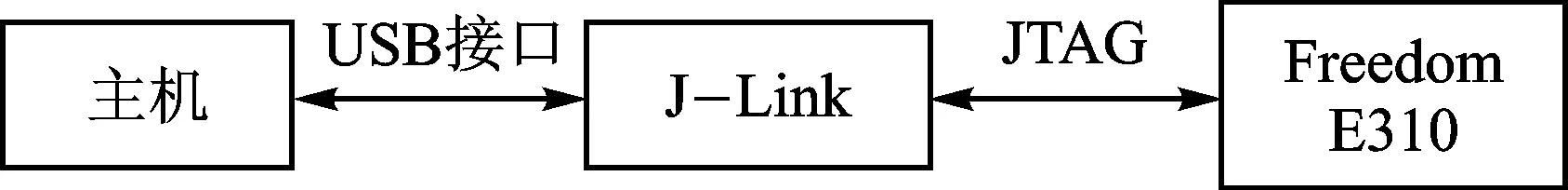

本文设计使用OpenOCD、J-Link对Freedom E310进行调试,整体结构设计如图4所示。OpenOCD运行在主机上,主机通过USB接口连接J-Link,后者通过JTAG接口连接Freedom E310。J-Link接收OpenOCD通过USB口送入的调试指令,然后通过JTAG接口送入Freedom E310,并将Freedom E310的响应信息传递给OpenOCD。

图4 Freedom E310调试方案整体结构

4.2 J-Link与Freedom E310的连接

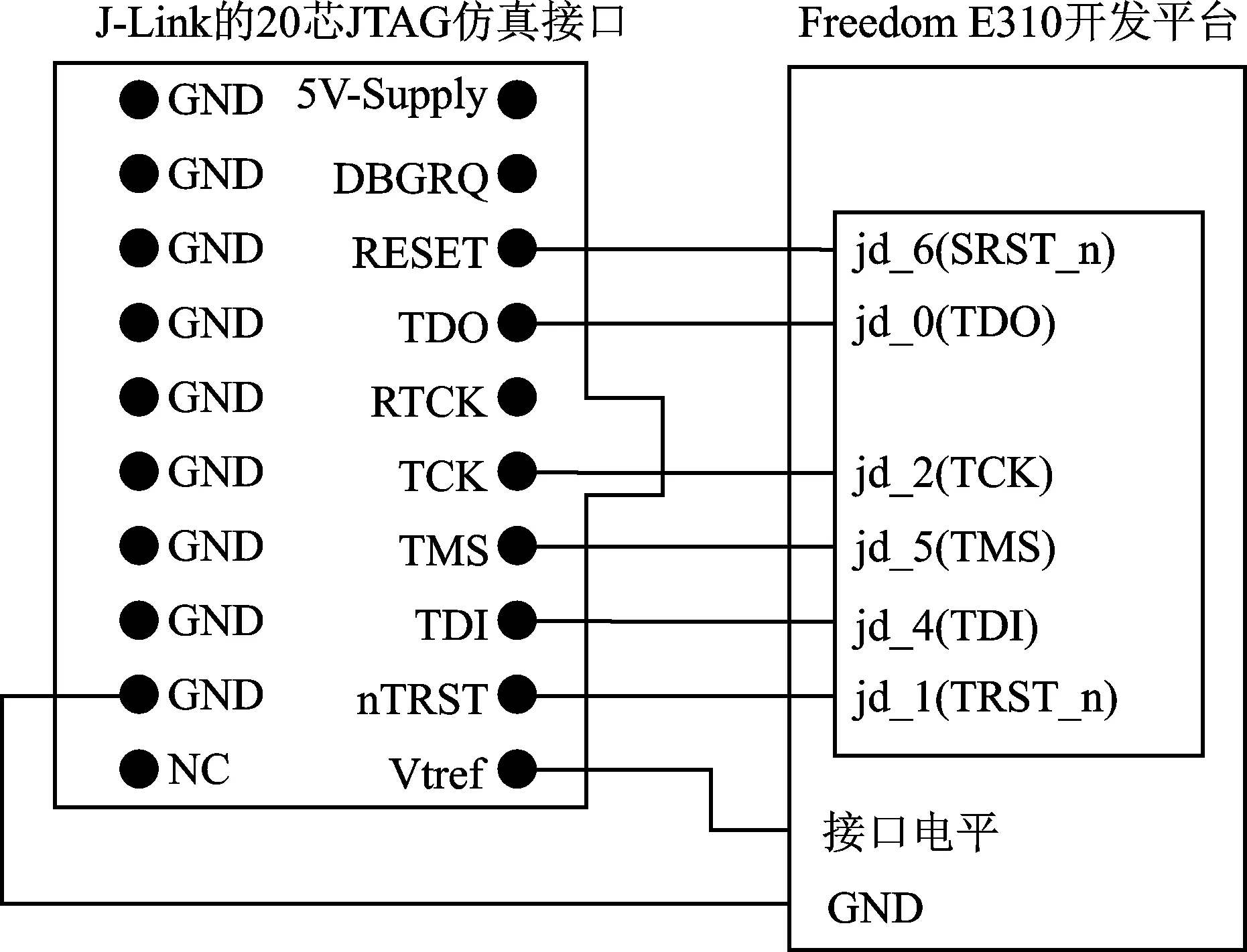

J-Link与Freedom E310之间通过JTAG接口连接,J-Link提供了一个20芯的JATG仿真插头。J-Link与Freedom E310连接时的针脚对应关系如图5所示。图中Vtref的输入是开发平台上IO口的输出高电平的值。

图5 J-Link的20芯仿真接口与Freedom E310的连接关系

4.3 OpenOCD配置文件设计

OpenOCD需要针对不同的调试适配器和不同的目标芯片,编写一个配置文件。配置文件一般包括4个部分[5]:

① 接口配置:与调试适配器有关,配置其使用的接口等信息。

② 开发板配置:与具体开发板有关的配置信息,可以配置上面的模块(如CPU、SDRAM、Flash等)的初始化过程。

③ 目标芯片配置:与具体芯片有关的配置信息,芯片需要具有JTAG TAP,如ARM、CPLD等,如果一个目标有多个TAP,那么需要在此处明确说明。

④ 补充配置:一些可能会使用到的库文件等信息。

本文只是调试Freedom E310,并不需要开发板相关信息,所以开发板配置可以省略。在目标芯片配置中,需要添加具体芯片的JTAG TAP,然后添加芯片。本文设计的调试Freedom E310的配置文件内容如下:

#接口配置,这里指出使用J-Link

interface jlink

#JTAG接口的最大频率

adapter_khz 12000

#添加一个新的JTAG TAP

set _CHIPNAME riscv

jtag newtap $_CHIPNAME cpu-irlen 5-expected-id 0x10e31913

#添加一个新的CPU

set _TARGETNAME $_CHIPNAME.cpu

target create $_TARGETNAME riscv-chain-position $_TARGETNAME

init

#输出一些信息

echo " "

echo "-----------------------"

echo "--- login with - telnet localhost 4444 ---"

echo "---hello world ---"

echo "-----------------------"

echo " "

#使目标CPU暂停执行

halt

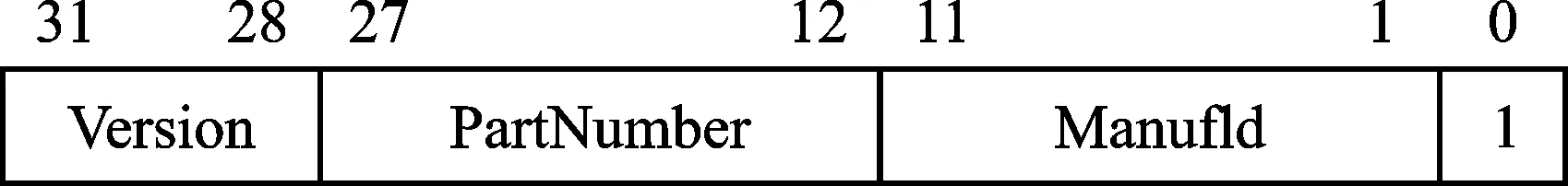

在添加JTAG TAP的时候,指出了这个TAP的指令寄存器的宽度是5位,并且IDCODE寄存器的值是0x10e 31913,当OpenOCD与目标连接的时候,会尝试获取IDCODE寄存器,然后与此处的对比,判断是否一致。IDCODE寄存器的定义如图6所示[6]。

图6 IDCODE寄存器的定义

包含三个部分:Version为版本号;PartNumber为部件号;Manufld为设计者或者制造者编码。

在Freedom E310的DebugTransportModuleJtag.v中定义了IDCODE寄存器,如下正是在OpenOCD配置文件中的值:

parameter JTAG_VERSION=4'h1;

parameter JTAG_PART_NUM=16'h0E31; // E31

parameter JTAG_MANUF_ID=11'h489; // As Assigned by JEDEC

assign idcode={JTAG_VERSION, JTAG_PART_NUM, JTAG_MANUF_ID, 1'h1};

5 使用OpenOCD、J-LINK调试Freedom E310

5.1 实验环境

本文将Freedom E310下载到Altera的DE2上运行,通过DE2的GPIO口与J-Link连接。运行OpenOCD的PC机使用的是Ubuntu14.04 64位。在Github上clone项目Freedom-e-sdk,通过编译可以得到OpenOCD可执行文件。

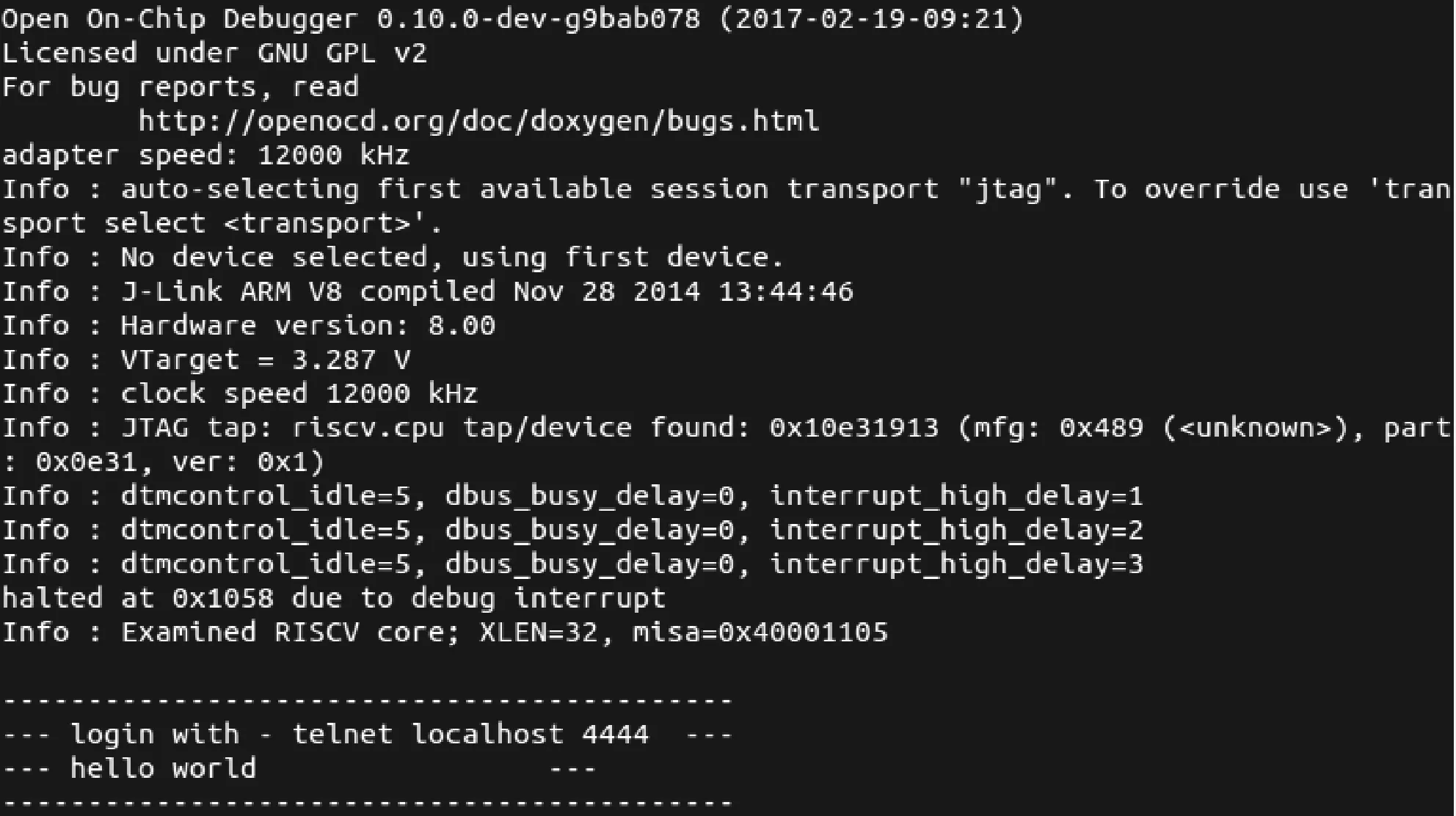

5.2 运行OpenOCD

假设3.3节设计的OpenOCD配置文件是openocd.cfg,那么在Ubuntu上输入如下指令,可以运行OpenOCD。

freedom-e-sdk/toolchain/bin/openocd-f openocd.cfg

显示如图7所示,表示已经正确识别Freedom E310。

图7 OpenOCD运行输出

5.3 运行Telnet

OpenOCD运行后,可以使用Telnet连接本地主机的4444端口,如图8所示。

图8 Telnet运行界面

4.4 执行调试指令

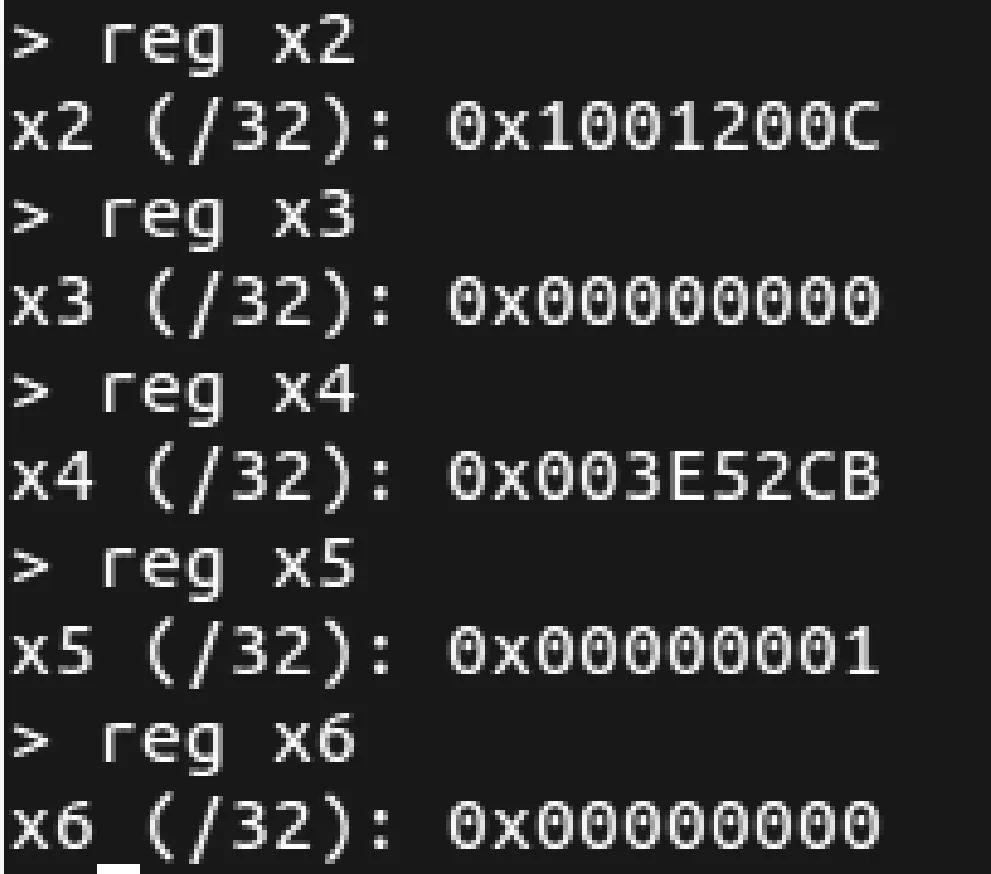

Telnet运行后,可以在其中输入各种调试指令,如:暂停运行(halt)、继续运行(resume)、单步执行(step)、查看寄存器(reg)、设置断点(bp)等。图9为运行查看寄存器指令的结果。

图9 运行查看寄存器指令

结 语

[1] Andrew Waterman, Yunsup Lee, David A. The RISC-V Instruction Set Manual, Volume I: User-Level ISA, Version 2.1[EB/OL].[2017-03]. https://www2.eecs.berkeley.edu/Pubs/TechRpts/2014/EECS-2014-54.html.

[2] SiFive Inc. SiFive E3 Coreplex Series Manual, Version1.2, 2016.

[3] SiFive. SiFive FE310-G000 Manual, Version1.0.1, 2016.

[4] Debug Probes-J-Link and J-Trace [EB/OL].[2017-03]. https://www.segger.com/jlink-debug-probes.html.

[5] Open On-Chip Debugger: OpenOCD User’s Guide, for release 0.10.0-dev[EB/OL].[2017-03]. http://www.docin.com/p-1825816225.html.

[6] RISC-V External Debug Support, Version 0.13[EB/OL].[2017-03].https://dev.sifive.com/documentation/risc-v-external-debug-support-0-11/.2017-2.

雷思磊(工程师),主要研究方向为处理器架构、嵌入式处理器应用等。

Research on Open-source SoC Freedom E310 Debugging Method

Lei Silei,Xue Zheng

(Jiuquan Satellite Launch Center,Jiuquan 735000,China)

The Freedom E310 is the first open-source commercial SoC based on the RISC-V instruction set architecture,and it can be customized according to the specific depth of application scenarios.On the basis of a brief introduction of the Freedom E310 and its Debug unit,the Freedom E310 debugging environment is established through the OpenOCD,J-Link,and it has carried on the actual test.

RISC-V;Freedom E310;JTAG

TP368.1

A

�迪娜

2017-03-13)