适用于超宽带系统的低功耗CMOS频率合成器研究*

李建伟

(长治学院电子信息与物理系,山西 长治 046000)

适用于超宽带系统的低功耗CMOS频率合成器研究*

李建伟*

(长治学院电子信息与物理系,山西 长治 046000)

针对脉冲无线电超宽频(IR-UWB)接收系统,提出了一种低功耗频率合成器设计。合成器的设计以一个整数N分频Ⅱ型四阶锁相环结构为基础,包括一个调谐范围为31%的7位压控振荡器,一组基于单相时钟逻辑的高速分频器。分频器能够合成8个由IEEE标准802.15.4a定义的频率。该集成频率合成器运用65 nm CMOS技术制造而成,面积为0.33 mm2,工作频率范围为7.5 GHz~10.6 GHz。测试结果显示,在1.2 V供电下,该合成器的3-dB闭环带宽为100 kHz,稳定时间为15 μs。测量相位噪声低于-103 dBc/Hz@1 MHz,抵消频率为1 MHz。杂散信号功率低于低于-58 dBc。相比其他先进的合成器,提出合成器的工作电流为5.13 mA,功耗仅为6.23 mW。

超宽带;锁相环路;频率合成器;低功耗;相位噪声

超宽带通信系统是一种短距离高速无线通信系统,具有抗多径、抗干扰、安全性高和传输速率高等特点,因此引起了大家的广泛关注。目前,大多数研究均采用基于单锁相环(PLL)或多锁相环结构来设计超宽带通信系统的频率合成器[1-2]。

多锁相环结构具有多个锁相环,每个锁相环产生一个需要的频点,然后,通过多路选择器在这些锁相环的输出中选择一路输出作为本振信号[3-4]。这类结构的优点在于输出信号的频谱利用率较高,原因在于每一个输出频率点都直接由锁相环产生。其缺点在于,多个锁相环导致了面积和功耗增大,故输出子带频率较少。单锁相环(单边带混频器)结构比较适合子带数多的情况,该主要包括一到两个锁相环和相应数量的分频器,产生若干偏移频率,然后,用单边带混频器将相应的偏移频率混频,从而得到目标频率[5-6]。

目前,大多数是针对多带正交频分复用(MB-OFDM)超宽带技术,即IEEE 802.15.3a标准。然而,本文研究是针对IEEE 802.15.4a标准的标准超宽带通信技术,其物理层协议[7]支持3个频段:(1)千兆赫以下的波段,由一个单频道组成,频谱范围在249.6 MHz~749.6 MHz之间;(2)低波段,由4个频道组成,频谱范围在3.1 GHz~4.8 GHz之间;(3)高波段,由11个频道组成,频谱范围在5.8 GHz~10.6 GHz之间。因此,本文提出了一种基于单锁相环路的频率合成器,可以产生8个由IEEE标准802.15.4a定义子带的中心频率,同时,改善了消耗功率,集成的合成器芯片面积也较小,相位噪声低于-103 dBc/Hz@1 MHz,频率转换时间满足超宽带系统的要求,小于5 ns。

1 提出的频率合成器设计

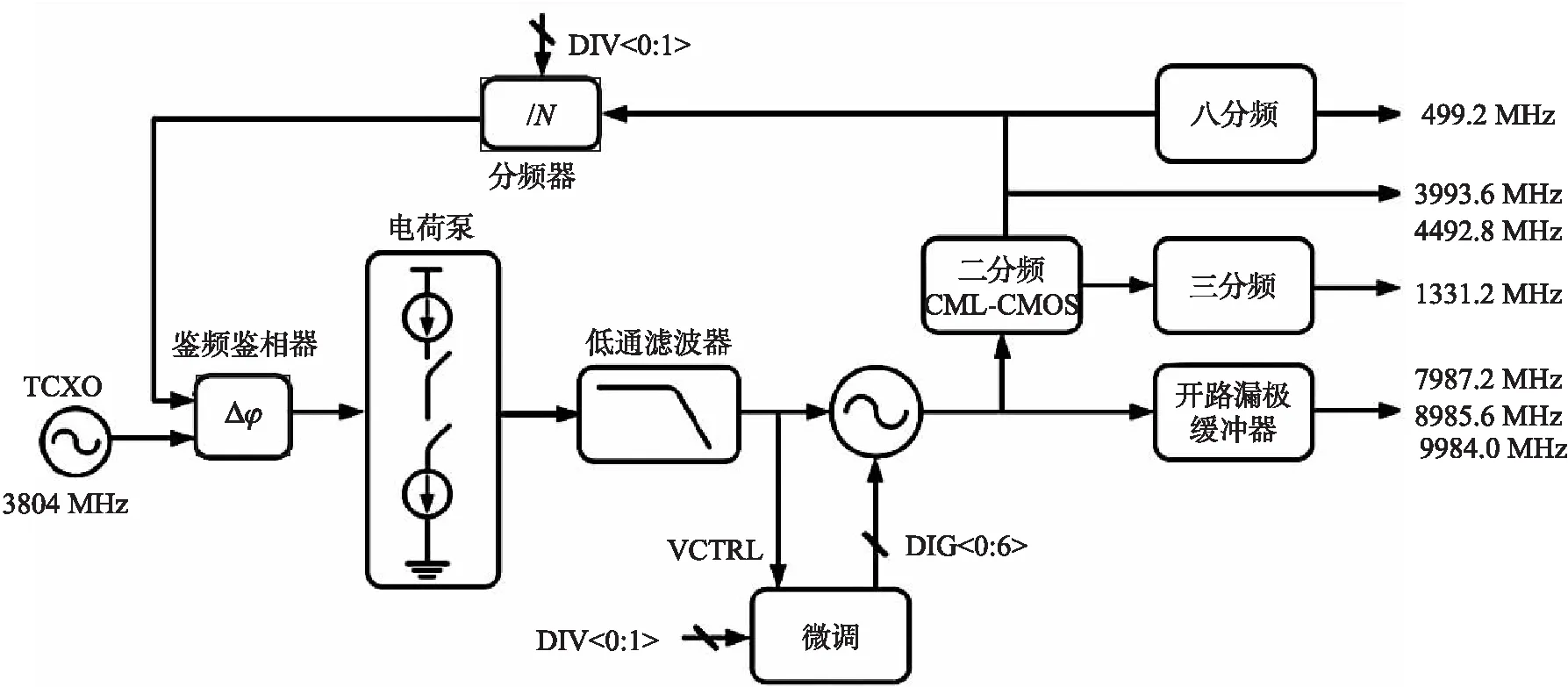

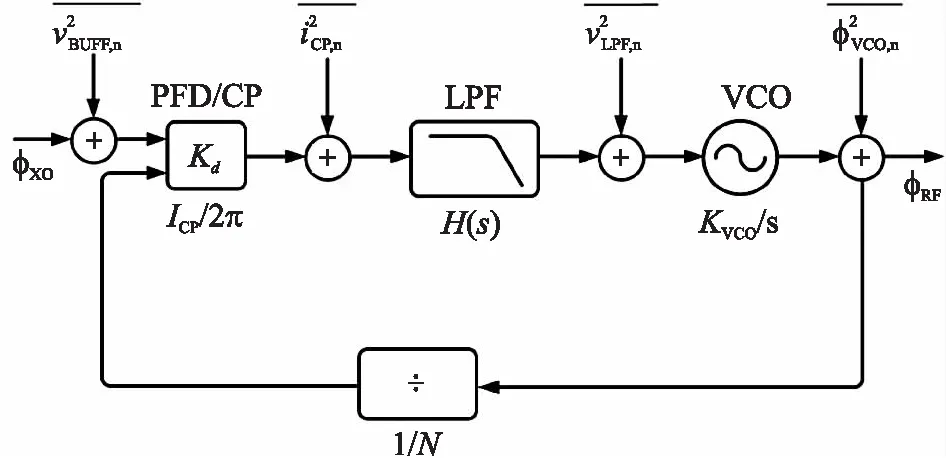

合成器的体系结构如图1中所示。

图1 提出的频率合成器结构示意图

整数-N合成器架构的输出选择取决于合成的输出频率分辨率(fOUT),是作为参考频率(fref)的倍数,fref由38.4 MHz温度补偿晶体振荡器(TCXO)产生:

fOUT=N×fref,(N=208,234,260)

(1)

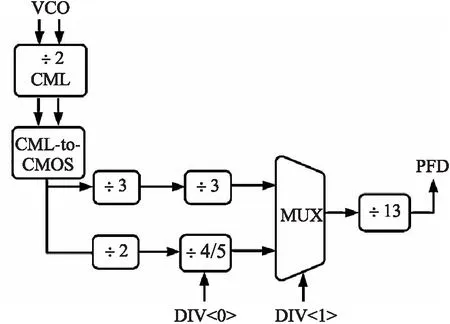

多子带的产生是通过压控震荡器(VCO)来实现,紧随其后的是一组高速分频器。压控震荡器还驱动电流型逻辑(CML)二分频电路,其后是从CML到CMOS生成输出波段。然后,由CMOS八分频器提供千兆赫以下频段(499.2 MHz)。2 bit可编程的CMOS分频器,额定分频参数范围在104~130之间,用于提供鉴频鉴相器PFD(Phase Frequency Detector)的反馈信号,合成1331.2 MHz载波(图1)。生成的频率499.2 MHz和1331.2 MHz作为6 bit模数转换器(ADC)的时钟信号,应用于脉冲无线电超宽频信道接收器中,如表1所示。为了不增加模数转换器的信噪比(SNR),抖动必须<3 ps[8-9]。

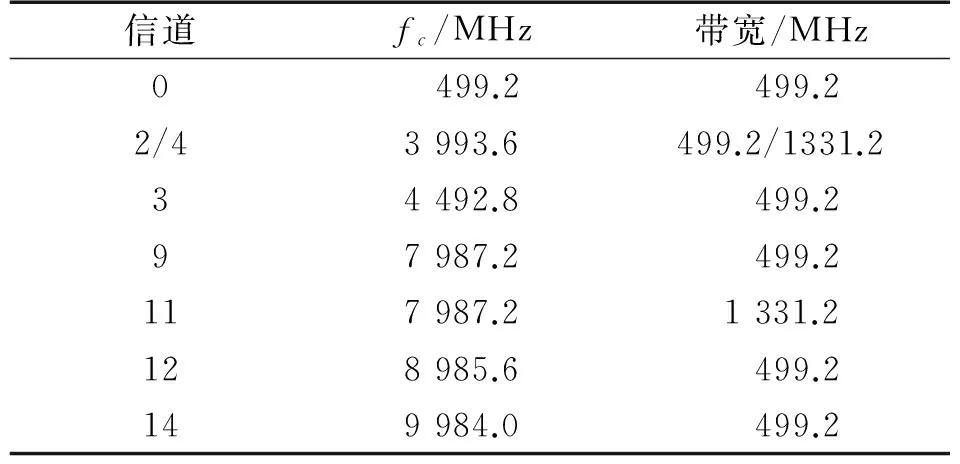

表1 IEEE 802.15.4.a的信道频率

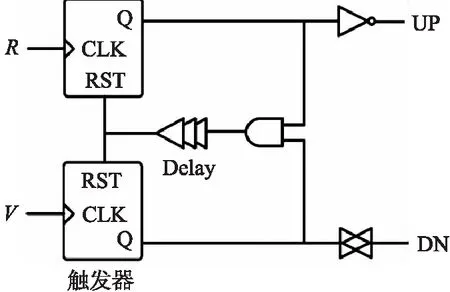

1.1 鉴频鉴相器

通过使用2个准确的单相时钟TSPC(True Single-Phase Clock)D触发器和一个静态互补AND(如图2所示)来实现鉴频鉴相器(PFD)。D触发器是正边缘触发,以便鉴频鉴相器根据输入信号的占空比延迟反应。一连串的CMOS逆变器组成两个缓冲区,通过该缓冲区每个向上和向下的输出信号都被用来供应电荷泵(CP),如图3所示。考虑到这种类型鉴频鉴相器的盲区问题会增加电路产生的抖动,因此从鉴频鉴相器输出的复位信号推迟了足够的时间,以便为向上和向下信号同时生成非常短暂的脉冲。盲区可以通过短暂的脉冲消除掉,而且检测较小相位差的能力也得以提高。

图2 鉴频鉴相器(PFD)的示意图

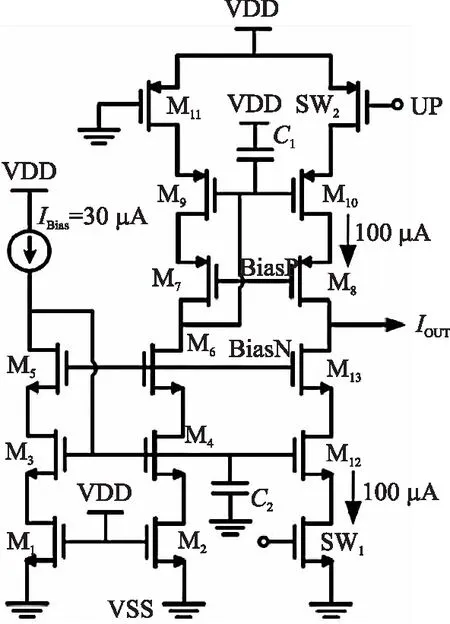

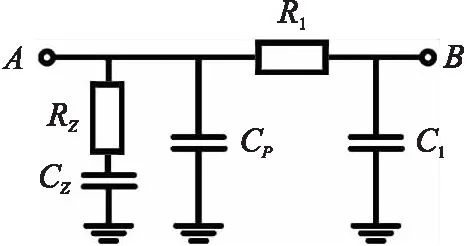

电流驱动型电荷泵电路如图3所示。电荷泵电流为100 μA。M10,M12形成共源共栅的电流镜,以便增加输出阻抗,因此,电流变化对输出电压不太敏感。SW1和SW2是电荷泵的两个开关,开关将切换不匹配和开机时间降到最低。M1,M2和M11用于复制偏压,当电荷泵开启时,提供同样的偏压条件。增加了C1和C2电容用于减少电荷耦合,电容有助于提高开关速度。通过适当的偏置(BiasP=400 mV,BiasN=800 mV),将输出电压范围比0.2 V至1 V更广,全程的供应电压为1.2 V。设计的芯片上三阶环路滤波器如图4所示。电容器Cp=6.7 pF和Cz=160 pF,以及电阻Rz=39 kΩ,因此锁相环回路带宽为100 kHz和相位裕度为55°,而电容C1=2.53 pF和电阻R1=100 kΩ。

图3 电荷泵电路原理

图4 三阶无源环路滤波器(LP)

图5 N分频器的示意图

1.2 可编程的N分频器

可编程的N分频器如图5所示。这个电路由一个D触发器(DFF)组成,使用CML模块来实现,从其差分输出OUT/OUT反馈回到它的输入端。每个CML模块仅消耗100 μA,电阻负载为2.5 kΩ。在第1次分频后,使用一个CML-to-CMOS缓冲器。这是一种推挽式输出运算放大器和再生逆变器。图6为基于D触发器的CMOS时钟分频器设计。

图6 基于D触发器的CMOS时钟分频器

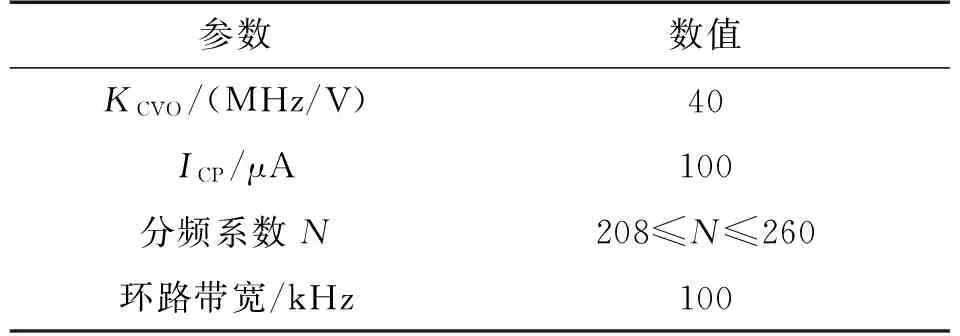

一个可编程的CMOS分频器应用了TSPC触发器,使用的额定分频因数为104,117和130,用于提供鉴频鉴相器的反馈信号。基于触发器的典型静态分频器具有16个晶体管,与之相比,TSPC电路只包含10个晶体管,因此分频器的实现有些紧凑。此外,TSPC逻辑本身的功耗低[10-12]。表2总结了主合成器的环路参数。

表2 主要的合成环路参数

ICP表示电荷泵在其开启状态下的电流。

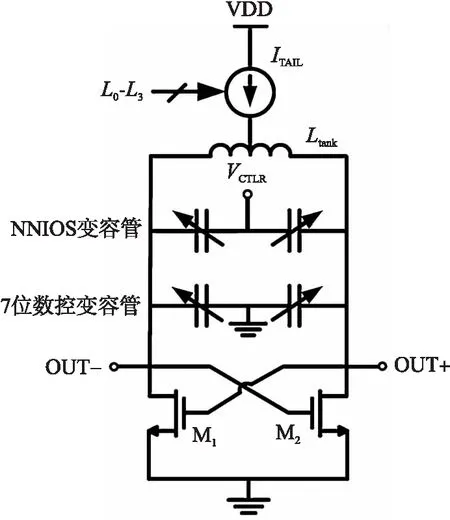

1.3 NMOS交叉耦合压控振荡器

压控振荡器采用只有NMOS交叉耦合的拓扑结果,用于最小电容寄生,即最大的调谐范围,如图7所示。谐振器电感450 pH,估算的品质因数为24,共振频率为65 GHz。为了限制调谐增益(Kvco),有利于干扰抑制和最小化噪声影响,振荡频率由七位数控MIM变容管粗略控制。精确的频率调谐由NMOS变容二极管提供。通过电感的中央分接头为振荡器提供电流。共模电压设置为VDD/2,调谐电压范围在200 mV到1 V之间。因此,压控震荡器的调谐范围为7.5 GHz~10.6 GHz(31%的调谐范围),在1.2 V的电压下,电流为2.5 mA。在100 kHz的抵消模拟相位噪声<-90 dBc/Hz。

图7 LC压控振荡器(七位数控变容管用于粗调,NMOS变容管用于细调)

2 相位噪声分析

在锁相环路中带宽约为100 kHz,关键的噪声源由电荷泵、低通滤波器(LPF)、压控振荡器和缓冲器造成。相位噪声的模型是基于文献[11]提出的线性解析模型。图8显示了锁相环路的线性模型。循环过滤互阻抗表示为H(s),压控振荡器增益表示为KVCOψs。N是锁相环路的分频比例。

图8 锁相环路线性模型

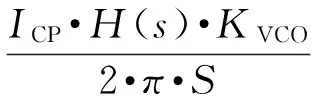

开环传递函数表示为:

(2)

根据图4显示的三阶滤波器,我们得到的互阻抗表示如下:

(3)

式中:

(4)

而且,

(5)

接下来,推导每个噪声的输出噪声频谱:

(6)

(7)

(8)

(9)

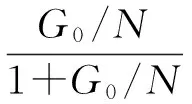

式中:G表示传递函数,由以下公式计算得出:

(10)

每个噪声的功率谱密度分别为LBuff(f),LCP(f),LLPF(f)以及LVCO(f)。整个锁相环路的相位噪声由以下公式计算得出:

(11)

(12)

式中:我们使用f1=1 kHz和f2=10 MHz作为集成限制值。

3 测量结果

运用TSMC 65 nm CMOS工艺对提出的频率合成器进行设计与制造。图9显示了芯片的照片和测量环境,面积为450 μm×750 μm(0.33 mm2)。

图9 芯片照片和测量环境

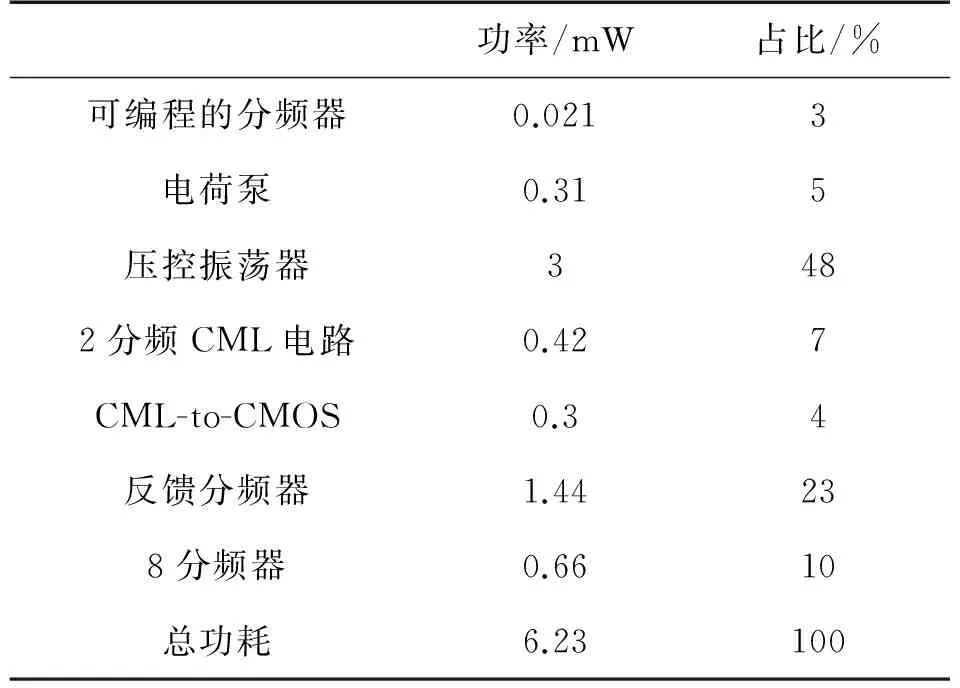

应用安捷伦N9010A EXA分析仪来测量芯片参数。在1.2 V的电源电压条件下,该合成器消耗的电流为5.13 mA。每个模块消耗的功率如表3所示。开漏级输出缓冲器的使用仅仅是出于测量的目的,消耗了5 mA。

表3 频率合成器的各模块功耗和占比

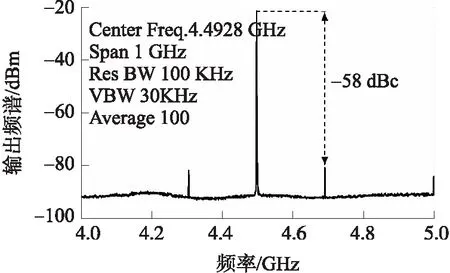

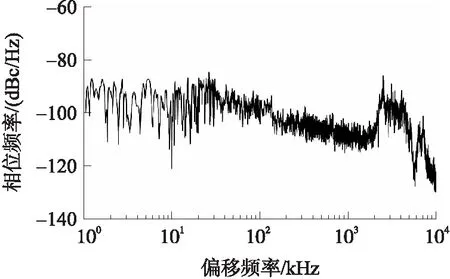

频率合成器使用38.4 MHz的TCXO作为参考,相位噪声为-130.6 dBc/Hz@1 MHz。图10显示了合成器在4492.8 MHz时的输出光谱。可以看出电路能够较好的抑制输出杂散。频率合成器输出信号中的杂散信号功率低于-58 dBc。图11显示了测量的相位噪声性能。

图10 频率合成器子带频率输出频谱

图11 测量的相位噪声性能

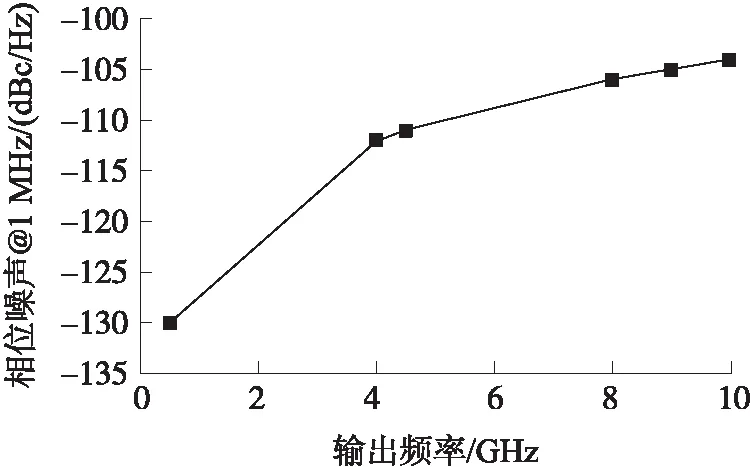

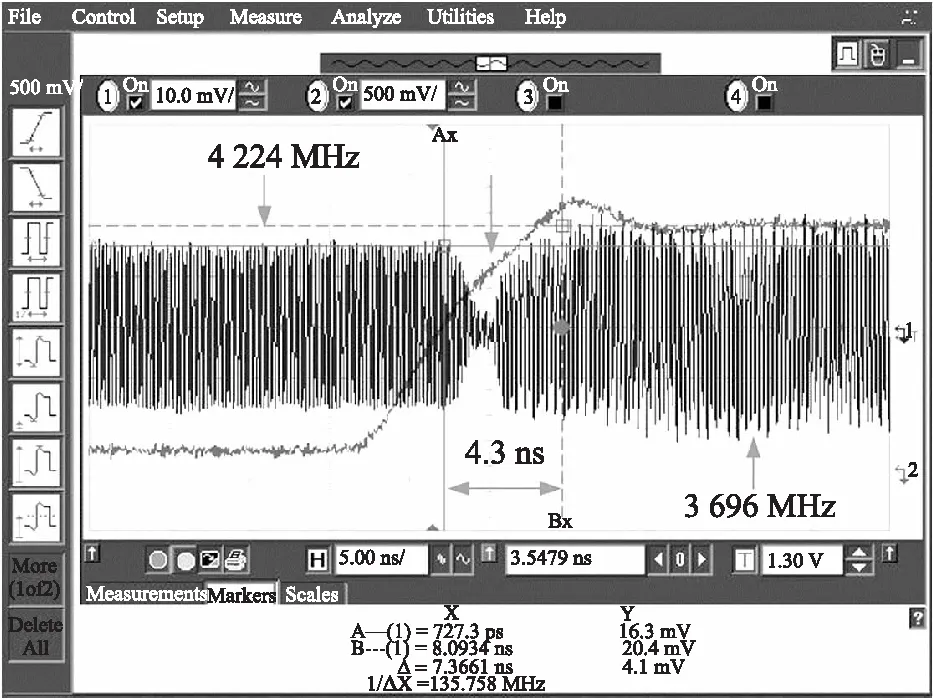

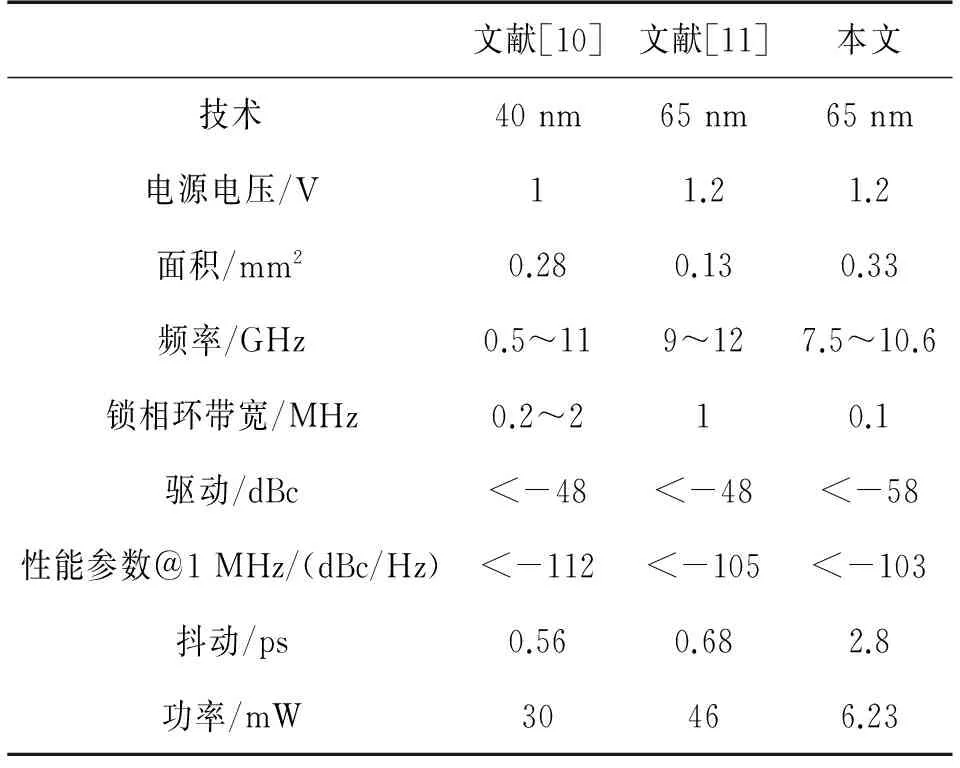

图12描绘了0.5 GHz~10 GHz合成输出频率的相位噪声。图13显示了该频率合成器中的频率转换时间。从图中可以出其频率转换时间为4.3 ns,满足超宽带标准的要求(小于9 ns)。表4总结了提出的合成器的测量性能,并且与目前的发展水平作比较。

图12 0.5 GHz~10 GHz@1 MHZ合成输出频率的相位噪声结果

图13 频率合成器频率转换时间

文献[10]文献[11]本文技术40nm65nm65nm电源电压/V11.21.2面积/mm20.280.130.33频率/GHz0.5~119~127.5~10.6锁相环带宽/MHz0.2~210.1驱动/dBc<-48<-48<-58性能参数@1MHz/(dBc/Hz)<-112<-105<-103抖动/ps0.560.682.8功率/mW30466.23

4 结论

本文提出了一种低功耗的超带宽频率合成器,适用于于零脉冲无线电超宽频(IR-UWB)接收器。在IEEE 802.15.4a所定义的0.5 GHz~10 GHz的频率范围内生成8个带宽。测量的参考边带大约为58 dB,低于载波,测量的相位噪声低于-103 dBc/Hz@1 MHz。相比其他先进的合成器,提出合成器的工作电流为5.13 mA,功耗仅为6.23 mW。此外,需要注意的是,每个噪声源的封闭相位噪声性能由分频比例N放大。因此,未来需要做的改进应该集中精力于改善外部参考输入缓冲器和压控振荡器的运行状况。

[1] Zhou B,Wang J. High-Robust Relaxation Oscillator with Frequency Synthesis Feature for FM-UWB Transmitters[J]. Journal of Semiconductor Technology and Science,2015,15(2):202-207.

[2] Ojani A,Mesgarzadeh B,Alvandpour A. Modeling and Analysis of Harmonic Spurs in DLL-Based Frequency Synthesizers[J]. IEEE Transactions on Circuits and Systems I Regular Papers,2014,61(11):3075-3084.

[3] Anghel A,Vasile G,Cacoveanu R,et al. Short-Range Wideband FMCW Radar for Millimetric Displacement Measurements[J]. IEEE Transactions on Geoscience and Remote Sensing,2014,52(9):5633-5642.

[4] Doll A,Qi M,Pribitzer S,et al. Sensitivity Enhancement by Population Transfer in Gd(ⅡI)Spin Labels[J]. Physical Chemistry Chemical Physics,2015,17(11):7334-44.

[5] 李智鹏,刘永智,徐铭海,等. 基于级联式偏置锁相环的低相噪宽带频率合成器简[J]. 微波学报,2014,30(6):9-13.

[6] Abiri E,Salehi M R,Salem S. A Low Phase Noise and Low Power 3 GHz~5 GHz Frequency Synthesizer in 0.18 μm CMOS Technology[J]. Microelectronics Journal,2014,45(6):740-750.

[7] 翟腾普,任丽香,刘泉华,等. 宽带PCSF雷达信号频率合成器的设计与实现[J]. 现代雷达,2015,37(9):67-70.

[8] 岳腾. 宽带频率源的设计与实现[D]. 北京:电子科技大学,2015.

[9] Ojani A,Mesgarzadeh B,Alvandpour A. A Self-Calibration Technique for Fast-Switching Frequency-Hopped UWB Synthesis[C]//Mixdes-International Conference Mixed Design of Integrated Circuits and Systems,2014:154-159.

[10] Khatri V,Banerjee G. A 0.5 GHz~2.0 GHz Injection Locked Oscillator Cascade for Parallel Wideband RF Spectrum Sensing[J]. Analog Integrated Circuits and Signal Processing,2015,84(1):29-42.

[11] Lou W,Liu X,Feng P,et al. An Integrated 0.38 GHz~6 GHz,9 GHz~12 GHz Fully Differential Fractional-N Frequency Synthesizer for Multi-Standard Reconfigurable MIMO Communication Applica-tion[J]. Analog Integrated Circuits and Signal Processing,2014,78(3):807-817.

[12] 付钱华,易淼. DDS激励PLL高性能频率合成器设计[J]. 电子器件,2016,39(1):62-66.

ResearchonLowPowerCMOSFrequencySynthesizerforUltraWideBandSystem*

LIJianwei*

(Department of Electronic Information and Physics,Changzhi University,Changzhi Shanxi 046000,China)

A low power frequency synthesizer design is proposed for the impulse radio ultra wideband(IR-UWB)receiving system. The synthesizer is designed on the basis of an integer N frequency division Ⅱ type four order phase locked loop structure,which includes a 7 bit voltage controlled oscillator with a tuning range of 31%,and a set of high speed frequency divider based on single phase clock logic. The frequency divider is capable of synthesizing eight frequencies defined by the IEEE standard 802.15.4a. The integrated frequency synthesizer is made with 65 CMOS nm technology,with an area of 0.33 mm2and a working frequency range of 7.5 GHz~10.6 GHz. Test results show that under the 1.2 V power supply,the synthesizer’s 3-dB closed loop bandwidth is 100 kHz,and the stability time is 15. Measured phase noise is less than dBc/Hz@1 MHz-103,the offset frequency is 1 MHz. The spurious signal power is below dBc-58. Compared to other advanced synthesizer,the synthesizer’s operating current is 5.13 mA,the power consumption is only 6.23 mW.

ultra wide band;phase locked loop;frequency synthesizer;low power consumption;phase noise

10.3969/j.issn.1005-9490.2017.06.004

项目来源:长治学院校级科学研究项目(2013203)

2016-10-29修改日期2016-12-08

TN925

A

1005-9490(2017)06-1348-06

李建伟(1979-),男,汉族,山西省长治市,硕士,讲师,主要研究方向为电子电路设计,ljw_1979@163.com。