基于自定义协议的机载数据记录仪控制系统设计

穆蔚然,靳 鸿,张志伟

(中北大学 电子测试技术国家重点实验室 仪器科学与动态测试教育部重点实验室,太原 030051)

在飞行器飞行试验中,机载数据记录仪作为重要的记录设备,记录着飞行器的重要工作环境参数和飞行动态参数。随着机载数据传输速度以及数据量的不断增加,多通道、大容量、高存储速度成为现代记录仪发展的主流趋势[1-2]。另外各通道之间信号类型的多样性和功能的复杂性使得整个存储系统更加庞大,多通道多任务管理复杂。而且机载环境下的存储设备、测试参数具有实时性强的存储要求[3]。因此需要一套实时性强、可靠性高的控制系统实现对机载数据记录仪多通道记录模块的统一管理,实现参数高速存储记录。

目前数据记录仪控制系统大多基于Linux、Unix等通用操作系统,与PCI等计算机标准总线接口[4-6]。通用PCI/CPCI、PXI总线标准采用分时复用的工作模式[7-8],同一时刻只允许一个采集终端拥有总线的使用权,所以系统总线的数据传输速度取决于当前优先级最高的采集终端,限制了系统整体的存储速率。操作系统自身的消耗势必会造成总线数据传输带宽的降低[9]。由于大多通用操作系统多任务非实时响应的特点,当多个任务同时执行时,影响数据总线传输和存储性能[10],虽然具有操作简单、通用性强和易于实现等优点但难以满足机载环境下对存储系统的实时性和可靠性要求。

1 控制系统总体设计

基于自定义协议的机载数据记录仪控制系统采用非标准总线来实现对各记录模块的控制。系统采用STM32F103单片机和FPGA作为主控制器,STM32对接口板卡的RS422指令数据进行解析,FPGA是整个系统指令的管理中心和数据的传输媒介,STM32通过配置和读取FPGA内部的寄存器实现系统各项功能。各通道记录模块相互独立且实时并行记录。

机载数据记录仪有上位机控制与1553B总线数据流2种控制模式,采用1553B总线数据流控制模式时,通过机载/地面计算机发送1553B总线数据流控制记录仪的工作。使用上位机控制模式时,通过上位机控制管理记录仪的工作,实现存储数据的上传。

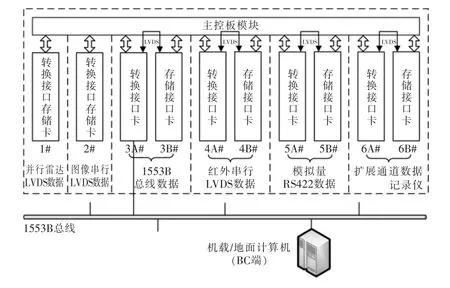

该数据记录仪采用了按照功能划分的插卡式模块化设计结构[11],将LVDS记录模块、模拟量记录模块、1553B总线记录模块、RS422总线记录模块进行整合。LVDS传输方式实现各通道记录模块存储数据的高速上传。使用RS422总线实现主控制板卡与各通道记录模块之间以及与上位机之间指令的通讯。各子板模块通过主控板卡连接、控制、传递各通道的信号。在主控板卡的控制下,协调统一各子板工作。整个系统具有扩展功能预留扩展插槽,记录仪总体结构组成示意如图1所示。

2 控制系统双模式控制方案设计

图1 记录仪总体结构组成示意Fig.1 Recorder overall structure diagram

机载数据记录仪有上位机与1553B总线数据流2种控制模式,在进入相应的工作模式前,需要在上位机控制模式下通过上位机对记录仪各通道记录模块进行上电配置,选择相应的控制模式。当记录仪采用1553B总线数据流控制模式时,通过机载/地面计算机发送1553B总线数据流控制记录仪的工作,此控制模式适用于机载环境和地面环境;当记录仪采用上位机控制模式时,通过上位机控制管理记录仪的工作,并实现存储数据上传的功能,此控制模式适用于地面环境。

2.1 上位机控制模式设计

上位机控制模式下的系统结构组成示意如图2所示,上位机通过2个USB接口与双通道数据转换控制卡连接,其中USB1接口与芯片CY7C68013进行通信[11],将双通道数据转换控制卡读到的数据回传给上位机;USB2通过CP2102(RS232)来接收和下发配置和控制指令。发送“下载”命令后,双通道数据转换控制卡收到上位机命令后通过RS422接口与主控板卡进行通信;主控板卡收到双通道数据转换控制卡转发的命令后,主控板卡FPGA从子板的存储单元中读取数据,通过LVDS接口向双通道数据转换控制卡发送数据。双通道数据转换控制卡收到数据后会判断数据是否有效,若有效则将数据写入缓存,上位机发送读数请求将缓存中数据存储至计算机硬盘,进行后续分析处理。

图2 上位机控制模式下的系统结构组成示意Fig.2 Host computer control mode composition of the system structure

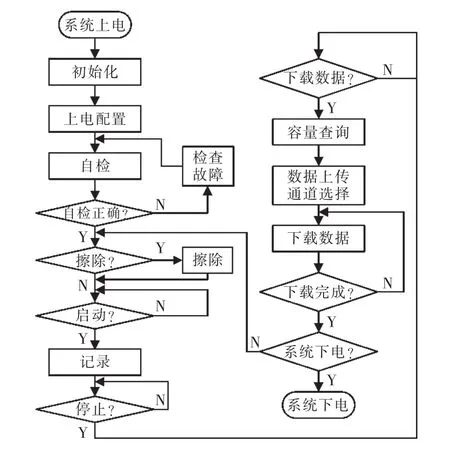

上位机控制模式下的系统工作流程如3所示,连接记录仪与上位机。通过上位机对记录仪各通道记录模块进行电源配置,配置信息将保存至主控板卡上。上位机操作记录仪进行自检,自检通过则表明初始配置设置正确。如未通过,则需检查相关配置是否与使用状态一致。当自检通过后,主控板卡根据上位机控制指令对子板进行操作。

图3 上位机控制模式下系统工作流程Fig.3 System workflow under the control mode of host computer

2.2 1553B总线数据流控制模式设计

1553B总线数据流控制模式下的系统结构组成示意如图4所示。1553B接口子板是实现这一控制模式的主要模块,1553B接口子板主要功能是将1553B消息命令转换为RS422通讯指令,1553B接口子板接收到机载/地面计算机(BC端)的1553B消息命令后转换成相应的RS422通讯指令,发送给主控板卡,主控板卡接收到对应的RS422通讯指令后控制记录仪的工作。

图4 1553B总线数据流控制模式下的系统结构组成示意Fig.4 Schematic diagram of the system structure under the 1553B bus data flow control mode

1553B总线数据流控制模式下的系统工作流程如图5所示。数据记录仪与上位机连接,通过上位机对记录仪各通道存储模块进行电源配置,配置信息将保存至主控板卡上。上位机发送自检指令,记录仪进行自检,若通过则表明初始配置设置正确。自检通过后连接记录仪与机载/地面计算机,数据记录仪进入1553B总线数据流控制模式,主控板卡根据1553B接口子板传来的控制指令对其余子板卡进行操作。

图5 1553B总线数据流控制模式下系统工作流程Fig.5 System workflow under 1553B bus data flow control mode

3 控制管理系统通讯协议设计

主控板卡与所有子板卡之间通讯协议采用自定义指令协议实现各板卡之间指令通讯和存储板卡上记录数据的下载。

3.1 电气接口设计

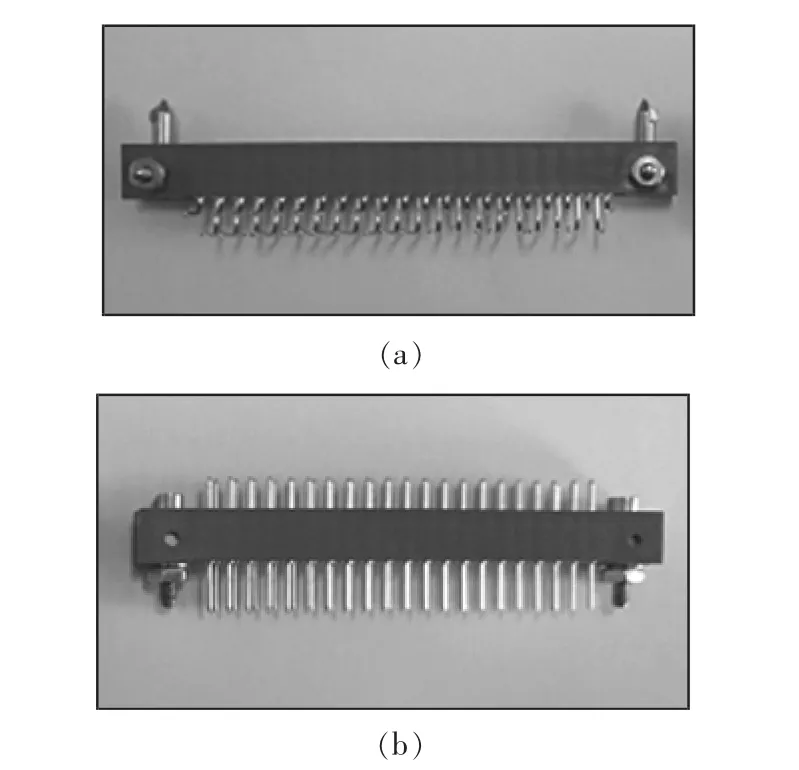

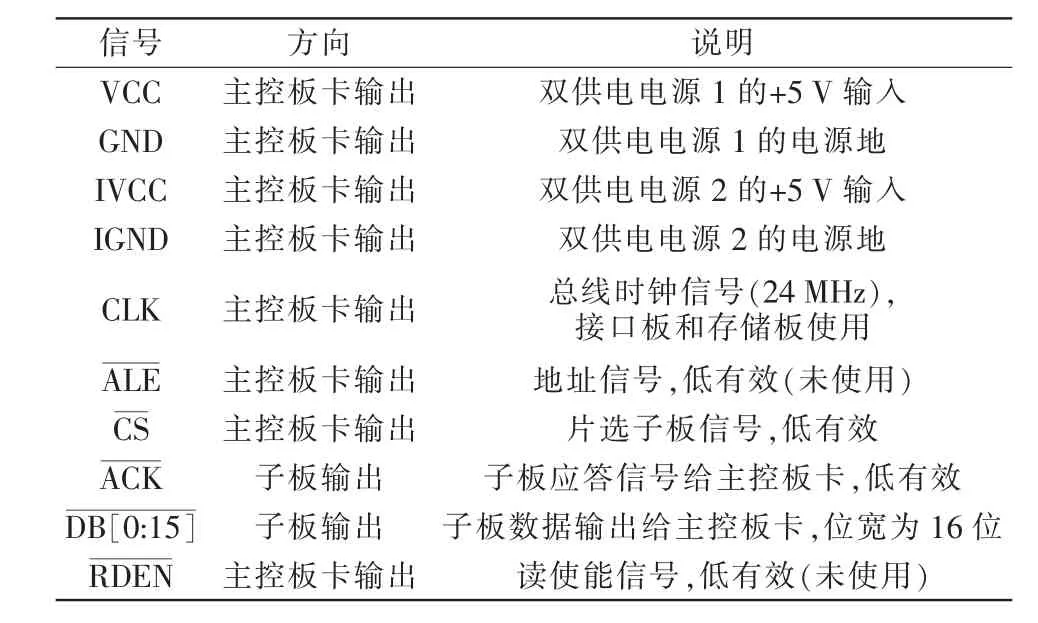

为满足机载环境要求,主控板卡与子板的连接器件采用J27A-41ZJXⅡBC/BW-0.8航天级接插件。该接插件具有高可靠性和高速传输的特点,产品示意如图6所示。这一系列的电路连接器可用于电子设备、计算机内部印制板之间、印制板与电缆之间、电缆与电缆之间的电路连接。具有插拔力低、接触可靠性高、支持热插拔、使用寿命长、耐用等特点。J27A-41TKⅡBW-0.8连接器部分引脚定义信号描述如表1所示。

图6 接插件产品示意Fig.6 Connector product diagram

表1 部分引脚定义信号描述Tab.1 Part of the pin definition of the signal description

3.2 主控板卡与子板卡之间指令通讯

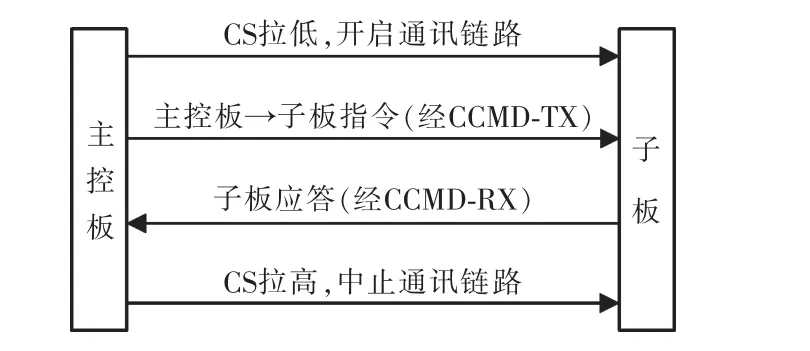

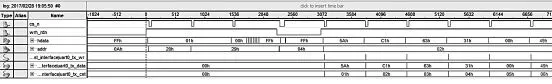

主控板卡与子板之间进行指令传输时,主控板卡作为从站子板作为主站。完成主控板卡与子板卡间指令通讯和存储数据的高速上传。通讯模式为在CS片选信号下的双向对等方式传输。传输过程如图7所示。

图7 主控板卡与子板间指令传输过程示意Fig.7 Schematic diagram of the instruction transmission between the main control board and the sub board

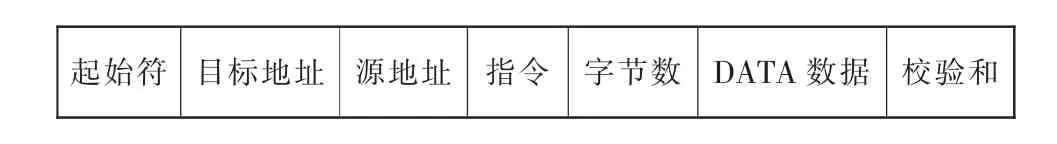

指令协议的具体格式为

起始符 目标地址 源地址 指令 字节数 DATA数据 校验和

目标地址和源地址定义方式比较随机,与各板卡地址相对应即可。字节数表示要发送的数据字节数,范围为0x00~0xFF。数据指需要发送的数据,该数据大小为字节数所规定的值。校验即为前面所有数据(START至DATA)异或得到的数值,然后需要将该数值MSB位清零,使其满足0~7F的要求。

对于各子板而言,RS422指令的有效性需要配合子板接口上的CS片选信号一起使用。在默认情况下,CS片选信号选通1553B接口子板。当有指令需要向其它子板发布时,先用CS片选信号选通指定的子板然后才可以进行通讯。发布指令的通讯任务完成后CS片选信号回归默认状态,仍然选通1553B总线子板。

3.3 主控板卡与子板间数据传输通讯协议

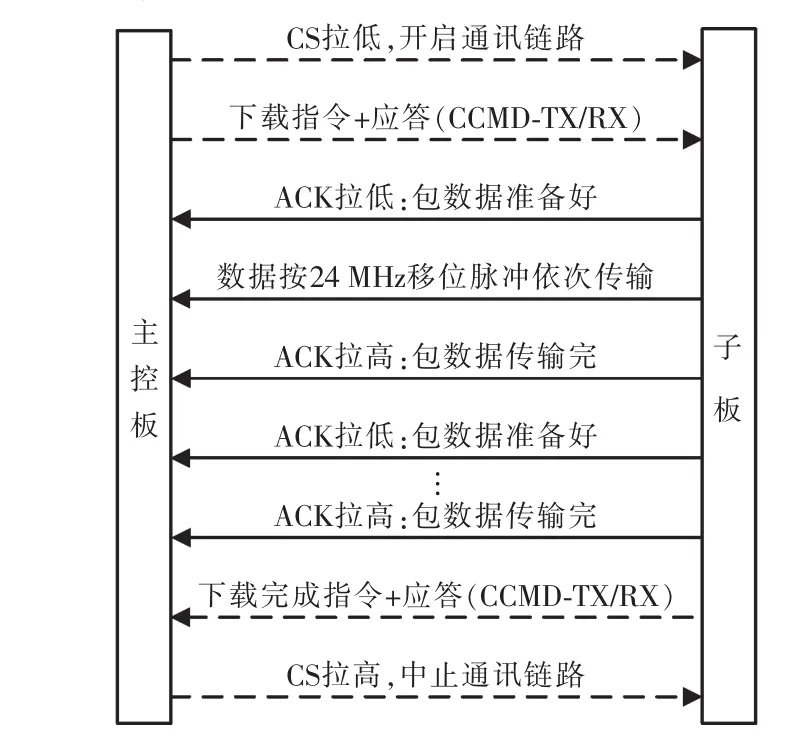

主控板卡与子板之间数据传输的完整过程如图8所示。

图8 主控板卡与子板数据传输过程示意Fig.8 Schematic diagram of the main control board and the sub board data transmission

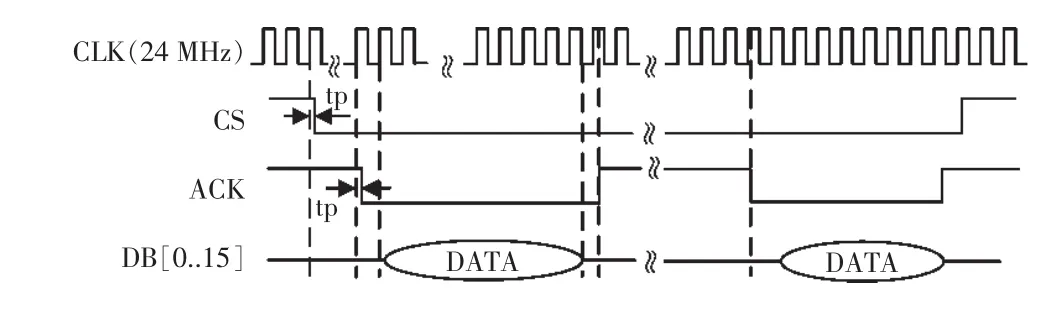

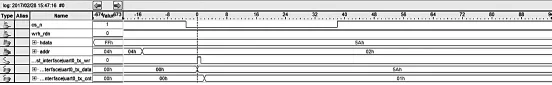

CS、ACK 及 DB[0:15]的变动均与 CLK 时钟脉冲的上升沿同步,CS电平变化由主控板卡进行控制。ACK 与 DB[0:15]变化由子板进行控制,在 ACK拉低的下一个CLK时钟移位脉冲上升沿开始数据传输。在DB[0:15]总线的DATA传输完毕后的下一个CLK时钟移位脉冲上升沿ACK拉高。对于各存储子板,数据上传时,将按帧头、帧计数、数据字、校验和、帧尾组成模式进行组帧。数据帧会连续发送,直至下载指令中所要求的数据全部传送完为止。指令相关的时序如图9所示。

3.4 1553B接口子板与主控板卡之间通讯协议设计

图9 指令时序图Fig.9 Instruction timing diagram

1553B接口板卡与主控板卡之间进行指令传输时,1553B板卡作为主站,主控板卡作为从站。

通讯模式为片选信号有效时双向对等传输方式,该操作只有当CS片选信号选定1553B接口子板时指令才有效,默认设置1553B接口板与存储板插在A号插槽、B号插槽,主控板卡与子板通讯空闲情况下CS信号默认选通1553B接口子板。1553B总线数据流控制下的指令包括自检、启动、停止3个指令,其传输过程如图10所示。

图10 1553B接口子板与主控板卡指令传输示意Fig.10 Schematic diagram of the 1553B interface sub board and main control board instruction transmission

4 时序仿真

STM32控制逻辑通过配置和读取FPGA内部相关的寄存器对目标子板的RS422指令数据包的转发和接收目标子板的RS422指令应答数据包,实现与子板的指令通讯以及双控制模式功能。

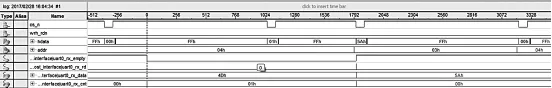

地面计算机发送 “自检”指令后,系统进入1553B数据流控制模式的在线仿真图,如图11所示,图中主控板卡STM32首先读取到1553B接口子板发送的数据包的起始符5A,接着等待接收RS422指令数据包的下一个数据字。

图11 1553B数据流控制模式在线仿真图Fig.11 1553B data flow control mode online simulation diagram

上位机或1553B数据流发送“自检”指令,以子板卡C1为例,主控板卡转发“自检”指令的在线仿真如图12所示。图12局部放大后,串口发送FIFO写操作的在线仿真如图13所示。

图12 主控板卡转发“自检”指令在线仿真图Fig.12 Online simulation diagram of “self-examination”instruction on the main control board

图13 串口发送FIFO写操作的在线仿真图Fig.13 Online simulation diagram of FIFO write operation by serial port

上位机或1553B数据流发送“自检”指令后,以子板C1的为例,主控板卡接收C1子板的应答指令的在线仿真如图14所示。图14局部放大后,串口接收FIFO写操作的在线仿真如图15所示。

图14 主控板卡接收C1子板应答指令在线仿真图Fig.14 Online simulation diagram of main control board receiving C1 sub board response instruction

图15 串口接收FIFO写操作在线仿真图Fig.15 Online simulation diagram of FIFO write operation by serial port

5 结语

整个控制系统所有通道记录模块实时并行记录,不需要经过主控板卡控制器干预,具有功能特定、指令精简、实时性强的优点。

板卡通讯采用的自定义指令协议是完全开放的,凡按照该指令设计的板卡均可兼容此记录仪,实现功能扩展。控制模式的多样性和灵活性使得记录仪适用范围更加广泛。若使用其他总线改变控制管理系统控制模式,只需更换1553B接口板卡即可实现。例如:实现CAN总线数据流控制模式,可按照1553B接口子板与主控板卡之间指令通讯协议设计“CAN接口板卡”,插入对应卡槽即可。

控制管理系统工作于复杂的机载环境,系统结构设计按照抗震动、抗冲击的规范;电路板符合电磁兼容性设计要求;主控板卡与子板接插件选用航空接插件,参照国家军用标准插件规范,满足传输速率,保证数据传输的可靠性。

[1]裴俊杰.基于FPGA的多路数据接收存储的设计与实现[D].太原:中北大学,2011.

[2]王欢,靳鸿,陈昌鑫,等.模块化和柔性化的机载数据记录仪设计[J].工程设计学报,2014,21(4):373-377.

[3]Qin G,Liu G,Feng H.Design and implementation of a solidstate flight data recorder using multichannel technique[C]//IntelligentControland Information Processing (ICICIP),2013 Fourth International Conference on,IEEE,2013:726-729.

[4]吴良.分布式试飞测试总线系统的硬件设计与实现[D].重庆:重庆大学,2008.

[5]刘九洲,杜国兴,盛文.基于CPCI总线的雷达便携式仪器测试系统设计[J].仪表技术,2013(1):4-6.

[6]祖东辉.大容量雷达数据存储与管理技术研究[D].成都:电子科技大学,2013.

[7]TakeshiSasada,Sato Ichikawa,MasashiShirakura.High-speed 200Gbytes data recorder utilizing the 512Mbits SDRAM and compact PCI bus[C]//22nd AIAA International Communications Satellite Systems Conference&Exhibit 2004(ICSSC).Monterey,California:AIAA,2004:185-189.

[8]刘东华,李秋娜.通用高速数据存储系统设计与实现[J].遥测遥控,2007,28(1):15-19.

[9]范晓星.高速大容量固态存储系统设计与实现[D].西安:西安电子科技大学,2014.

[10]任敏.基于FPGA的双通道的机载数据存储系统设计[D].太原:中北大学,2015.

[11]吴磊,郭超平,申世涛,等.基于CY7C68013与FPGA的便携式数据采集系统[J].计算机应用,2012,32(Z1):164-166.