SoC系统功耗评估方法*

杨瑞瑞,唐伟文

(成都三零嘉微电子有限公司,四川 成都 610041)

0 引 言

应用于便携式、手持设备、物联网等环境的低功耗或微功耗SoC芯片,对功耗指标的要求非常严格。如果芯片实际功耗消耗值不能满足能耗比指标要求,那么即使芯片功能没有问题,但由于功耗消耗过大也将无法进行推广应用。所以,SoC集成电路功耗控制,在低功耗芯片的设计中至关重要。

低功耗芯片设计过程中,在方案阶段采用低功耗架构、RTL代码设计时采用低功耗设计电路,在后端设计中采用低功耗的设计流程等,以保障芯片的能耗比满足设计需求。但是,如何确定采取低功耗策略的电路是否满足指标要求、是否可以进入下一步的设计流程是关键。因此,在每个阶段的设计中,通过功耗评估方法验证采用的低功耗策略是否满足要求至关重要。

1 功耗评估技术概述

本文针对设计过程中的功耗控制,提出在三个阶段进行功耗评估,分别是方案阶段功耗评估、RTL代码阶段功耗评估以及流片前签核阶段的功耗评估。在每个阶段进行的功耗评估方法不同,得到的准确度将不同,达到的目的也不同。表1介绍了在芯片全流程设计过程中,在不同设计阶段进行的功耗评估。

图1 低功耗芯片设计流程

方案阶段进行的功耗评估,主要使用公式计算的方法。此阶段评估值误差较大,但能够辅助确定方案设计的合理性,验证所选择工艺平台的正确性,与设计结果不产生较大差异。

RTL阶段的功耗评估,是在电路功能设计完成后,通过专业的功耗评估工具,加入合理的约束,通过不同应用模式激励产生的波形,得到比较准确的逻辑门翻转率,从而对不同应用模式的功耗进行评估。此阶段的评估准确率可达70%。

后端物理版图设计完成后签核阶段的功耗评估,是流片前的最后一次功耗评估。由于后端版图设计完成后,用于功耗评估的门电路是芯片实际物理门电路,因此准确率可达85%~90%。评估方法是读入后仿网表和SDF反标文件,产生不同应用模式激励下的后仿波形,得到准确的物理门电路翻转率,通过专业工具计算得到功耗值。下面对三个阶段的功耗评估方法分别做详细介绍。

2 方案阶段功耗评估方法

首先要分析功耗的来源和组成部分。在一个完整的SoC设计电路中,功耗从顶层划分主要有三部分:

其中,Pdigital是芯片中使用的模拟IP在工作时消耗的功耗,模拟部分的功耗值通过查询模拟IP的数据手册获得,数据手册会详细介绍模拟IP工作在不同模式或者不同配置下的功耗值。Pdigital是芯片中数字标准单元部分的功耗消耗值,工作电压为内核电压。Ppad是芯片管脚在工作时消耗的功耗值,当芯片与外部通信时,芯片的管脚会进行翻转产生功耗。当然,如果芯片工作的场景只有内部模块在工作,接口不进行数据传输,那么Ppad只产生较小的漏电功耗。

按照理论公式计算[1-2]:

其中f是系统工作频率;A是跳变因子,即整个电路的平均翻转比例;C是门电路的总电容;V是供电电压;τ是电平信号上升/下降的时间;Ileak是漏电电流;Pswitch是跳变功耗,是器件在工作过程中对电容充放电形成的;Pshortcircuit是短路功耗,是器件在工作时由电源到地形成的通路造成的;Pleakage是漏电流功耗,也叫静态功耗,是由亚阈值电流和反向偏压电流造成的。

假设已经选定某一工艺平台,如果使用式(2),其中门电路的电容C以及电平信号上升/下降的时间τ,基本无法填入合适的值。因此,本文使用其他方法完成内核功耗的评估。在本阶段进行功耗评估计算,需要已知芯片设计的电路门数(大部分数字IP具备继承性,可以获得电路的门数,文中使用的计算单位为最小二输入与非门NAND2)、工作模式频率以及芯片管脚在工作模式时的使用情况。查询工艺库里面最小二输入与非门NAND2短路功耗表,结合工作频率进行如下计算:

其中k1表示电路工作时的翻转率,即由于翻转产生短路功耗门电路的比例,根据经验,值为1/20;N表示电路的等效门数;f表示电路的工作频率;Pshortcircuit_nand2表示工艺库中最小二输入与非门NAND2的短路功耗,可以通过查工艺库获得;k2表示翻转功耗与短路功耗比,根据经验,值为(0.8~1);Pleakage_nand2表示工艺库中最小二输入与非门NAND2的漏电功耗,可以通过查工艺库获得。

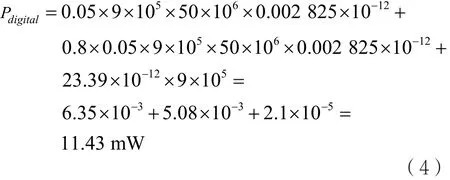

以SMIC55nm LL工艺为例,门电路约90万逻辑门,工作频率为50 MHz。查询工艺库中NAND2的短路功耗为0.002 825 pW[3],漏电功耗为23.39 pW[3],代入公式得到内核工作时的功耗值:

查询工艺库中使用管脚库的短路功耗表,结合工作频率,评估芯片管脚 PAD 的工作功耗:

其中k1表示PAD工作时的翻转率,根据经验,值为1/20;N表示工作PAD的个数;f表示PAD工作的时钟频率;Pshortcircuit_pad表示工艺库中PAD工作时产生的短路功耗,可以通过查工艺库获得;C为等效电容,根据经验,值为20 pF;V为PAD工作电压,一般为3.3 V/2.5 V;Pleakage_pad为PAD的漏电功耗,可以通过查工艺库获得。

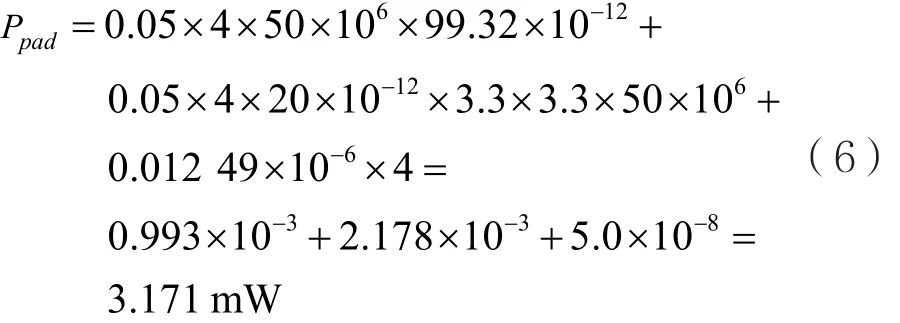

以SMIC55nm LL工艺为例,4个PB8的管脚工作,工作频率为50 MHz。查询工艺库中PB8的短路功耗为99.32 pW[3],漏电功耗是0.012 49 μW[3],代入公式计算得到管脚PAD工作时的功耗值:

最后,通过查询数据手册,获得模拟IP工作时的功耗值,将三部分相加,获得总的Ptotal功耗值。本阶段的功耗评估通过公式计算以及引入一些经验值,方法简单,准确率较低,主要目的是确认低功耗芯片方案阶段所使用的工艺、电路规模、以及工作频率的合理性,为后期设计打下基础。

3 RTL代码阶段功耗评估方法

代码阶段的功耗评估,是在RTL代码设计完成后,对应用场景下功耗消耗的评估,准确率比方案阶段高。如果在本阶段评估数据与指标存在非常大差距,可以及时更改设计,造成较小的迭代。

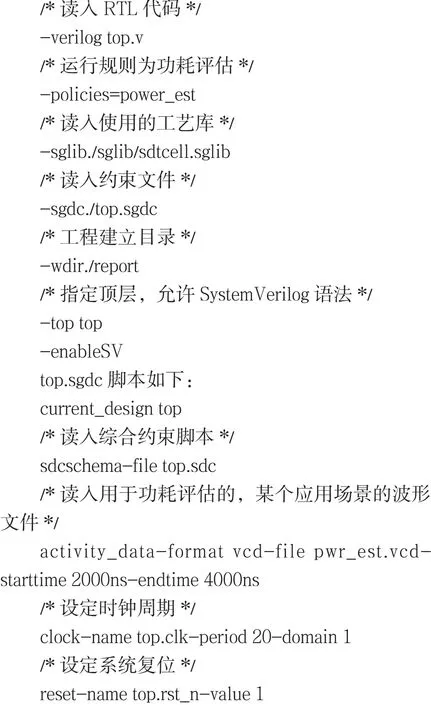

使用的评估工具是Spyglass。在Spyglass工具中对代码进行综合,工具将RTL代码综合成门电路网表,然后读入应用场景激励下生成的VCD或者FSDB波形,对门电路进行反标,获得门电路在应用场景下的翻转率,读入工艺库进行计算,得到功耗消耗值。

使用Spyglass进行功耗评估的基本语法为[4]:

本阶段的功耗评估值准确率约为70%。如果评估结果能够满足指标要求,设计进入下一步后端布局布线生成物理GDS版图。

4 签核阶段功耗评估方法

签核阶段功耗评估是最接近真实功耗消耗的数据,因为此时的门电路核线延时均是物理实际电路,得到的评估值也是最准确的。本阶段功耗评估数据准确率可达85%~90%。

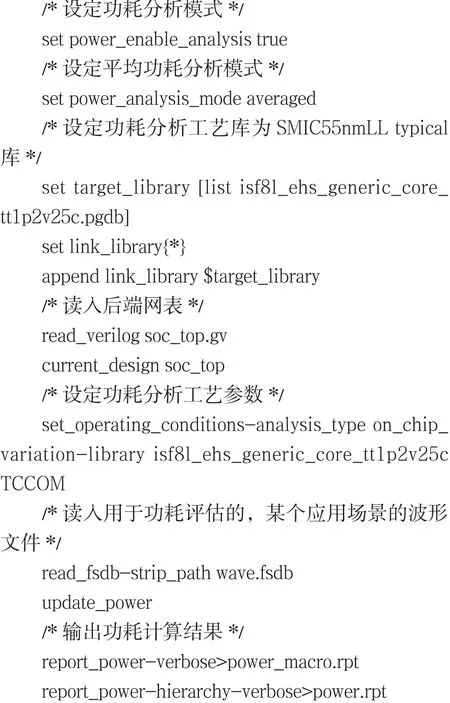

本阶段采用PTPX工具进行功耗分析,方法是将完成后端布局布线、时序收敛后的版图提取出后仿网表和反标SDF文件,应用后仿环境产生不同应用场景激励下的VCD或者FSDB波形。在PTPX工具中读入已产生的波形,对物理门电路进行映射,获得门电路在应用场景下的真实翻转率,读入工艺库进行计算,得到功耗消耗值。

下面以SMIC55nm LL工艺为例,介绍使用PTPX工具评估典型环境下功耗消耗的基本语法[5]:

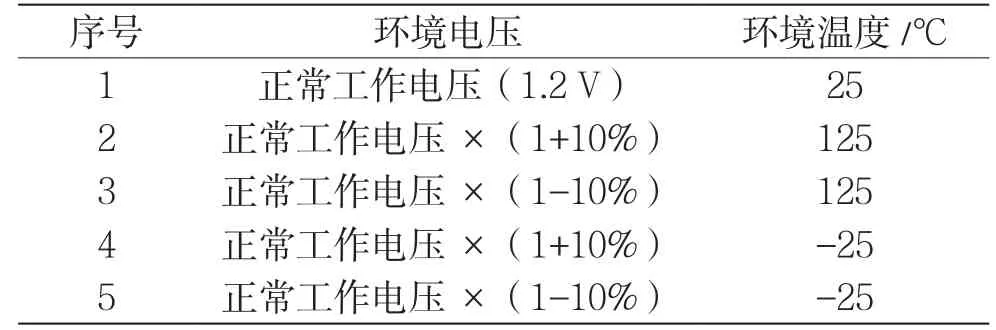

通过读入不同环境参数的工艺库,可以计算出不同环境下的功耗结果,如表1所示。

经过工具计算不同测试环境下的功耗值,若达到预期目标,可以进行芯片流片。

表1 测试环境电压和温度

5 结 语

在低功耗SoC芯片设计过程中,通过以上三个阶段的功耗评估,不仅可以保证超低功耗芯片设计的成功,而且能够保证芯片设计流程的顺畅,无需巨大的芯片设计迭代,保障了芯片流片的成功。