一种基于E1通信的高可靠数字接口模块设计*

,,,

(许继集团有限公司,许昌 461000)

引 言

随着特高压交直流电网建设的不断推进,基于传统交流系统的控制技术和管控措施已难以适应特高压交直流电网运行实践的要求,电网的安全可靠运行面临巨大挑战,亟待建设精准负荷系统保证直流系统稳定。通信模块作为精准负荷控制系统的重要组成部分,对系统保护的可靠性、稳定性、实时性发挥着至关重要的作用。

SDH(Synchronous Digital Hierarchy,同步数字系统)是精准负荷控制系统所采用的通信传输网络,也是电力系统常用的一种通信传输网络,但是,SDH传输网络的最小接口速率是STM-1(155 Mb/s),一个STM-1信号可以解析出63个E1接口信号。E1接口是速率为2.048 Mb/s的标准数字接口,俗称2M口,采用HDB3编码传输数据,是中国和欧洲普通采用的通信接口。而精准负荷控制终端装置的通信传输接口大多是百兆以太网,控制终端装置无法直接接入SDH网络,需要通信接口转换模块完成百兆以太网与E1的接口转换。因此设计一种高可靠的以太网转多路E1的数字接口模块,为精准负荷控制系统提供稳定、可靠、安全的通信支撑,具有重要意义。

本文提出了一种基于E1通信的数字接口模块实现方案,采用目前先进的E1接口芯片及不断成熟的EMC设计方案,应用FPGA可扩展性强、灵活方便的优点,通过硬件编码技术在FPGA内部设计功能模块,实现百兆光以太网转换成多路E1接口的高可靠性设计。

1 系统总体方案设计

图1是系统总体硬件实现方案。百兆以太网差分信号通过PHY芯片KSZ8041FTLI转换成RMII接口,然后由FPGA和E1接口芯片完成百兆以太网到2.048 Mb/s E1信号的信号传输、协议转换和数据流码型转换,然后依次经变压器、共模电感和EMC防护电路完成电平变换、信号隔离、滤波整形和抗干扰,最终转换为8路E1接口。

图1 系统硬件整体框图

2 系统硬件及原理

系统硬件分为电源供电单元、时钟管理单元、百兆以太网接口单元、E1接口单元、FPGA控制单元和EMC防护单元[2]。

2.1 电源供电单元

系统支持DC/AC 220 V电源输入,采用电源模块把输入电压转换为5 V,然后再通过多通道DC-DC电源转换芯片把5 V转换成3.3 V、1.8 V和1.2 V,其中1.2 V为FPGA的内核供电,1.8 V为E1接口芯片的数字内核部分供电,3.3 V为其他电路单元提供电源。

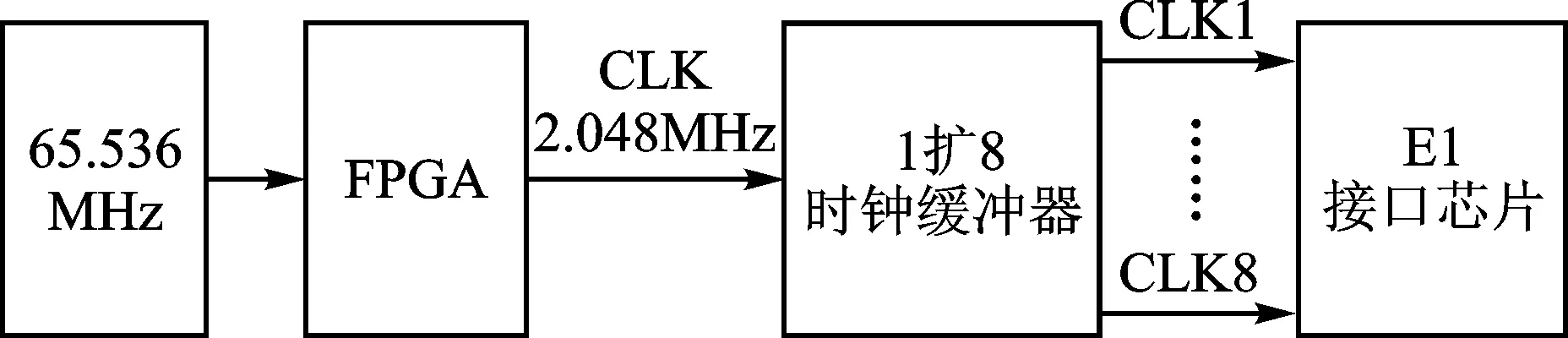

2.2 时钟管理单元

本系统选用了50 MHz和65.536 MHz两种晶振为系统提供所需的工作时钟。其中,50 MHz时钟为FPGA提供基准时钟,并为百兆以太网的RMII接口提供时钟参考;65.536 MHz时钟为整个系统提供时钟参考,同时由FPGA内部的时钟管理单元分频产生一个2.048 MHz的时钟信号,使用单输入、8输出零延时的时钟缓冲芯片552G-02ILN,生成8路完全同步的时钟信号,为E1接口芯片的每个E1通道提供时钟输入,如图2所示。这种通过FPGA软件为E1接口芯片提供输入时钟的方法,减少了晶振的使用数量,简化了E1接口芯片的外围电路,同时可以优化由晶振引发的辐射发射等问题。PCB布局布线时,8路时钟信号线应尽量短且尽可能等长。

图2 FPGA生成多路同步时钟的原理框图

2.3 百兆光以太网接口单元

百兆光以太网通过物理层收发器芯片KSZ8041FTLI转换为RMII接口[3],与 FPGA的扩展MAC互连。以太网MAC层协议由FPGA内部逻辑实现,并封装在MAC软核中,可以根据需要灵活使用该MAC软核[4]。扩展MAC工作模式配置为全双工、百兆、光纤模式,禁能自协商。在RMII接口信号线的源端串联33 Ω电阻,用来减少高速信号的过冲。接口框图如图3所示。

图3 百兆光以太网接口框图

2.4 E1接口单元

E1接口芯片采用EXAR的XRT83VSH38,该芯片提供8通道的E1/T1/J1接口,可完成HDB3码的编码、解码、码型变换,芯片还具有去抖、本地及远程loopback诊断、掉电保护、过压过流保护和线路性能监视功能。每一路的发送、接收缓冲器都有32/64位的FIFO,用于消除数据的抖动;芯片提供标准的SPI串行接口和并行总线接口,以便于微处理器进行参数配置、控制和状态监视。芯片的8路发送、接收通道内部均集成了匹配电阻,可通过对寄存器TERSEL[1:0]编程配置合适阻值的匹配电阻。数字内核部分使用1.8 V电源供电,I/O和模拟内核采用3.3 V电源供电,封装为225引脚的BAG封装。

E1芯片接口侧电路如图4所示,芯片的发送、接收引脚和对外接口之间使用变压器进行隔离,发送通道使用了1:2的升压变压器,以满足ITU-G.703标准中规定的E1输出脉冲的电压幅值要求;接收通道使用了1:1的变压器。E1接口芯片内部是数模混合电路,并且发送时钟和接收时钟均有8路,这些将会增加对外的噪声干扰[6]。为抑制芯片、时钟对外的传导发射和辐射发射,变压器选用了集成共模电感的变压器。

图4 E1芯片接口侧电路图

此外,为优化阻抗不连续引起的回波损耗,在XRT83VSH38芯片的RTIP和RRING引脚之间并联精密电阻R7来调整输入阻抗,总输入阻抗为片内输入阻抗和外部电阻的并联值。为滤除发送信号中的直流分量,在发送端串联了0.68 μF的电容C2。

2.5 FPGA控制单元

E1接口芯片XRT83VSH38和微处理器的接口支持两种模式:SPI串行接口和标准并行接口。本文的微处理器选用的是Xilinx公司的Spartan-6系列FPGA芯片XC6SLX9-2FTG256I,为节省引脚使用了SPI串行接口,本系统中数据的接收和发送通过FPGA进行处理,XRT83VSH38和FPGA的接口包括发送逻辑、接收逻辑、控制逻辑和串行SPI接口,如图5所示。

图5 E1芯片FPGA侧接口电路图

2.6 EMC防护单元

电力系统精准负荷控制装置运行的现场环境往往比较恶劣,而且设备数量多、分布距离远,容易遭受不可预测的干扰(如雷击、脉冲群干扰、射频干扰等),将会对通信带来不利影响[5]。因此提高E1接口电路的抗干扰性能,对于确保精准负荷控制系统乃至整个电网的安全稳定运行,都具有重要意义。

本系统中E1接口电路的浪涌、静电、快速瞬变、介质强度等EMC防护电路采用了两级防护措施:主防护和次级防护[6]。对外接口侧采用过压、过流保护器件进行主保护,可将大部分瞬间能量从系统转移,芯片电路侧使用TVS管进行次级防护,进一步消除由变压器耦合到数字电路部分的残留干扰[6]。

主防护的具体实现如图6所示,当浪涌等瞬变能量施加于保护电路时,固体放电管P0080SCMCL将会雪崩击穿,提供低阻抗的接地路径将大部分瞬变能量转移到大地[7]。由于浪涌的电压和电流都较高,还必须通过限流来保护后级电路,TBU是由MOSFET半导体技术制成的主动高速过流保护器件,具有预设电流限值和耐高压能力,响应时间为纳秒级。当过流发生时,可快速从低阻状态切换到极高阻状态,将被保护电路与浪涌断开,并可在瞬变消失后自动重置到低阻状态,让系统恢复正常工作。在正常工作时,TBU低阻抗,不影响电路的正常工作性能。

图6 E1接口一级EMC防护电路

根据《GBT 14598.3-2006度量继电器绝缘配合及试验要求》,E1的对外端口和220 V电源端口之间需满足规定的绝缘电压和介质强度要求。上述标准规定,220 V电源端口和E1对外端口之间要满足交流试验电压2 000 V、E1对外端口和机壳地之间要满足交流500 V的耐压要求,本系统通过在固体放电管和大地之间串联安规电容CT1和压敏电阻VR1的方法来实现电荷的泄放和电压的钳位。

次级防护主要用来保护变压器另一侧的E1接口芯片等数字部分,防止经过变压器耦合过来的残留瞬变电压和电流损坏变压器后级的电路。如图7所示,在E1接口芯片的发送、接收引脚和数字地之间并联TVS,将残存干扰通过TVS管传导到数字地。本系统选用了Littlefuse的双向TVS管SP4021-01FTG-C,其反向截止电压为5 V,结电容极低仅2.5 pF,对发送、接收信号几乎没有影响。

图7 E1接口二级EMC防护电路

PCB元件布局时,线路侧主防护的过压保护器件、安规电容和压敏电阻应紧靠对外端口放置,导线应尽可能短,以缩短瞬变能量传导至大地的路径。次级防护的TVS管紧靠变压器放置,接收差分对(RTIP0、RRING0)和发送差分对(TTIP0、TRING0)旁路到TVS的分支走线要尽可能得短,缩短对地的放电路径,同时减少导线的寄生电容。

3 FPGA设计

3.1 E1接口的数据发送

E1接口的数据发送主要包含三个部分:以太网接收、数据存储和串行数据发送。

FPGA与PHY芯片KSZ8041FTLI使用RMII模式交互数据,数据收发都以本地50 MHz晶振上升沿为基准。FPGA实时检测KSZ8041FTLI数据接收端口RXD[1:0],以前导码和约定的目的MAC、源MAC为依据判断是否有以太网报文,如果检测到有效报文,则按照约定的协议将报文中包含的8个E1通道的发送数据分别存储到8个缓存区中,缓存区通过FPGA内部BlockRam实现。同时8个E1通道发送模块实时检测以太网接收完成标志位,如果检测到有数据接收完成即启动串行发送,串行发送模块以Tclk上升沿为基准(也可以通过E1接口芯片引脚配置为下降沿),将并行数据逐位传输到E1接口芯片的TDA端口,同时按照约定的协议完成HDLC协议编码。

考虑到以太网接收和E1通道发送速率不一致,数据存储模块采用多级缓存模式。每个E1通道都设有一个多级缓存区和相应状态寄存器,当通过以太网接收到对应通道的有效数据时,状态寄存器加1,当串行发送模块完成发送时,状态寄存器减1,状态寄存器为0时,为空闲态,状态寄存器等于缓存区级数时,视为溢出,暂停以太网报文的接收。

3.2 E1接口的数据接收

E1接口的数据接收也包含三部分:E1接口数据接收、数据存储和以太网数据发送。

FPGA采用同步串行模式接收E1接口芯片的数据,以接收时钟Rclk的上升沿为基准,实时检测E1芯片RDA端口数据。按照约定的HDLC协议,FPGA实时检测帧头帧尾“0111 1110”,非“0111 1110“数据为有效数据。串行接收模块将接收的串行数据以字节为单位存入对应通道的接收缓存区中,在进行串并转换的同时完成HDLC协议解码。以太网发送模块实时检测8个通道的数据缓存区是否有待接收的数据,如果有,则按约定的顺序依次从8个接收缓存区中读取数据,并进行以太网包组帧,将以太网报文通过RMII接口发送出去。

由于E1接口数据接收速率仅为2.048 Mb/s,共有8个E1通道,即E1接口侧数据接收带宽最大为16.384 Mb/s,而以太网发送模块为100 Mb/s模式,足以满足数据上传的要求,E1接口数据的接收缓存区通过乒乓结构实现,不使用多级缓存。

4 系统测试和分析

4.1 功能测试

将本设计的硬件板卡安装到机箱,其百兆光以太网与精准负荷控制系统的稳控装置互连,E1接口采用自环方式通信,通过装置调试分析器软件监测数据的发送和接收,经过长时间的监测,通信可靠、稳定,无通信中断及丢帧现象。

用示波器测量E1发送端,波形如图8所示。ITU-G.703标准中规定:平衡传输(120 Ω双绞线传输)E1接口的标称峰值电压为3 V±0.3 V[6],本设计中E1接口为平衡传输方式,实测波形的峰值电压为3 V,完全符合标准要求。此外,波形的脉冲宽度、电压值、上升沿、下降沿和通信速率均符合ITU-G.703标准的规定(图9为2 048 kb/s接口脉冲波形模板)。

图8 E1发送端(TTIP、TRING)波形图

图9 ITU-G.703 2048 kb/s接口脉冲波形模板

4.2 电磁兼容测试

对本系统进行浪涌抗扰度4级、静电放电抗扰度4级、电快速瞬变扰度A级、传导和辐射发射限值3级以及绝缘、介质强度、高低温测试[8],实验过程中通信稳定可靠,误码率在10-5以内。

结 语